计算机组成原理实验.docx

《计算机组成原理实验.docx》由会员分享,可在线阅读,更多相关《计算机组成原理实验.docx(33页珍藏版)》请在冰豆网上搜索。

计算机组成原理实验

实验一算术逻辑运算单元实验

一.实验目的

1、掌握简单运算器的数据传输方式

2、掌握74LS181的功能和应用

二.实验要求

完成不带进位位算术、逻辑运算实验。

按照实验步骤完成实验项目,了解算术逻辑运算单元的运行过程。

三.实验说明

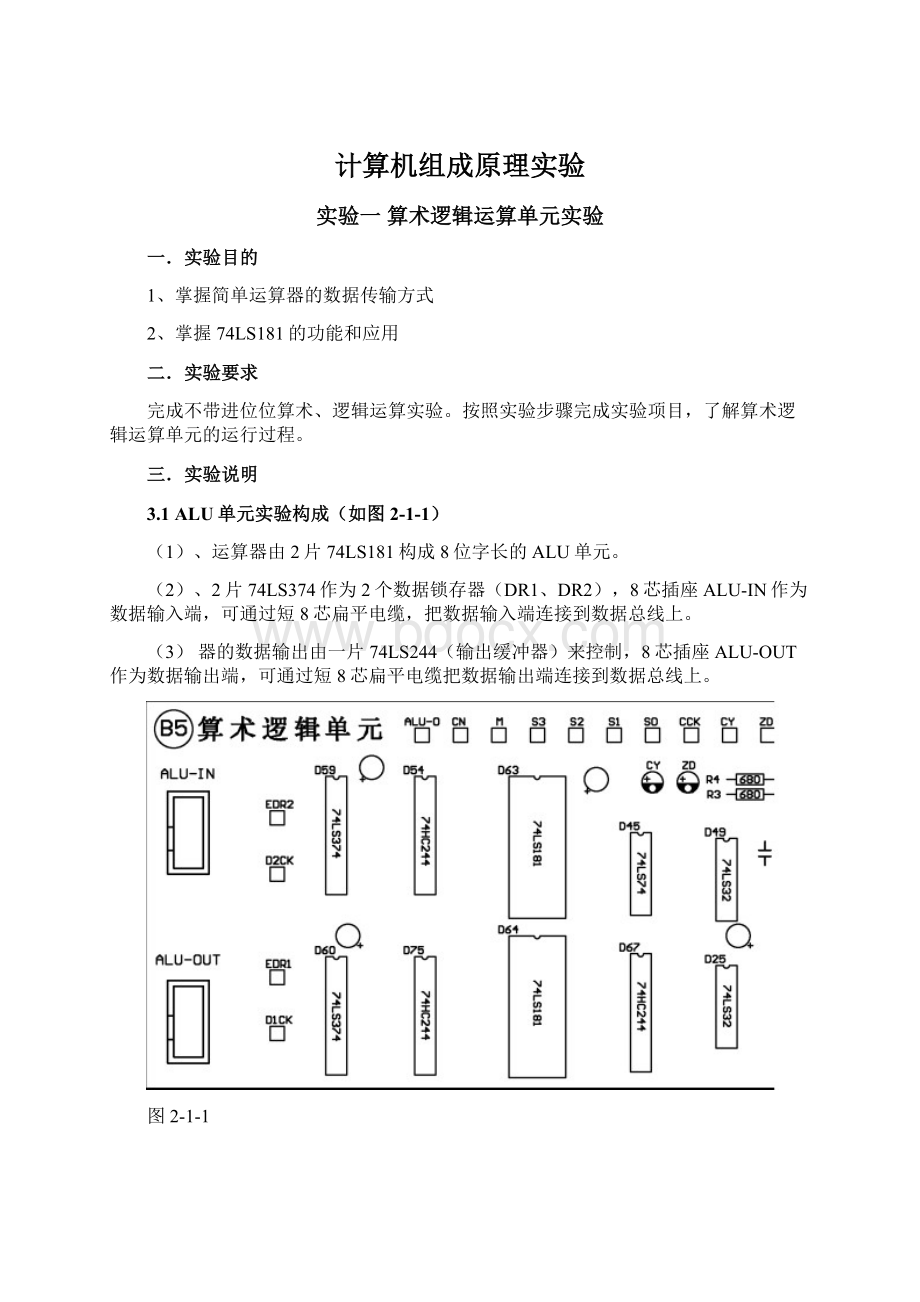

3.1ALU单元实验构成(如图2-1-1)

(1)、运算器由2片74LS181构成8位字长的ALU单元。

(2)、2片74LS374作为2个数据锁存器(DR1、DR2),8芯插座ALU-IN作为数据输入端,可通过短8芯扁平电缆,把数据输入端连接到数据总线上。

(3)器的数据输出由一片74LS244(输出缓冲器)来控制,8芯插座ALU-OUT作为数据输出端,可通过短8芯扁平电缆把数据输出端连接到数据总线上。

图2-1-1

图2-1-2

3.2ALU单元的工作原理(如图2-1-2)

数据输入锁存器DR1的EDR1为低电平,并且D1CK有上升沿时,把来自数据总线的数据打入锁存器DR1。

同样使EDR2为低电平、D2CK有上升沿时把数据总线上的数据打入数据锁存器DR2。

算术逻辑运算单元的核心是由2片74LS181组成,它可以进行2个8位二进制数的算术逻辑运算,74LS181的各种工作方式可通过设置其控制信号来实现(S0、S1、S2、S3、M、CN)。

当实验者正确设置了74LS181的各个控制信号,74LS181会运算数据锁存器DR1、DR2内的数据。

由于DR1、DR2已经把数据锁存,只要74LS181的控制信号不变,那么74LS181的输出数据也不会发生改变。

输出缓冲器采用74LS244,当控制信号ALU-O为低电平时,74LS244导通,把74LS181的运算结果输出到数据总线;当ALU-O为高电平时,74LS244的输出为高阻。

3.3控制信号说明

信号名称

作用

有效电平

EDR1

选通DR1寄存器

低电平有效

EDR2

选通DR2寄存器

低电平有效

DR1CK

DR1寄存器工作脉冲

上升沿有效

DR2CK

DR2寄存器工作脉冲

上升沿有效

S0~S3

74LS181工作方式选择

M

选择逻辑或算术运算

CN

有无进位输入

CCK

进位寄存器的工作脉冲

上升沿有效

ALU-O

74LS181计算结果输出至总线

低电平有效

四.实验步骤

实验1、不带进位位逻辑或运算实验

●把ALU-IN(8芯的盒型插座)与CPT-B板上的二进制开关单元中J01插座相连(对应二进制开关H16~H23),把ALU-OUT(8芯的盒型插座)与数据总线上的DJ02相连。

●把D1CK和D2CK用连线连到脉冲单元的PLS1上,把EDR1、EDR2、ALU-O、S0、S1、S2、S3、CN、M接入二进制开关(请按下表接线)。

信号定义

接入开关位号

D1CK

PLS1孔

D2CK

PLS1孔

EDR1

H8孔

EDR2

H7孔

ALU-O

H6孔

CN

H5孔

M

H4孔

S3

H3孔

S2

H2孔

S1

H1孔

S0

H0孔

●按启停单元中的运行按钮,使实验平台处于运行状态。

●二进制开关H16~H23作为数据输入,置33H(对应开关如下表)。

H23

H22

H21

H20

H19

H18

H17

H16

数据总线值

D7

D6

D5

D4

D3

D2

D1

D0

8位数据

0

0

1

1

0

0

1

1

33H

置各控制信号如下:

H8

H7

H6

H5

H4

H3

H2

H1

H0

EDR1

EDR2

ALU-O

CN

M

S3

S2

S1

S0

0

1

0

1

1

1

1

1

0

●按脉冲单元中的PLS1脉冲按键,在D1CK上产生一个上升沿,把33H打入DR1数据锁存器,通过逻辑笔或示波器来测量确定DR1寄存器(74LS374)的输出端,检验数据是否进入DR1中。

●二进制开关H16~H23作为数据输入,置55H(对应开关如下表)。

H23

H22

H21

H20

H19

H18

H17

H16

数据总线值

D7

D6

D5

D4

D3

D2

D1

D0

8位数据

0

1

0

1

0

1

0

1

55H

置各控制信号如下:

H8

H7

H6

H5

H4

H3

H2

H1

H0

EDR1

EDR2

ALU-O

CN

M

S3

S2

S1

S0

1

0

0

1

1

1

1

1

0

●按脉冲单元中的PLS1脉冲按键,在D2CK上产生一个上升沿的脉冲,把55H打入DR2数据锁存器。

●经过74LS181的计算,把运算结果(F=A或B)输出到数据总线上,数据总线上的LED显示灯IDB0~IDB7应该显示为77H。

实验2、不带进位位加法运算实验

●二进制开关H16~H23作为数据输入,置33H(对应开关如下表)。

H23

H22

H21

H20

H19

H18

H17

H16

数据总线值

D7

D6

D5

D4

D3

D2

D1

D0

8位数据

0

0

1

1

0

0

1

1

33H

置各控制信号如下:

H8

H7

H6

H5

H4

H3

H2

H1

H0

EDR1

EDR2

ALU-O

CN

M

S3

S2

S1

S0

0

1

0

1

0

1

0

0

1

●按脉冲单元中的PLS1脉冲按键,在D1CK上产生一个上升沿,把33H打入DR1数据锁存器,通过逻辑笔或示波器来测量确定DR1寄存器(74LS374)的输出端,检验数据是否进入DR1中。

●二进制开关H16~H23作为数据输入,置55H(对应开关如下表)。

H23

H22

H21

H20

H19

H18

H17

H16

数据总线值

D7

D6

D5

D4

D3

D2

D1

D0

8位数据

0

1

0

1

0

1

0

1

55H

置各控制信号如下:

H8

H7

H6

H5

H4

H3

H2

H1

H0

EDR1

EDR2

ALU-O

CN

M

S3

S2

S1

S0

1

0

0

1

0

1

0

0

1

●按脉冲单元中的PLS1脉冲按键,在D2CK上产生一个上升沿,把55H打入DR2数据锁存器。

●经过74LS181的计算,把运算结果(F=A加B)输出到数据总线上,数据总线上的LED显示灯IDB0~IDB7应该显示为88H。

五.实验思考

验证74LS181的算术运算和逻辑运算,在保持DR1=65H、DR2=A7H时,改变运算器的功能设置,观察运算器的输出,填写以下表格来进行分析和比较。

DR1

DR2

S3

S2

S1

S0

M=0(算术运算)

M=1

逻辑运算

CN=1

CN=0

65

A7

0

0

0

0

F=

F=

F=

65

A7

0

0

0

1

F=

F=

F=

65

A7

0

0

1

0

F=

F=

F=

65

A7

0

0

1

1

F=

F=

F=

65

A7

0

1

0

0

F=

F=

F=

65

A7

0

1

0

1

F=

F=

F=

65

A7

0

1

1

0

F=

F=

F=

65

A7

0

1

1

1

F=

F=

F=

65

A7

1

0

0

0

F=

F=

F=

65

A7

1

0

0

1

F=

F=

F=

65

A7

1

0

1

0

F=

F=

F=

65

A7

1

0

1

1

F=

F=

F=

65

A7

1

1

0

0

F=

F=

F=

65

A7

1

1

0

1

F=

F=

F=

65

A7

1

1

1

0

F=

F=

F=

65

A7

1

1

1

1

F=

F=

F=

实验二通用寄存器判零实验

一.实验目的

1、了解通用寄存器的组成和硬件电路

2、利用通用寄存器实现数据的置数、左移、右移等功能

二.实验要求

按照实验步骤完成实验项目,实现通用寄存器移位操作。

了解通用寄存器单元的工作原理运用。

三.实验说明

3.1寄存器实验构成:

(如图2-2-1)

1、通用寄存器由2片GAL构成8位字长的寄存器单元。

8芯插座RA-IN作为数据输入端,可通过短8芯扁平电缆,把数据输入端连接到数据总线上。

2、数据输出由一片74LS244(输出缓冲器)来控制。

用8芯插座RA-OUT作为数据输出端,可通过短8芯扁平电缆,把数据输出端连接到数据总线。

3、判零和进位电路由1片GAL、1片7474和一些常规芯片组成,用2个LED(ZD、CY)发光管分别显示其状态。

图2-2-1

3.2通用寄存器单元的工作原理:

(图2-2-2)

通用寄存器单元的核心部件为2片GAL,它具有锁存、左移、右移、保存等功能。

各个功能都由X1、X2信号和工作脉冲RACK来决定。

当置ERA=0、X0=1、X1=1,RACK有上升沿时,把总线上的数据打入通用寄存器。

可通过设置X0、X1来指定通用寄存器工作方式,通用寄存器的输出端Q0~Q7接入判零电路。

LED(ZD)亮时,表示当前通用寄存器内数据为0。

输出缓冲器采用74LS244,当控制信号RA-O为低时,74LS244开通,把通用寄存器内容输出到总线;当RA-O为高时,74LS244的输出为高阻。

GAL方程如下:

Clk,OEpin1,11;

A,B,C,Dpin3,4,5,6;

QA,QB,QC,QDpin18,17,14,13;

S0,S1,SIL,SIRpin8,9,2,7;

Q=[QD,QC,QB,QA];

I=[D,C,B,A];

SL=[QC,QB,QA,SIL];

SR=[SIR,QD,QC,QB];

equations

Q:

=S0&S1&I

#S0&!

S1&SR

#!

S0&S1&SL

#!

S0&!

S1&Q;

图2-2-2

3.3控制信号说明

信号名称

作用

有效电平

X0、X1

74LS198的工作模式

ERA

选通通用寄存器

低电平有效

RA-O

通用寄存器内容输出至总线

低电平有效

RACK

通用寄存器工作脉冲

上升延有效

M

在ALU单元中作为逻辑和算术运算的选择。

在本实验中决定是否带进位移位

0带进位

1不带进位

四.实验步骤

实验1、数据输入通用寄存器

●把RA-IN(8芯的盒型插座)与CPT-B板上二进制开关单元中的J01插座相连(对应二进制开关H16~H23),把RA-OUT(8芯的盒型插座)与数据总线上的DJ6相连。

●把RACK连到脉冲单元的PLS1,把ERA、X0、X1、RA-O、M接入二进制拨动开关。

(请按下表接线)。

信号定义

接入开关位号

RACK

PLS1孔

X0

H12孔

X1

H11孔

ERA

H10孔

RA-O

H9孔

M

H4孔

●二进制开关H16~H23作为数据输入,置42H(对应开关如下表)。

H23

H22

H21

H20

H19

H18

H17

H16

数据总线值

D7

D6

D5

D4

D3

D2

D1

D0

8位数据

0

1

0

0

0

0

1

0

42H

置各控制信号如下:

H12

H11

H10

H9

H4

X0

X1

ERA

RA-O

M

1

1

0

0

1

●按启停单元中的运行按钮,置实验平台为运行状态。

●按脉冲单元中的PLS1脉冲按键,在RACK上产生一个上升沿,把42H打入通用寄存器。

●此时数据总线上的指示灯IDB0~IDB7应该显示为42H。

由于通用寄存器内容不为0,所以LED(ZD)灯灭。

实验2、寄存器内容无进位位左移实验

●按照实验1数据输入的方法把数据42H打入通用寄存器中,数据总线上显示42H。

●实现左移功能,置各控制信号如下:

H12

H11

H10

H9

H4

X0

X1

ERA

RA-O

M

0

1

0

0

1

●按启停单元中的运行按钮,置实验平台为运行状态。

●按脉冲单元中的PLS1脉冲按键,在RACK上产生一个上升沿,使通用寄存器中的值左移。

●此时数据总线上的LED指示灯IDB0~IDB7应该显示为84H。

由于通用寄存器内容不为0,所以ZD(LED)灯灭。

●按脉冲单元中的PLS1脉冲按键,使通用寄存器中的值左移,此时数据总线上的LED指示灯IDB0~IDB7应该显示为09H。

若一直按PLS1,在总线上将看见数据循环左移的现象。

实验3、寄存器内容无进位位右移实验

●按照实验1数据输入的方法把数据42H打入通用寄存器中,数据总线上显示42H。

●实现右移功能,置各控制信号如下:

H12

H11

H10

H9

H4

X0

X1

ERA

RA-O

M

1

0

0

0

1

●按启停单元中的运行按钮,置实验平台为运行状态。

●按脉冲单元中的PLS1脉冲按键,在RACK上产生一个上升沿,使通用寄存器中的值右移。

●此时数据总线上的LED指示灯IDB0~IDB7应该显示为21H。

由于通用寄存器内容不为0,所以ZD(LED)灯灭。

●按脉冲单元中的PLS1脉冲按键,使通用寄存器中的值右移,此时数据总线上的LED指示灯IDB0~IDB7应该显示为90H。

若一直按PLS1,在总线上将看见数据循环左移的现象。

附:

通用寄存器的逻辑

通用寄存器(8位并入并出移位寄存器)

CLR

X1X0

CLK

SLSR

QA~AH

0

XX

X

XX

全0

1

XX

0

XX

保持不变

1

11

上升沿

XX

并行接数A~H

1

01

上升沿

X0

右移移入0

1

01

上升沿

X1

右移移入1

1

10

上升沿

0X

左移移入0

1

10

上升沿

1X

左移移入1

实验三进位控制、通用寄存器判零实验

一.实验目的

1、熟悉带进位控制的算术逻辑运算器的组成和硬件电路

2、用进位寄存器来实现带进位的左移、右移。

3、熟悉判零线路。

二.实验要求

按照实验步骤完成实验项目,实现带进位位的算术逻辑运算,通用寄存器实现带进位的左移、右移功能,理解通用寄存器的判零电路。

三.实验说明

3.1进位和判零电路的实验构成

进位和判零电路由1片GAL、74LS74和两个LED(CY、ZD)发光管组成。

当有进位时CY发光管亮,ZD发光管亮表示当前通用寄存器的内容为0。

图2-3-1

3.2进位控制的原理:

(如图2-3-1)

●进位电路与通用寄存器、ALU有着非常紧密的关系,算术逻辑单元的进位输出和通用寄存器带进位移动都会影响进位寄存器中的结果。

●若实验者在做算术逻辑实验时,选择了算术运算方式,当ALU的计算结果输出至总线时,在CCK上来一个上升沿,将把74LS181的进位输出位(CN+4)上的值(为了统一进位标识,1表示有进位,0表示无进位),打入进位寄存器(74LS74)中,并且有进位时LED(CY)发光。

●在进行通用寄存器的数据移位实验时,把CCK和通用寄存器的工作脉冲接在一起,当选择带进位左移动时,在工作脉冲下,通用寄存器的最高位将移入进位寄存器中,进位寄存器中的值将移入通用寄存器的最低位。

当进位寄存器中的值为1时,LED(CY)发亮,若进位寄存器中的值为0时,LED(CY)灭。

同样在带进位右移时,也会产生这样的效果。

●通过把通用寄存器中的每一位做“或”运算,当寄存器的每一位为0时,ZD输出0,LED(ZD)发光。

以下为GAL中的方程:

Q0Q1Q2Q3Q4Q5Q6Q7MX0X1GND

CN+4ALU_OCYNCNCCY_IZDCSRSLERAVCC

SR=M*/X1*X0*Q0+/M*/X1*X0*CY+/ALU_O*/CN+4

SL=M*X1*/X0*Q7+/M*X1*/X0*CY+/ALU_O*/CN+4

CY_I=/X1*X0*Q0+X1*/X0*Q7+/ALU_O*/CN+4

/ZD=/Q0*/Q1*/Q2*/Q3*/Q4*/Q5*/Q6*/Q7

四.实验步骤

实验1、算术逻辑单元带进位位的加法运算实验

●把ALU-IN(8芯的盒型插座)与CPT-B板上的二进制开关单元中J01插座相连(对应二进制开关H16~H23),把ALU-OUT(8芯的盒型插座)与数据总线上的DJ2相连。

●把D1CK、D2CK、CCK用连线连到脉冲单元的PLS1上,把EDR1、EDR2、ALU-O、S0、S1、S2、S3、CN、M接入二进制拨动开关(请按下表接线)。

信号定义

接入开关位号

D1CK

PLS1孔

D2CK

PLS1孔

CCK

PLS1孔

EDR1

H8孔

EDR2

H7孔

ALU-O

H6孔

CN

H5孔

M

H4孔

S3

H3孔

S2

H2孔

S1

H1孔

S0

H0孔

●按启停单元中停止按钮,实验平台停机并且把进位寄存器CY清零(CY灯灭)。

在本实验中使用算术逻辑单元作为进位发生器,按运行键,实验即进入运行状态。

●二进制开关H16~H23作为数据输入,置65H(对应开关如下表)。

H23

H22

H21

H20

H19

H18

H17

H16

数据总线值

D7

D6

D5

D4

D3

D2

D1

D0

8位数据

0

1

1

0

0

1

0

1

65H

置各控制信号如下:

H8

H7

H6

H5

H4

H3

H2

H1

H0

EDR1

EDR2

ALU-O

CN

M

S3

S2

S1

S0

0

1

1

1

0

1

0

0

1

●按脉冲单元中的PLS1脉冲按键,在D1CK上产生一个上升沿,把65H打入DR1数据锁存器,通过逻辑笔或示波器来测量确定DR1寄存器(74LS374)的输出端,检验数据是否进入DR1中。

●二进制开关H16~H23作为数据输入,置A7H(对应开关如下表)。

H23

H22

H21

H20

H19

H18

H17

H16

数据总线值

D7

D6

D5

D4

D3

D2

D1

D0

8位数据

1

0

1

0

0

1

1

1

A7H

置各控制信号如下:

H8

H7

H6

H5

H4

H3

H2

H1

H0

EDR1

EDR2

ALU-O

CN

M

S3

S2

S1

S0

1

0

1

1

0

1

0

0

1

●按脉冲单元中的PLS1脉冲按键,在D2CK上产生一个上升沿,把A7H打入DR2数据锁存器。

●再置各控制信号如下:

H8

H7

H6

H5

H4

H3

H2

H1

H0

EDR1

EDR2

ALU-O

CN

M

S3

S2

S1

S0

1

1

0

1

0

1

0

0

1

●按脉冲单元中的PLS1脉冲按键,在CCK上产生一个上升沿,把74LS181的进位打入进位寄存器中,在有进位的情况下,CY指示灯亮,并且ALU-O为0,把计算结果输出到数据总线。

●经过74LS181的计算将产生进位,即CN+4输出0,当把计算结果输出到总线时,数据总线指示灯IDB0~IDB7将显示结果0CH。

实验2、带进位移位实验

●按启停单元中停止按钮,实验平台停机时把进位寄存器CY清零(CY灯灭)。

在本实验中使用通用寄存器作为进位发生器,按运行键,实验即进入运行状态。

●把RA-IN(8芯的盒型插座)与CPT-B板上的二进制开关单元中J01相连(对应二进制开关H16~H23),把RA-OUT(8芯的盒型插座)与数据总线上的DJ6相连。

●把CCK、RACK连到脉冲单元的PLS1,把ERA、X0、X1、RA-O、M接入二进制拨动开关。

(请按下表接线)。

信号定义

接入开关位号

CCK

PLS1孔

RACK

PLS1孔

X0

H12孔

X1

H11孔

ERA

H10孔

RA-O

H9孔

M

H4孔

●二进制开关H16~H23作为数据输入,置81H(对应开关如下表)。

H23

H22

H21

H20

H19

H18

H17

H16

数据总线值

D7

D6

D5

D4

D3

D2

D1

D0

8位数据

1

0

0

0

0

0

0

1

81H

置各控制信号如下:

H12

H11

H10

H9

H4

X0

X1

ERA

RA-O

M

1

1

0

0

0

●按脉冲单元中的PLS1脉冲按键,在RACK上产生一个上升沿,把81H打入通用寄存器内。

●此时数据总线上的指示灯IDB0~IDB7应该显示为81H。

由于通用寄存器内容不为0,所以ZD(LED)灯灭。

置各控制信号如下:

H12

H11

H10

H9

H4

X0

X1

ERA

RA-O

M

0

1

0

0

0

●按脉冲单元中的PLS1脉冲按键,在RACK上产生一个上升沿,使通用寄存器中的值左移。

因进位寄存器CY的初始值为0,在RACK脉冲作用下将CY打入通用寄存器的最低位Q0。

同时在CCK脉冲作用下把通用寄存器的最高位Q7(为1)打入进位寄存器CY,使CY显示灯亮,这样就实现了