基于FPGA的数字时钟课程设计.docx

《基于FPGA的数字时钟课程设计.docx》由会员分享,可在线阅读,更多相关《基于FPGA的数字时钟课程设计.docx(25页珍藏版)》请在冰豆网上搜索。

基于FPGA的数字时钟课程设计

西安郵電學院

基于FPGA的数字时钟

院别:

电子工程学院

班级:

成员:

技术规范

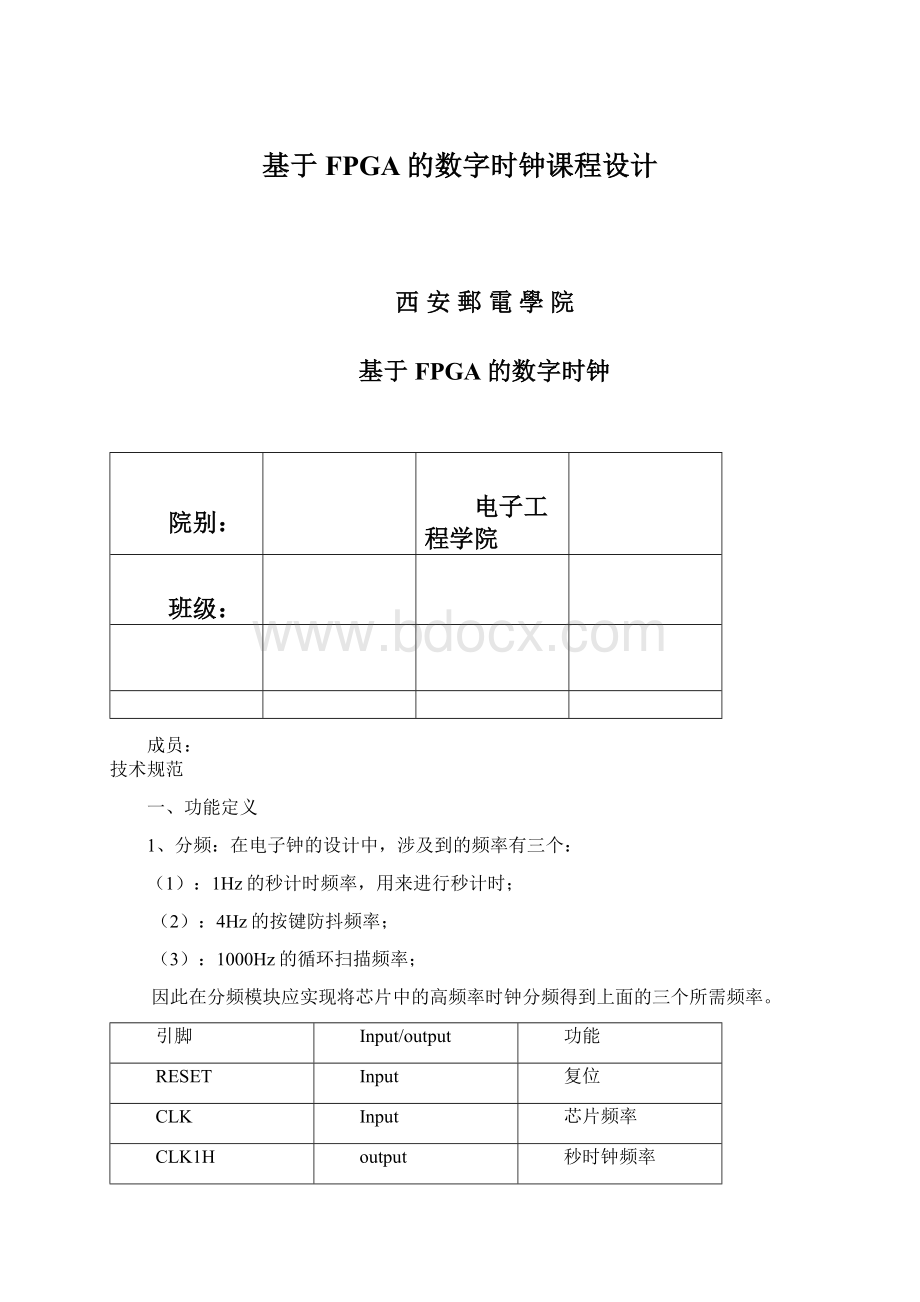

一、功能定义

1、分频:

在电子钟的设计中,涉及到的频率有三个:

(1):

1Hz的秒计时频率,用来进行秒计时;

(2):

4Hz的按键防抖频率;

(3):

1000Hz的循环扫描频率;

因此在分频模块应实现将芯片中的高频率时钟分频得到上面的三个所需频率。

引脚

Input/output

功能

RESET

Input

复位

CLK

Input

芯片频率

CLK1H

output

秒时钟频率

CLK1K

output

扫描频率

CLK4H

output

扫描按键频率

2、控制:

进行正常计时,时间调整,时间复位模式的选择:

(1)时间初始复位;

(2)选择秒时间调整的模式;

(3)选择分时间调整的模式;

(4)选择小时时间调整的模式;

引脚

Input/output

功能

CLK4H

Input

扫描按键频率

RESET

Input

复位

[5:

0]MIN

output

复位分钟

[5:

0]SEC

output

复位秒钟

[4:

0]HOUR

output

复位时钟

[1:

0]KEY

Input

按键(进行模式的选择和调时)

[1:

0]TS

output

模式的选择

EN

output

使能(复位或计时选择)

D

output

调节时间的时钟

3、计时:

进行调整时间,正常计时;

(1)正常计时;

(2)调整秒计时;

(3)调整分计时;

(4)调整时计时;

引脚

Input/output

功能

CLK1H

input

秒时钟频率

[5:

0]MIN

output

分钟计时输出

[5:

0]SEC

output

秒钟计时输出

[4:

0]HOUR

output

时钟计时输出

[1:

0]TS

input

模式的选择

D

input

调节时间的时钟

EN

input

使能(复位或计时选择)

[5:

0]DATA_M

input

复位分钟

[5:

0]DATA_S

input

复位秒钟

[4:

0]DATA_H

input

复位时钟

4、选择输出:

进行时间高低位的变换及循环扫描输出:

(1)进行时间高低位的变换;

(2)进行时间的循环扫描;

引脚

Input/output

功能

CLK1K

input

循环扫描时钟

[5:

0]MIN

input

分钟计时输入

[5:

0]SEC

input

秒钟计时输入

[4:

0]HOUR

input

时钟计时输入

[5:

0]SEG

output

进行数码管的选通

[3:

0]OUT

output

时间的输出

5、译码:

对时间进行七段数码管的译码:

引脚

Input/output

功能

[3:

0]DATA_IN

input

时间的输入

[7:

0]LED

output

七段译码的输出

二、总引脚定义

引脚

Input/output

功能

RESET

Input

复位

CLK

Input

芯片频率

[1:

0]KEY

Input

按键(进行模式的选择和调时)

[7:

0]LED

output

七段译码的输出

[5:

0]SEG

output

进行数码管的选通

设计思路:

一、总体设计思路图:

二、功能引脚定义

1、总体引脚

(1)K[1]:

输入,控制是否进入调整模式,调时模式或调分模式。

(2)K[2]:

输入,根据K1的选择进行加1调时。

(3)CLK:

输入,1赫兹,控制秒钟的频率。

(4)CLK1K:

输入,1K赫兹,控制时间的连续扫描输出。

(5)[7:

0]LED:

输出,七段显示译码管的输入。

(6)[5:

0]SEG:

输出,控制六个数码管的是否接通。

(7)SC:

输入,时间复位。

2、

(1)控制模块:

输出控制信号和时分秒计时。

控制信号控制时分秒是否正常计时。

K[1]:

输入,控制是否进入调整模式,调时模式或调分模式。

K[2]:

输入,根据K1的选择进行加1调时。

SC:

输入,时间复位。

[5:

0]SEC:

复位秒计时。

[5:

0]MIN:

复位、调时分计时。

[5:

0]HOUR:

复位、调时时计时。

KEN:

控制是否进行正常及时、进入调时复位状态。

(2)计时模块

秒计时:

输出正常的秒计时或复位计时。

分计时:

输出正常的分计时或复位计时或调时计时。

时计时:

输出正常的时计时或复位计时或调时计时。

(3)时间扫描模块:

利用高频率的时钟不断地循环扫描是分秒计时,以便循环译码;输出控制信号,控制数码管是否有效;此模块同时进行时间的高地位的计算与输出。

[5:

0]SEC:

输入,计时时间。

[5:

0]MIN:

输入,计时时间。

[4:

0]HOUR:

输入,计时时间。

CLK1K:

输入,1K赫兹,高时钟进行扫描。

[3:

0]OUT:

进行时间的输出。

[5:

0]SEG:

输出,进行数码管的选通控制。

(4)七段译码管:

对时分秒的高低位进行译码输出显示。

电路设计源代码及生成模块图

总模块:

moduleDZZ_ZH(KEY,RESET,CLK,LED,SEG);

output[7:

0]LED;

output[5:

0]SEG;

input[1:

0]KEY;

inputRESET;

inputCLK;

reg[6:

0]LED;

reg[5:

0]SEG;

wireWCLK1H,WCLK1K;

wire[5:

0]WMIN,WSEC;

wire[4:

0]WHOUR;

wireWEN,WD,WB;

wire[1:

0]WTS;

wireWCO1,WCO2;

wire[3:

0]WOUT;

wire[5:

0]WDATA_S,WDATA_M;

wire[4:

0]WDATA_H;

wireWCLK4H;

DZZ_FPA1(.CLK(CLK),.CLK1H(WCLK1H),.CLK1K(WCLK1K),.RESET(RESET),.CLK4H(WCLK4H));

DZZ_TA2(.KEY(KEY),.RESET(RESET),.HOUR(WHOUR),.MIN(WMIN),.SEC(WSEC),.TS(WTS),.D(WD),.EN(WEN),.CLK4H(WCLK4H));

DZZ_SA3(.DATA_S(WSEC),.SEC(WDATA_S),.CLK(WCLK1H),.KEN(WEN),.CO(WCO1),.TS(WTS),.D(WD));

DZZ_MA4(.DATA_M(WMIN),.MIN(WDATA_M),.CLK(WCO1),.KEN(WEN),.CO(WCO2),.D(WD),.TS(WTS));

DZZ_HA5(.DATA_H(WHOUR),.HOUR(WDATA_H),.CLK(WCO2),.D(WD),.KEN(WEN),.TS(WTS));

DZZ_SLA6(.DATA_S(WDATA_S),.DATA_M(WDATA_M),.DATA_H(WDATA_H),.OUT(WOUT),.CLK1K(WCLK1K),.B(WB),.SEG(SEG));

DZZ_YMA7(.DATA_IN(WOUT),.LED(LED),.D(WB));

Endmodule

一、分频:

moduleDZZ_FP(CLK,CLK1H,CLK1K,RESET,CLK4H);

outputCLK1H,CLK1K,CLK4H;

inputCLK;

inputRESET;

regCLK1K,CLK1H,CLK4H;

reg[12:

0]CNT1;

reg[24:

0]CNT2;

reg[22:

0]CNT3;

always@(posedgeCLKornegedgeRESET)

begin

if(!

RESET)

begin

CNT1<=13'b0000_0000_0000_0;

CLK1K<=0;

end

elseif(CNT1==13'b1000_0010_0011_0)

begin

CNT1<=13'b0000_0000_0000_0;

CLK1K<=~CLK1K;

end

else

begin

CNT1<=CNT1+1'b1;

end

end

always@(posedgeCLKornegedgeRESET)

begin

if(!

RESET)

begin

CNT2<=25'b0000_0000_0000_0000_0000_0000_0;

CLK1H<=0;

end

elseif(CNT2==25'b1011_1110_1011_1100_0100_0000_0)

begin

CNT2<=25'b0000_0000_0000_0000_0000_0000_0;

CLK1H<=~CLK1H;

end

else

begin

CNT2<=CNT2+1'b1;

end

end

always@(posedgeCLKornegedgeRESET)

begin

if(!

RESET)

begin

CNT3<=23'b0000_0000_0000_0000_0000_000;

CLK4H<=0;

end

elseif(CNT3==23'b1011_1110_1011_1100_0100_000)

begin

CNT3<=23'b0000_0000_0000_0000_0000_000;

CLK4H<=~CLK4H;

end

else

begin

CNT3<=CNT3+1'b1;

end

end

endmodule

二、控制模块代码:

moduleDZZ_T(KEY,RESET,HOUR,MIN,SEC,TS,D,EN,CLK4H);

output[4:

0]HOUR;

output[5:

0]MIN;

output[5:

0]SEC;

outputD;

output[1:

0]TS;

outputEN;

input[1:

0]KEY;

inputRESET;

inputCLK4H;

reg[4:

0]HOUR;

reg[5:

0]MIN;

reg[5:

0]SEC;

regEN;

regD;

reg[1:

0]TS;

always@(negedgeRESETorposedgeCLK4H)

begin

if(!

RESET)

begin

HOUR=5'b00000;

MIN=6'b000000;

SEC=6'b000000;

TS=2'b00;

EN=0;

D=0;

end

else

begin

EN=1;

if(!

KEY[1])

begin

TS=TS+1'b1;

end

else

begin

TS=TS;

end

if(!

KEY[0])

begin

D=1;//guanjian

EN=1;

end

else

begin

D=0;

EN=1;

end

end

end

endmodule

三、计时调整时间模块代码:

(1)小时计时和小时计时的调整:

moduleDZZ_H(DATA_H,HOUR,CLK,D,KEN,TS);

output[4:

0]HOUR;

input[4:

0]DATA_H;

inputCLK;

inputD;

input[1:

0]TS;

inputKEN;

reg[4:

0]HOUR;

regCLK1;

always@(TS)

begin

if(TS==2'b11)

CLK1=D;

else

CLK1=CLK;

end

always@(posedgeCLK1ornegedgeKEN)

begin

if(!

KEN)

begin

HOUR<=DATA_H;

end

else

begin

if(TS==2'b00)

begin

if(HOUR<=5'b10110)

begin

HOUR<=HOUR+1'b1;

end

else

begin

HOUR<=5'b00000;

end

end

elseif(TS==2'b11)

begin

if(HOUR<=5'b10110)

begin

HOUR<=HOUR+1'b1;

end

else

begin

HOUR<=5'b00000;

end

end

else

begin

HOUR<=HOUR;

end

end

end

endmodule

(2)分计时和分计时的调整:

moduleDZZ_M(DATA_M,MIN,CLK,KEN,CO,D,TS);

output[5:

0]MIN;

outputCO;

input[5:

0]DATA_M;

inputCLK;

inputD;

inputKEN;

input[1:

0]TS;

reg[5:

0]MIN;

regCO;

regCLK1;

always@(TS)

begin

if(TS==2'b10)

CLK1=D;

else

CLK1=CLK;

end

always@(posedgeCLK1ornegedgeKEN)

begin

if(!

KEN)

begin

MIN<=DATA_M;

end

else

begin

if(TS==2'b00)

begin

if(MIN<=6'b111010)

begin

MIN<=MIN+1'b1;

CO<=0;

end

else

begin

MIN<=6'b000000;

CO<=1;

end

end

elseif(TS==2'b10)

begin

if(MIN<=6'b111010)

begin

MIN<=MIN+1'b1;

end

else

begin

MIN<=6'b000000;

end

end

else

begin

MIN<=MIN;

end

end

end

endmodule

(3)秒计时和秒计时的调整:

moduleDZZ_S(DATA_S,SEC,CLK,KEN,CO,TS,D);

output[5:

0]SEC;

outputCO;

input[5:

0]DATA_S;

inputCLK;

inputKEN;

input[1:

0]TS;

inputD;

reg[5:

0]SEC;

regCO;

regCLK1;

always@(TS)

begin

if(TS==2'b01)

CLK1=D;

else

CLK1=CLK;

end

always@(posedgeCLK1ornegedgeKEN)

begin

if(!

KEN)

begin

SEC<=DATA_S;

end

else

begin

if(TS==2'b00)

begin

if(SEC<=6'b111010)

begin

SEC<=SEC+1'b1;

CO<=0;

end

else

begin

SEC<=6'b000000;

CO<=1;

end

end

elseif(TS==2'b01)

begin

if(SEC<=6'b111010)

begin

SEC<=SEC+1'b1;

end

else

begin

SEC<=6'b000000;

end

end

else

begin

SEC<=SEC;

end

end

end

endmodule

四、选择模块:

moduleDZZ_SL(DATA_S,DATA_M,DATA_H,OUT,SEG,CLK1K,B);

output[3:

0]OUT;

output[5:

0]SEG;

outputB;

input[5:

0]DATA_S;

input[5:

0]DATA_M;

input[4:

0]DATA_H;

inputCLK1K;

reg[3:

0]OUT;

regB;

reg[5:

0]SEG;

reg[2:

0]SLECT;

parameter

S0=3'b000,

S1=3'b001,

S2=3'b010,

S3=3'b011,

S4=3'b100,

S5=3'b101;

always@(posedgeCLK1K)

begin

case(SLECT)

S0:

begin

OUT<=DATA_H/6'b1010;

SEG<=6'b011111;

B<=0;

SLECT<=S1;

end

S1:

begin

OUT<=DATA_H%6'b1010;

SEG<=6'b101111;

B<=1;

SLECT<=S2;

end

S2:

begin

OUT<=DATA_M/6'b1010;

SEG<=6'b110111;

B<=0;

SLECT<=S3;

end

S3:

begin

OUT<=DATA_M%6'b1010;

SEG<=6'b111011;

B<=1;

SLECT<=S4;

end

S4:

begin

OUT<=DATA_S/6'b1010;

SEG<=6'b111101;

B<=0;

SLECT<=S5;

end

S5:

begin

OUT<=DATA_S%6'b001010;

SEG<=6'b111110;

B<=0;

SLECT<=S0;

end

default:

begin

SLECT<=S0;

SEG<=6'b111111;

end

endcase

end

endmodule

五、译码:

moduleDZZ_YM(DATA_IN,LED,D);

output[7:

0]LED;

input[3:

0]DATA_IN;

inputD;

reg[7:

0]LED;

parameter

S0=4'b0000,

S1=4'b0001,

S2=4'b0010,

S3=4'b0011,

S4=4'b0100,

S5=4'b0101,

S6=4'b0110,

S7=4'b0111,

S8=4'b1000,

S9=4'b1001;

always@(DATA_IN)

begin

if(D)

begin

case(DATA_IN)

S0:

begin

LED=8'b11111101;

end

S1:

begin

LED=8'b01100001;

end

S2:

begin

LED=8'b11011011;

end

S3:

begin

LED=8'b11110011;

end

S4:

begin

LED=8'b01100111;

end

S5:

begin

LED=8'b10110111;

end

S6:

begin

LED=8'b10111111;

end

S7:

begin

LED=8'b11100001;

end

S8:

begin

LED=8'b11111111;

end

S9:

begin

LED=8'b11110111;

end

default:

LED=8'b00000000;

endcase

end

else

begin

case(DATA_IN)

S0:

begin

LED=8'b11111100;

end

S1:

begin

LED=8'b01100000;

end

S2:

begin

LED=8'b11011010;

end

S3:

begin

LED=8'b11110010;

end

S4:

begin

LED=8'b01100110;

end

S5:

begin

LED=8'b10110110;

end

S6:

begin

LED=8'b10111110;

end

S7:

begin

LED=8'b11100000;

end

S8:

begin

LED=8'b11111110;

end

S9:

begin

LED=8'b11110110;

end

default:

LED=8'b00000000;

endcase

end

end

endmodule

综合布局布线报告

总体设计模块:

分频、计时、译码;

计时:

控制、秒计时、分计时、时计时、循环选择;

作业心得体会

在本次的作业报告中我学会了如何使用modesim和quartus软件进行电路的验证和仿真。

在电路的设计初始时刻,我没有按照设计电路时从上到下的设计方法,而是盲目的进行对电路的模块进行设计。

结果在最后的设计综合的时候,设计的各个模块不能进行顺利的综合和仿真。

在电子钟的设计中我对时钟的理解不是很透彻,因此在进行计时的时候出现了很多的问题。

在进行时分秒的计时时,我对时间的如何进位没有很好的理解,在计时时出现了很多问题,最后在同学的帮助下得到了很好的解决。

在对按键的使用中我也出现了很困惑的问题。

调整时间的时候,我使用了按键的触发,结果在时间调整计时的时候老是出现时间的快速跳动和不确定性。

最后我引入了按键的扫描时钟,使用4Hz的频率来扫描按键的高低电平,然后利用按键的高低电平来触发调整计时的触发频率,这样很好的解决了按键的抖动问题。

在使用verilogHDL进行电路代码的书