直流电机的PWM控制.docx

《直流电机的PWM控制.docx》由会员分享,可在线阅读,更多相关《直流电机的PWM控制.docx(8页珍藏版)》请在冰豆网上搜索。

直流电机的PWM控制

设计报告

课程名称在系统编程技术

任课教师

设计题目直流电机的PWM控制

班级

学号

日期2011年6月13日

一、题目分析

本实验设计的直流电机的PWM控制系统需要满足以下两点要求:

直流电机的转速具有4个档位可供调节;

通过按键控制直流电机的转向。

二、方案选择

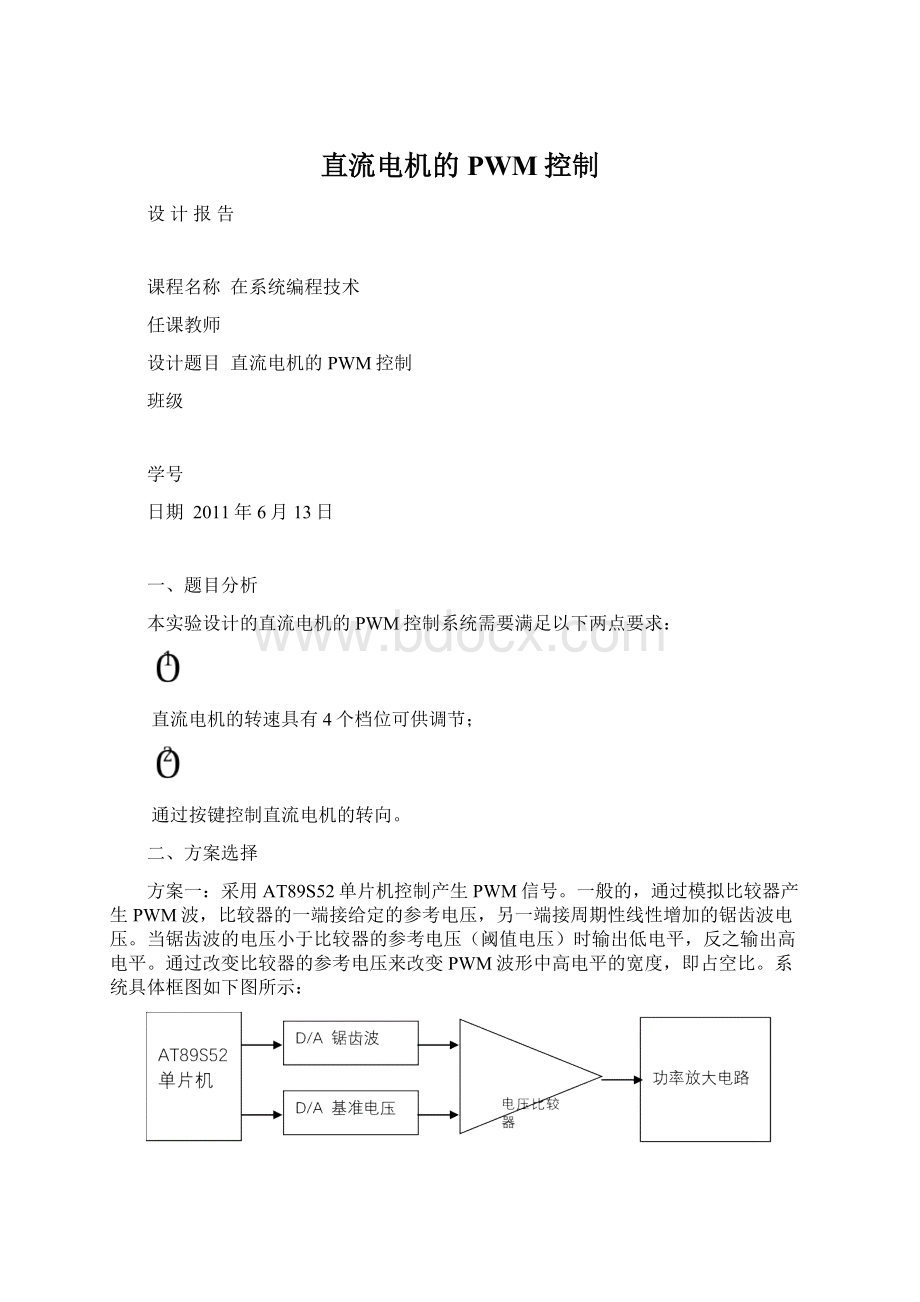

方案一:

采用AT89S52单片机控制产生PWM信号。

一般的,通过模拟比较器产生PWM波,比较器的一端接给定的参考电压,另一端接周期性线性增加的锯齿波电压。

当锯齿波的电压小于比较器的参考电压(阈值电压)时输出低电平,反之输出高电平。

通过改变比较器的参考电压来改变PWM波形中高电平的宽度,即占空比。

系统具体框图如下图所示:

图1单片机实现PWM控制系统框图

方案二:

利用FPGA内部资源实现产生PWM波。

用VHDL语言描述设计数字比较器,数字比较器的一端接设定值计数器输出,另一端接线性递增计数器输出端。

当线性计数器的计数值小于设定值时输出低电平,反之输出高电平。

方案一需要通过D/A转换器产生锯齿波电压和设置参考电压,通过外接模拟比较器输出PWM波形,因此外围电路比较复杂。

方案二省去了外接D/A转化器和模拟比较器,FPGA外部连线很少,电路更加简单、便于控制。

所以本系统选择方案二。

三、系统细化框图

基于FPGA的直流电机PWM控制电路主要由以下三个部分组成:

(1)FPGA中PWM脉宽调制信号产生电路。

(2)FPGA中的正/反转方向控制电路。

(3)H桥功率驱动电路。

图2FPGA直流电机驱动控制系统框图

四、各模块设计与实现

由系统细化框图可得系统顶层原理图,如附录1所示。

系统顶层包括设定计数器、锯齿波发生器、数字比较器、旋转方向控制电路和H桥驱动电路。

4.1设定计数器的设计

设定计数器为系统的转速控制模块,此模块等效于模拟电路的比较器的基准电压。

通过CASE语句实现对不同数值选择,从而实现改变基准数值。

如图所示,具体程序实现如附录2所示

图3设定计数器的顶层模块图

4.2锯齿波发生器的设计

此锯齿波发生器的实质为一四进制计数器和锁存器的组合。

脉宽技术器在时钟脉冲的激励下输出从0开始增大的锯齿波。

每增大一次后对外发送一次。

如图所示,具体程序实现如附录3所示

图4锯齿波发生器的顶层模块图

4.3数字比较器的设计

数字比较器的输入端接设定计数器的输出端和锯齿波发生器的输出端,这两路数据经过数字比较器处理后,选择输出较大的值,并维持一定长度的电平。

如下图所示,具体程序实现如附录4所示。

图5数字比较器顶层模块图

4.4旋转方向控制电路的设计

旋转方向控制电路控制直流电机转向,该电路由两个2选1多路选择器组成。

如下图所示,具体程序实现如附录5所示

图6旋转方向控制电路顶层模块图

4.5H桥功率驱动电路设计

H桥功率驱动电路为BTL功率放大电路的典型应用。

具体实现电路,如下图所示

图7H桥功率驱动电路

五、时序仿真与功能仿真

取ENDTime为50us,以便有足够长的时间观察,CLK时钟信号设置频率为20MHz。

仿真波形如下图所示

图8时序仿真波形图

六、总结

经过为期近一个月的课程设计,感觉不只是时间的考验而且是对耐心的考验。

不过,最终还是完成了“直流电机的PWM控制”。

从对比中得出,用FPGA实现PWM波的控制较模拟电路更为简单、稳定,从比较器中看就很容易得出此结论。

另外,PROCESS在FPGA中进行并行操作,从此项特点上可以看出FPGA在人工智能和机器人的开发上具有很大的潜力。

所以,研究FPGA对直流电机的控制对发展机电一体化技术具有很好的铺垫作用。

七、参考文献

[1]松《EDA技术实用教程》[M]..科学出版社.2002.10

[2]吴继华,王诚.AlteraFPGA/CPLD设计(高级篇),人民邮电出版社,2005

[3]辉基于FPGA的数字系统设计西安电子科技大学出版社2008-11-1

附录:

1、系统顶层原理图

2、设定计数器源代码

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYDECTIS

PORT(SET:

INSTD_LOGIC;

D:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));

END;

ARCHITECTUREoneOFDECTIS

SIGNALCQ:

STD_LOGIC_VECTOR(1DOWNTO0);

BEGIN

PROCESS(CQ)

BEGIN

CASECQIS

WHEN"00"=>D<="0001";

WHEN"01"=>D<="0110";

WHEN"10"=>D<="1011";

WHEN"11"=>D<="1111";

WHENOTHERS=>NULL;

ENDCASE;

ENDPROCESS;

PROCESS(SET)

BEGIN

IFSET'EVENTANDSET='1'THENCQ<=CQ+1;

ENDIF;

ENDPROCESS;

END;

3、锯齿波发生器源代码

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYCNT5IS

PORT(CLK:

INSTD_LOGIC;

AA:

OUTSTD_LOGIC_VECTOR(4DOWNTO1));

ENDCNT5;

ARCHITECTUREBEHAVOFCNT5IS

SIGNALCQI:

STD_LOGIC_VECTOR(4DOWNTO0);

BEGIN

PROCESS(CLK)

BEGIN

IFCLK'EVENTANDCLK='1'THENCQI<=CQI+1;

ENDIF;

ENDPROCESS;

AA<=CQI(4DOWNTO1);

ENDBEHAV;

4、数字比较器源代码

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYCMP4IS

PORT(A:

STD_LOGIC_VECTOR(3DOWNTO0);

B:

STD_LOGIC_VECTOR(3DOWNTO0);

AGB:

OUTSTD_LOGIC);

ENDCMP4;

ARCHITECTUREBEHAVOFCMP4IS

BEGIN

PROCESS(A,B)

BEGIN

IF(A=B)OR(A>B)THENAGB<='1';

ELSEAGB<='0';

ENDIF;

ENDPROCESS;

ENDBEHAV;

5、二选一选择器源代码

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYMUX21AIS

PORT(A,B:

INBIT;

S:

INBIT;

Y:

OUTBIT);

ENDMUX21A;

ARCHITECTUREONEOFMUX21AIS

BEGIN

Y<=AWHENS<='0'ELSEB;

ENDARCHITECTUREONE