DSP数字信号处理.docx

《DSP数字信号处理.docx》由会员分享,可在线阅读,更多相关《DSP数字信号处理.docx(16页珍藏版)》请在冰豆网上搜索。

DSP数字信号处理

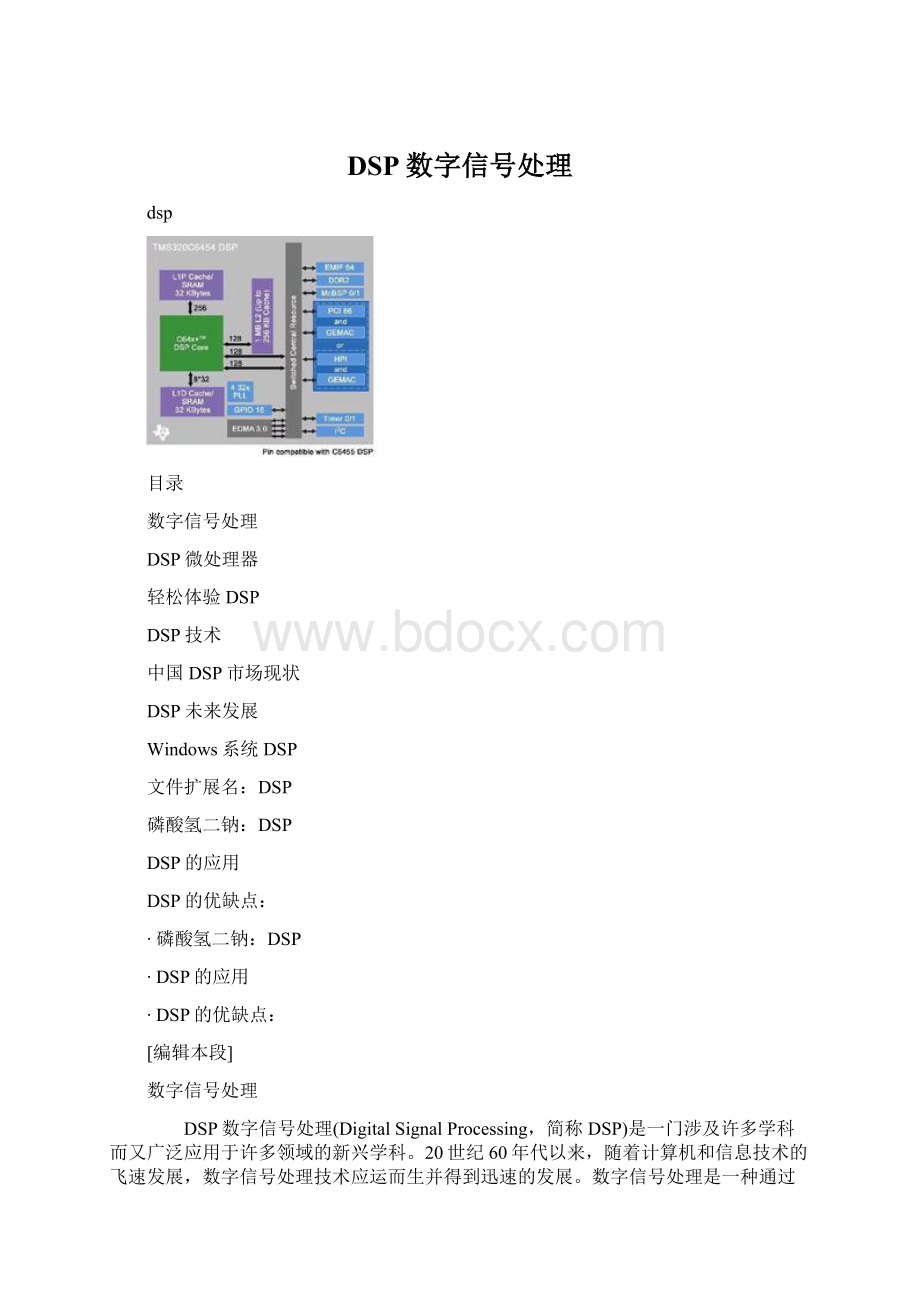

dsp

目录

数字信号处理

DSP微处理器

轻松体验DSP

DSP技术

中国DSP市场现状

DSP未来发展

Windows系统DSP

文件扩展名:

DSP

磷酸氢二钠:

DSP

DSP的应用

DSP的优缺点:

∙磷酸氢二钠:

DSP

∙DSP的应用

∙DSP的优缺点:

[编辑本段]

数字信号处理

DSP数字信号处理(DigitalSignalProcessing,简称DSP)是一门涉及许多学科而又广泛应用于许多领域的新兴学科。

20世纪60年代以来,随着计算机和信息技术的飞速发展,数字信号处理技术应运而生并得到迅速的发展。

数字信号处理是一种通过使用数学技巧执行转换或提取信息,来处理现实信号的方法,这些信号由数字序列表示。

在过去的二十多年时间里,数字信号处理已经在通信等领域得到极为广泛的应用。

德州仪器、Freescale等半导体厂商在这一领域拥有很强的实力。

[编辑本段]

DSP微处理器

DSP(digitalsignalprocessor)是一种独特的微处理器,是以数字信号来处理大量信息的器件。

其工作原理是接收模拟信号,转换为0或1的数字信号,再对数字信号进行修改、删除、强化,并在其他系统芯片中把数字数据解译回模拟数据或实际环境格式。

它不仅具有可编程性,而且其实时运行速度可达每秒数以千万条复杂指令程序,远远超过通用微处理器,是数字化电子世界中日益重要的电脑芯片。

它的强大数据处理能力和高运行速度,是最值得称道的两大特色。

DSP芯片,也称数字信号处理器,是一种特别适合于进行数字信号处理运算的微处理器器,其主要应用是实时快速地实现各种数字信号处理算法。

根据数字信号处理的要求,DSP芯片一般具有如下主要特点:

(1)在一个指令周期内可完成一次乘法和一次加法;

(2)程序和数据空间分开,可以同时访问指令和数据;

(3)片内具有快速RAM,通常可通过独立的数据总线在两块中同时访问;

(4)具有低开销或无开销循环及跳转的硬件支持;

(5)快速的中断处理和硬件I/O支持;

(6)具有在单周期内操作的多个硬件地址产生器;

(7)可以并行执行多个操作;

(8)支持流水线操作,使取指、译码和执行等操作可以重叠执行。

当然,与通用微处理器相比,DSP芯片的其他通用功能相对较弱些。

[编辑本段]

轻松体验DSP

第一种商品化的IC数字信号处理器是英特尔的2920,早在1979年就在取代全双工、1200bps数字硬调制解调器中的模拟滤波器组了。

同时,迅速增多的微处理器和外设提高了处理以数字表示信号的可行性。

那时几乎任何商业化信号处理任务都需要模拟计算,伴有复杂的反馈回路和补偿电路来维持稳定性。

各种依赖位片处理器小型电脑和数据采集硬件的技术都极其昂贵,并且通常只适合于研究人员。

能够经济地把信号数字化,并在数字领域进行数学计算,从而减少漂移和其它用模拟技术处理也很昂贵的不精确条件,这种逻辑很有吸引力,它直接导致今天市场上出现多种系列的DSP。

目前,某种形式的DSP安装在从自动应答电话机到洗衣机等各种产品的中心部位,很容易使人忘记这场变革就发生在最近。

直到最近,通用微控制器和DSP芯片之间的巨大差别还使许多嵌入式系统工程师觉得:

数字信号处理是门困难的学科。

这种感觉来源于第一代DSP的架构和编程要求,这一代DSP往往设计用来实现数字滤波器。

不过,在卷入DSP对比微控制器的争论之前,你也许要问,为什么使用数字滤波器?

DSP还适合于别的什么领域?

使用数字滤波的经典理由是,你可以实现线性相位FIR(有限脉冲响应)滤波器,它保持了音频处理等应用中的信号保真度。

当你正在尝试处理传感器信号时,避免由于不相等的组延迟(由非线性相位-频率响应特性引起)导致的信号失真可能也是很关键的。

正如任何已经尝试过的人所知道的那样,用模拟技术制造线性相位滤波器几乎是不可能的,相比之下,DSP和软件滤波器工具箱使这种实现不费吹灰之力。

假如你使用针对控制系统建模的仿真工具,你一定知道来自Mathworks的Matlab和Simulink等工具也可以建立DSP算法的模型,并自动生成代码,你可以把这些代码移植到各种硬件目标。

不过,数字信号处理的能力其实起始于滤波器应用。

例如,软件工具也可以毫不费力地实现FFT(快速傅里叶变换)。

然后,你可以对连续时间信号的快照做频率分析。

假如你有很多传感器输出要处理,以得到关键的实时控制响应,那么DSP通常是惟一的答案。

初学者工具包帮你建立信心

假如你第一次接触数字信号处理,你很可能想得到更多背景信息。

不过,阅读产品的相关资料无法取代亲自尝试它们,而初学者工具包提供了一种获得体验的轻松方式。

今天,与微控制器最相像的DSP系列就是摩托罗拉的DSP56F800,它主要针对实时控制应用。

例如,F805核心包括一个16比特定点引擎,该引擎运行在双哈佛架构上,以实现对程序和数据存储器的三路并行访问。

摩托罗拉的片上仿真技术通过一个JTAG标准的端口来提供系统内调试能力。

该器件是144引脚LQFP封装。

开发支持来自DSP56F805EVM,它包含一个130mm×165mm印制电路板、CodeWarriorIDE和一个SDK(软件开发工具包),价格为299美元。

该印制电路板上装有处理器,还有一个128k×16比特SRAM(外部代码和数据各为64k字)、一个RS-232端口,以及一个“并口至JTAG”接口,便于基于PC的调试。

一个正交解码器/霍尔效应接口和专用的马达控制逻辑给伺服控制等应用带来了便利。

各个跳线器选择不同的运行模式,多个起始码准备信号和I/O,用于轻松连接。

CodeWarrior安装的文档很有用地包括了56F805的硬件参考手册和数据表,以及该IDE的用法说明和参考手册。

要想迅速开始,请查看开发板的在线硬件手册,并确保所有跳线器都处在默认位置。

接着,把并口连接到你的PC,并尝试这些在线手册的“瞄准DSP56F805”(TargetingDSP56F805)部分。

这部分包括一个简要的指南,它示范如何创建、编译和链接F805代码。

在默认情况下,CodeWarrior使用“项目用具”(projectstationery)来构造新的项目。

这个方法自动创建和解开各种依赖处理器的功能、库、链接器命令和你的代码之间的依赖性。

假如你正用C语言编程,用具还可以进行启动文件的创建,以分配和初始化系统内存;你可以选择“空项目”并自己控制这些进程。

你可以在CodeWarrior的编辑器里无缝地混合和匹配C语言代码和汇编代码。

假如你使用预制用具,那么项目窗口会打开,显示代码、支持和库子目录;把它们展开,就可以访问恰当的资源,然后你可以编辑这些资源。

在项目窗口内选择“运行”(run)图标,默认的设定就会编译、链接并下载模板程序到开发板的外部SRAM。

线程窗口会打开,让你查看栈、变量和源代码,还有执行控制,比如设置/清除断点、运行、终止以及多种单步运行选项。

检查“视图”(View)菜单下的可用工具,比如表达式视图、全局变量视图和寄存器视图。

这些工具包括原始数据、反汇编、源和混合模式内存表示;你还可以从这儿直接编辑内存单元。

不过,你不会找到正式的剖析工具,你只有自己计算时序要求严格的任务。

一种替代办法是包含多个调用来启动和停止片上定时器,从而在关键点安插你的代码;除去调用开销,就得到了真实结果。

当然,假如你的代码运行没有超出截止期限,并且安插的代码位置适当,那么除去这种开销应该不会对运行造成消极影响。

由于片上内存使用和片外内存使用之间可能存在明显的性能差别,因此要确保测试的是真正的目标配置。

CodeWarrior只安装了一个F805例子,这个例子检测从板上开关到交替闪烁LED的中断。

你可以使用这个例子作为使用C语言编译器pragma指令、编写中断服务例程以及保存并调用库函数的指导。

不过,假如你想要CAN(控制器区域网络)例子,那你真不走运——这项功能是额外费用高级包中的一个价格为3000美元的选项。

其它高级功能包括安全例程,这其中含RSA(Rivest、Shamir和Adleman)、DES(数据加密标准)和3重DES算法,以及远程通信和语音处理函数,比如G711语音编码器。

其它开发工具包括200美元的“并口至JTAG”命令转换器;USB至JTAG转换器目前正在开发中。

你还可以指定1999美元的PCI至JTAG仿真器连接和2999美元的以太网同等品。

另一方面,对于那些好奇心很重、不需要F805的I/O功能的用户来说,有一个选项也许更好,那就是65美元的DSP56F801开发工具包。

该工具包还包括并列排线(parallel-cable)仿真、SDK以及CodeWarrior的一个免费版本,它局限于16kB程序内存。

无限制的IDE价格为495美元。

多媒体照亮实时控制

模拟器件公司(AnalogDevices)的Blackfin系列主要针对多媒体设备和便携式设备,包括三个代码兼容处理器,它们的不同之处仅在于速度和片上补充内存。

从内部来看,Blackfin内核包括一个双MAC定点处理引擎,该引擎把结果存储在两个40比特累加器里。

在使用中,VisualDSP++IDE的编译器利用最适合该内核架构的32比特“长”的值,在软件中自动合成浮点运算;你可以选择改变这种行为,以符合ANSII-C规范。

ADDS-BF533-EZlite初学者工具包现已上市,价格为295美元,它包括一块127mm×178mm印制电路板,板上装有处理器、2MB闪存和32MBSDRAM。

板上外设包括一个AD1836音频编解码器(带有四条输入声道和六条输出声道)、一个ADV7171视频编码器和ADV7183解码器(各带三个拾音插座、一个ADM3202RS-232线路驱动器/接收器—用于片上UART,它连接到一个DB9连接器、一个扩充接口—它承载并口、串口和SPI等各种I/O、一个JTAG在线仿真器头,以及各种LED和按钮。

该工具包依靠VisualDSP++IDE的一个20kB的代码有限版本,用于程序开发。

调试通信采用板上“USB至JTAG”调试接口,该接口允许与主机PC之间的非侵入式通信,这是通过该环境的背景遥测通道进行的。

不要理睬快速开始卡,遵照评估系统手册中的指示,VisualDSP++IDE就会顺利地安装好。

头两个练习介绍了链接器等基本元件如何通过让你建造、运行和修改某个过程(它计算来自定点数组的三个乘积的各个和)来互动。

有意思的是,C源代码窗口中的“混合”控制视图使你能够同时比较例程的C语言实现和汇编器实现。

某些IDE能够把源代码行拖到汇编器窗口中,或反过来,以找到相应的代码段,上述的同时比较功能是这种功能的替代方法。

其它编辑器功能允许设置和清除断点、启用行编号,以及设置书签。

假如你把第三课中的代码例子装载到前一课,你就能看到该IDE数据可视化能力的多个方面,比如正态图、正态图的FFT等价图,以及一份FIR滤波器响应分析。

由于这个例子及目前的其它Blackfin例子是针对535处理器,因此你需要把目标改到533。

由于工具包许可证不允许仿真器会话,因此请你下载整个软件及其评估许可证,连同许可证管理器工具程序。

运行该60MB的组合,就可以让你的安装升级。

90天后,它会回到最初的限制版。

在选择单一仿真器会话选项之后,你现在可以看到线性剖析仿真工具,它专门分析处理器在某应用程序内的何处花了时间。

双击某个例程,就会显示底层汇编器以及在该流程内部所花时间的百分比;双击某个程序计数器条目,就会高亮度显示相应的反汇编器输出。

软件剖析工具一般在函数的开头和结尾插入侵入性的“包装代码”,以获得统计数据。

VisualDSP++消除了这种开销,因为它用PC计数器的一个统计随机样本来记录指令地址,得到执行统计数据,并显示代码瓶颈。

ADI还还表示,该仿真器具有几项尖端而独特的功能,比如高速缓存和流水线可视化。

他指出,由于这些功能提供非常多的细节,因此它们是“只有仿真器才具有的功能”。

他说,在这个水平上,目前不可能不露痕迹地全速询问处理器,而又不往该部件“增加大量的逻辑和测试引脚”。

该环境在安装期间创建的ADSP-BF533文件夹包括多个针对533的例子,你可以把它们用作进一步开发的模板。

对新手的一个主要障碍是C语言程序员倾向于隐藏关键组件,比如头文件,并模糊它们的交互;好消息是伴随工具包的这些例子是极其清晰的。

你还将看到VSCE(VisualDSP++的组合式软件工程)模块,它们是预先配置的例程,根据模拟器件公司的VCSE标准编写。

这种做法使你能够把来自模拟器件公司和第三方厂商的符合标准的模块添加到你自己的项目中,不用担心各种冲突,比如内存冲突或I/O冲突。

1GHz的能力使并行I/O更快

假如你想做实验,那么你可能想知道和一个真正复杂的处理器打交道涉及哪些内容,这样的处理器包括德州仪器公司的TMS320C6000系列,它有用地提供了定点微分和浮点微分之间的代码兼容性。

一款新型初学者工具包展示了16比特定点6416的600MHz版本,它紧随该厂商的256比特甚长指令字型号之后。

这种顶级的机器针对I/O密集型应用,比如通信基础设施。

例如,该芯片把一个ATM(异步传输模式)接口装入其532引脚、0.8mm间距BGA封装中,封装大小仅为23mm2;其它通信外设包括维特比(Viterbi)和turbo解码器协处理器。

这种初学者工具包由SpectrumDigital公司制造,包括一个115mm×225mm印制电路板,板上装有DSP、一个TLV320AIC23编解码器、16MBSDRAM、512kB用户闪存和一个“USB至JTAG”仿真端口——所有这些的价格为395美元左右。

四个3.5mm立体声I/O端口与编解码器连接;一些简单的用户I/O端口连接到四个LED和若干钢琴键开关;高密度的扩充连接器提供额外的存储器、外设和PCI/HPI连接;两个端口选项提供外部仿真器。

尽管硬件很复杂,但用户友好的软件展示了德州仪器公司针对模块化软件开发的eXpressDSP理念。

理想情况下,eXpressDSP把应用程序抽象得足够好,非程序员可以通过在执行模板内部组合现成的算法来构造应用程序。

实际上,你需要充分的C语言编程经验来充分利用可提供给你的功能。

eXpressDSP的内核是DSP/BIOS内核,这是一种实时调度程序,该程序包括各种模块以处理各项中断、传输数据的管道和周期性事件。

事实上,DSP/BIOS构成了支持320C系列的RTOS的基础。

CodeComposerStudioIDE拥有一个DSP/BIOS配置工具,它使你能够在程序编译期间选择包括哪些模块,从而使该固件的内存占位(memoryfootprint)达到最小。

非常关键的是,每个DSP/BIOS模块都包括代码安插机制,允许CodeComposer通过USB仿真链接来调试运行中的应用程序。

为了使对实时操作的影响最小,当DSP芯片处于代码线程执行之间的闲置状态时,安插代码才开始运行。

你可以在它以图形格式在线程之间切换时查看执行图,这种格式帮助揭示被超过的截止期限。

其它使时序要求严格的任务分析变得容易的工具包括一张CPU负载图和一个统计窗口,后者报告某个线程的平均情形和最差情形执行时间。

你还可以从某个驻留在PC上的文件传送数据,比如来自DSO的输出,它代表了你想处理的真正信号。

DSP/BIOS提供了一组定义得非常好的API,它们适用于整个320Cxx系列,这样你可以轻松地在各种平台之间移植代码。

通过禁止直接访问外设和坚持可重入的可重定位码,eXpressDSP算法标准允许你轻松集成来自德州仪器公司和第三方厂商的符合标准的算法。

你可以下载免费的DSP/BIOS驱动程序开发工具包。

你还可以免费下载一组共三个参考框架应用程序,作为德州仪器公司大多数初学者工具包的“初学者件”。

全面的应用程序说明描述了这些模型的功能,包括其定制示例。

RF1针对的是约3.5k字大小的应用程序,它们需要一至三条通道和类似数量的eXpressDSP算法。

其局限包括不支持动态内存分配、线程预占、阻塞、多速率操作或控制函数。

由于这些原因,RF1最适合较低端的5xxx硬件平台。

中档的RF3一般适合6xxx芯片,这些芯片运行一至十条通道和一至十种算法。

RF3约为11k字的占位提供了RF1中没有的所有工具,但不包括任务阻塞。

最后,RF5版本提供了所有此类工具,并支持100多条通道和同样多种算法,代价是28k字内存。

RF5增强包括一个用于支持多处理器的单独线程。

附文:

通往DSP的最初几步

假定你想首先从DSP开始,那么你将面临几个挑战。

首先,如果你避开C语言,你将错过大量例子。

你可以通过等门户网站来免费提高C语言方面的技巧,但你一定要弄到几本参考课本。

其次,假如你想有效利用数字信号处理,你就不能逃避数学。

其包括复数理论,以及卷积和离散傅里叶变换等基本知识。

然后,你将需要选择一种处理器。

你必须考虑在定点和浮点算术功能之间进行选择,以及传统的微控制器选择准则。

总地说来,定点器件比同等的浮点器件需要更少的硅,并更便宜。

假如你正在使用定点器件,并在设计自己的算法,那么你往往必须在可选数字格式表示法之间做选择,这些表示法有时需要仔细的软件设计,以避免舍入和截断误差,这些误差使数据失真。

浮点芯片可以简化你的生活,因为它在硬件中实现了一致的数字表示系统,比如IEEE-754标准,它定义了32比特单精度和64比特双精度格式。

浮点DSP一般采用单精度表示法,这些表示法把23比特小数尾数、8比特指数和一个符号比特放入32比特的字中,使指数具有±127的动态范围。

厂商支持和工具链的提供情况是关键的考虑事项。

模拟器件、摩托罗拉和德州仪器提供各种DSP初学者工具包,跨越多种应用,从简单的马达控制器到复杂的通信链路。

不过,如果你想继续使用常规的微控制器,并且需要硬件乘法功能,请考虑英飞凌(Infineon)的新款XC167CI。

这种16比特处理器扩展了嵌入式166架构的功能,把32/40比特MAC(乘法/累加)单元包括进来,这种单元在25ns(40MHz时钟)内进行单周期乘法;其它增强包括一个柱形移位器。

要想获得更强的功能,该公司的32比特TriCore系列增加了多种功能,比如反向比特寻址,用于恢复FFT算法的输出。

[编辑本段]

DSP技术

基于DSP的智能视频监控系统

传统的视频监视系统是简单的非智能闭路电视(CCTV)系统,其缺点十分明显。

这样的系统或者需要安保人员实时监视画面以捕捉关键事件,或者需要在事后对视频记录进行回放并进行人工分析,耗时耗力,成本高而效率低。

近几年,DSP在智能视频监控系统方面的应用不断完善,正在逐渐取代传统的模拟非智能系统。

iSuppli公司2006年的一份分析报告曾指出,IP视频监控系统市场到2010年将增长近十倍。

IP监控的创新技术之一是“智能摄像机”,它拥有强大的数字信号处理器,能探测威胁并触发自动响应。

可见,DSP芯片是智能监控的核心。

提到DSP,多数人都会联想到TI公司。

该公司的DSP开发历史悠久,它所占据的DSP市场份额遥遥领先。

当然,TI公司也重视DSP在智能视频监控中的应用(见TI达芬奇技术实现数字化智能视频监控

本文重点介绍ADI公司在智能监控领域的进展情况。

本月初,笔者有幸和ADI上海公司的DSP和嵌入式处理器产品技术市场经理张铁虎、EP/DSP高级技术应用工程师魏宏伟两位先生进行了交流。

他们介绍了ADI公司DSP智能监控技术、战略特点和计划等,在此向21IC用户做个汇报。

虽然总体来说ADI公司DSP的名气不如TI的大,但该公司对DSP应用于智能视频监控相当重视。

从产品角度来讲,ADI公司主要业务有三:

模拟产品、MEMS和DSP。

其中DSP应用包括工业测控、移动媒体和汽车电子,而监控则占据ADI工业测控业务的大部分。

可见,智能监控对于ADI的DSP业务发展十分重要。

据张铁虎介绍,ADI的DSP发展历程虽然不如TI的悠久,但拥有自己明显的特点或优势。

首先,ADI的DSP架构和TI的不同。

TI的DSP实际上是ARM+DSP,所以需要两套开发工具。

ADI的DSP是基于1999年与Intel公司合作开发的MicroSignalArchitecture(微信号架构),称作convergentprocessor,在一个核里既有数字信号处理功能,又有MCU功能,所以只需一套开发工具,为用户使用、学习提供了方便。

其次,ADI的DSP开发工具是免费的,可在该公司网站上随时下载。

据第三方评测机构BDTI称,ADI的DSP具有最高的性价比。

此外,ADI的DSP还具有功耗低、稳定(工业/汽车级DSP工作温度范围为-40至+85摄氏度)的优点。

ADI公司在智能视频监控方面的市场策略比较独特。

有一些第三方设计单位为用户提供解决方案。

尤其是,ADI同许多科研院所(如清华大学)进行合作,共同展开视频分析的开发工作。

视频智能分析算法属于前沿技术,挑战性很强,而科研院所内的智力资源比较丰富,非常适合做这方面的研究。

目前,ADI公司的一些DSP智能视频监控已经走向实际应用。

在印度,人头清点(peoplecounting)系统已经实现量产;在美国,车牌识别系统实现了小批量应用;在中国,人脸识别也实现了小批量应用。

张铁虎介绍说,现在智能视频监控还主要应用在对安全要求很高的场合,如银行、监狱、水厂、政府机关等。

随着技术的发展、成本的降低,智能视频监控将越来越普及,更广泛地取代传统的CCTV。

张铁虎说,ADI公司非常看好智能监控市场,在这方面将持续投资,并在全球范围内同设计公司、科研院所展开合作开发。

DSP技术也是ADI的长期计划,目前该公司正在设计下一代的指令集,并已经完成了其中一部分。

ADI的DSP会特别注重视频分析,并为这方面的客户提供参考设计、算法模块等。

关于DSP核FPGA的竞争问题,张铁虎说,DSP更适合视频分析,而FPGA的长处是并行处理。

另外,FPGA还存在体积大、功耗大、价格高等问题。

不过,根据BDTI的报告,FPGA正越来越多地涉入DSP的应用领域。

在现今的很多设计中,DSP往往与FPGA配合使用。

在很多情形下,这一组合对于下一代系统的设计仍然适合。

但在另外一些情形下,设计者会考虑仅使用两者之一,而且通常是FPGA取代DSP的功能。

然而,对于智能视频监控市场,虽然FPGA也在试图进入,但就目前情况来看,DSP似乎是比较现实的解决方案。

基于DSP的语音实时变速系统设计

引言

在外语多媒体教学中,要求对语速进