数电实习报告三相步进电机控制器设计.docx

《数电实习报告三相步进电机控制器设计.docx》由会员分享,可在线阅读,更多相关《数电实习报告三相步进电机控制器设计.docx(14页珍藏版)》请在冰豆网上搜索。

数电实习报告三相步进电机控制器设计

三相步进电机控制器设计

一、设计任务及要求:

设计任务:

1、输入信号:

四个控制开关S1、S2、S3(开关拨下时S=0,开关拨上时S=1,)和一个外部的时钟源。

其中:

(1)、系统上电后,若S1=1,S2=1时,电机停止转动,步数清零(三个8421BCD数码管显示为000);

(2)、系统上电后,若S1=X(无关项),S2=0时,电机停止转动,步数显示保持(即暂停);

(3)、系统上电后,若S1=0,S2=1时,步进电机三相三拍转动1周(360度),转动完成后停止,停止以后再操作S1、S2、S3无效,直至重新上电后才能从头工作;

(4)、系统正常工作时,若S3=0时,步进电机正转,S3=1时,步进电机反转。

2、外部输入脉冲信号时钟源(50MHz),经分频后产生两路5Hz信号,供主控制器和步数计数器使用。

还要产生一个400Hz信号供三个7段数码管扫描显示使用。

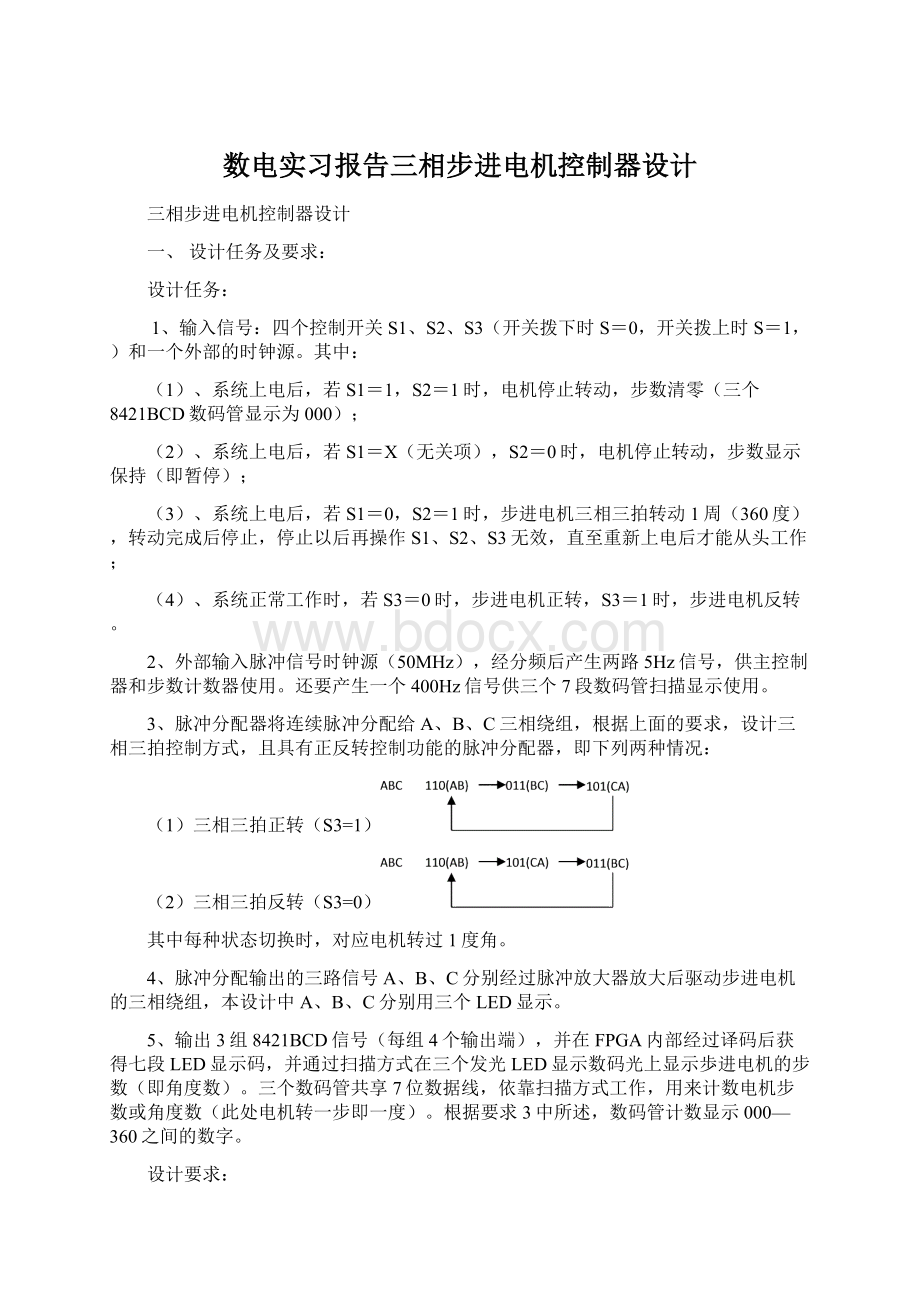

3、脉冲分配器将连续脉冲分配给A、B、C三相绕组,根据上面的要求,设计三相三拍控制方式,且具有正反转控制功能的脉冲分配器,即下列两种情况:

(1)三相三拍正转(S3=1)

(2)三相三拍反转(S3=0)

其中每种状态切换时,对应电机转过1度角。

4、脉冲分配输出的三路信号A、B、C分别经过脉冲放大器放大后驱动步进电机的三相绕组,本设计中A、B、C分别用三个LED显示。

5、输出3组8421BCD信号(每组4个输出端),并在FPGA内部经过译码后获得七段LED显示码,并通过扫描方式在三个发光LED显示数码光上显示歩进电机的步数(即角度数)。

三个数码管共享7位数据线,依靠扫描方式工作,用来计数电机步数或角度数(此处电机转一步即一度)。

根据要求3中所述,数码管计数显示000—360之间的数字。

设计要求:

1、按照现代数字系统的Top-Down模块化设计方法,提出步进电机控制系统的整体设计方案,并进行正确的功能划分,分别提出并实现主控制器、分频器、步数计数器、扫描显示译码模块等四部分模块化子系统的设计方案。

2、在Quartus的EDA设计环境中,采用原理图和Verilog语言混合输入的方法,完成系统的顶层设计、各子系统的模块化设计。

分别完成各个基于Verilog语言实现的子模块(包括分频器、步数计数器、主控制器、扫描显示译码四部分)的逻辑功能仿真,并对顶层设计进行功能和时序仿真。

3、在2步的基础上,采用Altera公司的CPLD器件EP1C12F324C8对顶层设计进行适配(FitDesign),生成下载文件。

4、采用DownLoad软件将设计的JED文件烧录到试验板的芯片上,实际测试。

二、设计原理与方案:

(一)、顶层设计方案:

设计原理图如下所示:

该控制器共含有四大部分:

主控制器、步数计数器、译码扫描显示电路、分频器。

分频器由时钟源输入50MHz的脉冲,经过分频器可分频为5Hz和400Hz频率的脉冲,输入给下一级电路。

主控制器部分根据外部输入的控制按键控制电机的转动方向,根据输入的脉冲控制电机的转动频率,并显示相序的变化。

同时向步数计数器输出控制数值,以使步数计数器与主控器同步。

另外在主控制器中还应有一个控制端来接收计数器的反馈,使电机在转动360度后能够停止转动。

计数器部分根据分频器输入的脉冲数进行计数,并由主控制器的输出来控制其是否计数以及清零、暂停等功能。

同时当记数到360步后反馈给主控制器一个控制值使其控制电机停止转动。

将计数的数值输出给译码扫描电器。

译码扫描电路中由分频器的400Hz脉冲控制数码管的扫描频率。

根据计数器的数值通过4-7译码器显示到数码上。

(二)、控制器设计方案:

设计思路:

控制器共有五个输入端口,分别为Clk、s1、s2、s3、k。

Clk为脉冲输入端口。

Clk为输入脉冲,为5Hz,由分频器输入。

k为计数器的返回值,在步数达到360时,该值有效,电机停转。

s1、s2、s3为三个控制键的输入在不同的情况下执行不同的动作,如下:

(1)、系统上电后,若S1=1,S2=1时,电机停止转动,步数清零;

(2)、系统上电后,若S1=X(无关项),S2=0时,电机停止转动,步数显示保持(即暂停);

(3)、系统上电后,若S1=0,S2=1时,步进电机三相三拍转动1周(360度),转动完成后停止,停止以后再操作S1、S2、S3无效,直至重新上电后才能从头工作;

(4)、系统正常工作时,若S3=0时,步进电机正转,S3=1时,步进电机反转。

控制器共有四个输出端口,分别为xiang、key1、key2、key3。

key1、key2、key3控制计数器与电机同步计数和清零。

xiang为三个相位的输出。

主控器程序如下:

modulekongzhiqi(clk,s1,s2,s3,k,xiang,key1,key2,key3);

inputclk,s1,s2,s3,k;

output[2:

0]xiang;

outputkey1,key2,key3;

regkey1,key2;

reg[2:

0]xiang;

reg[2:

0]state;

reg[1:

0]i=2'd0;

always@(posedgeclk)

beginif(s1==1&&s2==1)

beginkey1<=1'b0;key2<=1'b0;end

elseif(s1==1&&s2==0)

beginkey1<=1'b1;key2<=1'b0;end

elseif(s1==0&&s2==0)

beginkey1<=1'b1;key2<=1'b0;end

elseif(s1==0&&s2==1)begin

if(k==1)

beginkey1<=1'b1;key2<=1'b1;xiang=xiang;end

elsebegin

i=(i==2'd3)?

0:

(i+2'd1);

case(i)

2'd0:

beginkey1<=1'b1;key2<=1'b1;xiang=3'b110;end

2'd1:

beginkey1<=1'b1;key2<=1'b1;xiang=(s3==1'd0)?

3'b011:

3'b101;end

2'd2:

beginkey1<=1'b1;key2<=1'b1;xiang=(s3==1'd0)?

3'b101:

3'b011;end

endcase

end

end

end

assignkey3=s3;

endmodule

分频器程序如下:

modulefenpin(Clk,pin5,pin400

);

inputClk;

outputpin5;

outputpin400;

reg[31:

0]Cout1;

reg[31:

0]Cout2;

regClk_En1;

regClk_En2;

always@(posedgeClk)

begin

Cout1<=(Cout1==32'd10000_000)?

32'd0:

(Cout1+32'd1);

Clk_En1<=(Cout1==32'd10000_000)?

1'd1:

1'd0;

end

always@(posedgeClk)

begin

Cout2<=(Cout2==32'd125_000)?

32'd0:

(Cout2+32'd1);

Clk_En2<=(Cout2==32'd125_000)?

1'd1:

1'd0;

end

assignpin400=Clk_En2;

assignpin5=Clk_En1;

endmodule

(三)、受控器设计方案:

受控器有步数计数器和译码扫描器两个。

(1)、步数计数器由主控器控制,有四个输入端,分别为Clk、key1、key2、key3。

Clk为输入脉冲,为5Hz,由分频器输入,与主控器同频。

key1、key2、key3为三个控制键的输入在不同的情况下执行不同的动作,如下:

、key1=0,key2=0或key2=1时,步数为零;

、key1=1,key2=1时,步数在脉冲上升沿时加一;

、key1=1,key2=0时,步数保持上一次的数值;

在程序中,添加变量w1、w2,判断key3的值是否与上次的不同,不同则说明电机转向改变,执行步数清零,重新计数。

输出变量k,当计数达到360步时,添加if语句使k值会由原来的0变为1,计数停止,并且根据k值为1使计数在此后都不计数。

步数计数器有四个输出端,分别为bushu1、bushu2、bushu3,k。

bushu1、bushu2、bushu3为步数的8421BCD码,每一个数都是一个4位的二进制数,输出给译码扫描器。

k就是反馈到主控器中的变量。

(2)、译码扫描器由步数计数器控制,有四个输入端,分别为Clk,bushu1、bushu2、bushu3。

bushu1、bushu2、bushu3由步数计数器输入,经过4-7译码器后将译码后的7位二进制数赋值给7位的数码管。

Clk由分频器产生,经过再分频后,对应输出端的del,对8个数码管进行扫描,使每个管显示不同数值。

译码扫描器有两个输入端shumaguan,del。

shumaguan为7位数值对应电路板上的数码管的7段显示。

del端对应电路板上的3-8译码器的3个输入端,对数码管扫描。

步数计数器程序如下:

modulejishu(Clk,key1,key2,key3,bushu1,bushu2,bushu3,k

);

inputClk,key1,key2,key3;

outputk;

output[3:

0]bushu1;

output[3:

0]bushu2;

output[3:

0]bushu3;

regw1,w2,k;

reg[3:

0]bushu1;

reg[3:

0]bushu2;

reg[3:

0]bushu3;

always@(posedgeClk)

begin

w2=key3;

if(w2!

=w1)

beginbushu1=4'b0000;bushu2=4'b0000;bushu3=4'b0000;end

beginif(bushu1!

=4'b0||bushu2!

=4'd6||bushu3!

=4'd3)

if(k==0)

begink=0;

case(key1)

1'b0:

begincase(key2)

1'b0:

beginbushu1=4'b0000;bushu2=4'b0000;bushu3=4'b0000;end

1'b1:

beginbushu1=4'b0000;bushu2=4'b0000;bushu3=4'b0000;end

endcase

end

1'b1:

begin

if(key2==1'b1)

beginbushu1=(bushu1==4'b1001)?

4'b0:

(bushu1+4'b1);

if(bushu1==4'b0)

bushu2=(bushu2==4'b1001)?

4'b0:

(bushu2+4'b1);

if(bushu2==4'b0&&bushu1==4'b0)

bushu3=bushu3+4'b1;

w1=key3;

end

elsebeginbushu1=bushu1;bushu2=bushu2;bushu3=bushu3;end

end

endcase

end

if(bushu1==4'b0&&bushu2==4'd6&&bushu3==4'd3)

beginbushu1=4'b0000;bushu2=4'b0110;bushu3=4'b0011;k<=1'b1;end

end

end

endmodule

译码扫描器程序如下:

moduleyima(Clk,shumaguan,bushu1,bushu2,bushu3,del);

inputClk;

input[3:

0]bushu1;

input[3:

0]bushu2;

input[3:

0]bushu3;

output[2:

0]del;

output[6:

0]shumaguan;

reg[6:

0]shuzhi;

reg[2:

0]i;

always@(posedgeClk)

begin

i<=(i==3'b010)?

3'b0:

(i+3'b001);

end

always@(i)

case(i)

3'b000:

case(bushu1)

4'b0000:

shuzhi<=7'b0111_111;

4'b0001:

shuzhi<=7'b0000_110;

4'b0010:

shuzhi<=7'b1011_011;

4'b0011:

shuzhi<=7'b1001_111;

4'b0100:

shuzhi<=7'b1100_110;

4'b0101:

shuzhi<=7'b1101_101;

4'b0110:

shuzhi<=7'b1111_101;

4'b0111:

shuzhi<=7'b0000_111;

4'b1000:

shuzhi<=7'b1111_111;

4'b1001:

shuzhi<=7'b1101_111;

endcase

3'b001:

case(bushu2)

4'b0000:

shuzhi<=7'b0111_111;

4'b0001:

shuzhi<=7'b0000_110;

4'b0010:

shuzhi<=7'b1011_011;

4'b0011:

shuzhi<=7'b1001_111;

4'b0100:

shuzhi<=7'b1100_110;

4'b0101:

shuzhi<=7'b1101_101;

4'b0110:

shuzhi<=7'b1111_101;

4'b0111:

shuzhi<=7'b0000_111;

4'b1000:

shuzhi<=7'b1111_111;

4'b1001:

shuzhi<=7'b1101_111;

endcase

3'b010:

case(bushu3)

4'b0000:

shuzhi<=7'b0111_111;

4'b0001:

shuzhi<=7'b0000_110;

4'b0010:

shuzhi<=7'b1011_011;

4'b0011:

shuzhi<=7'b1001_111;

default:

shuzhi<=7'b0000_000;

endcase

default:

shuzhi<=7'b0111111;

endcase

assignshumaguan=shuzhi;

assigndel=i;

endmodule

三、电路设计、仿真与实现:

(一)、顶层设计实现:

顶层电路图如下:

图1.1顶层电路图

总程序的RTL视图:

图1.2顶层电路RTL视图

总程序的technology视图:

图1.3顶层电路technology视图

总程序仿真波形如下:

图2.1总程序仿真波形1

该波形为s1为0,s2为1,s3为0时产生的,相序显示为正转,数码管计数并且到360后停止计数保持。

(二)、控制器设计实现:

分频器的RTL视图

图1.4分频器的RTL视图

主控制器的RTL视图

图1.5主控制器的RTL视图

主控器的technology视图

图1.6主控器的technology视图

主控制器的仿真波形

图2.2主控制器的仿真波形1

该波形为s1为0,s2为1,s3为0时的主控制器波形,相序显示为正转,当k变为1是相序保持。

(三)、受控器设计实现:

步数计数器的RTL视图

图1.7步数计数器的RTL视图

步数计数器的仿真波形:

图2.3步数计数器的仿真波形

该波形为key1为1,key2为1时,步数计数,当key3变为1时,步数清零重新计步。

译码扫描器的RTL视图

图1.8译码扫描器的RTL视图

(四)、FitDesign结果;实际DownLoad及测试结果。

程序下载到电路板上,结果符合要求。

当对按键无操作时,数码管显示0,相序灯前两个亮。

当按下s1时,数码管从0开始计数,相序按反向顺序闪亮。

此时按下s2计数保持,相序保持。

当数码管计到360时,计数停止,相序停止。

当按下s1和s3时,数码管同上,相序顺序按正向闪亮,

当按下s1后一段时间,再按s3时,计数器会清零重新计数。

表示转向发生变化。

四、分析与讨论: