MSP430学习笔记.docx

《MSP430学习笔记.docx》由会员分享,可在线阅读,更多相关《MSP430学习笔记.docx(18页珍藏版)》请在冰豆网上搜索。

MSP430学习笔记

msp430c程序总结

MSP4302008-08-2219:

39:

26阅读237评论0字号:

大中小

在程序中使用的P5DIR、P5OUT、BIT1等的含义非常明显:

P5DIR就是端口P5的输入输出方向寄存器,P5OUT就是端口P5的输出寄存器,BIT1就是一个数据的位1(由位0开始),P5OUT^=BIT1的含义就是P5OUT.1求反。

WDTCTL=WDTPW+WDTHOLD;//关闭看门狗

WDTCTL=WDTPW;//起动看门狗

WDTCTL=WDTPW+WDTCNTCL;//计数器清零

P5DIR|=0x0F;//设置P5.0-P5.3为输出方向

P1DIR=0x0F;//设置P1.4-P1.7为输入方向

P1IE=0xf0;//设置P1.4-P1.7可以中断

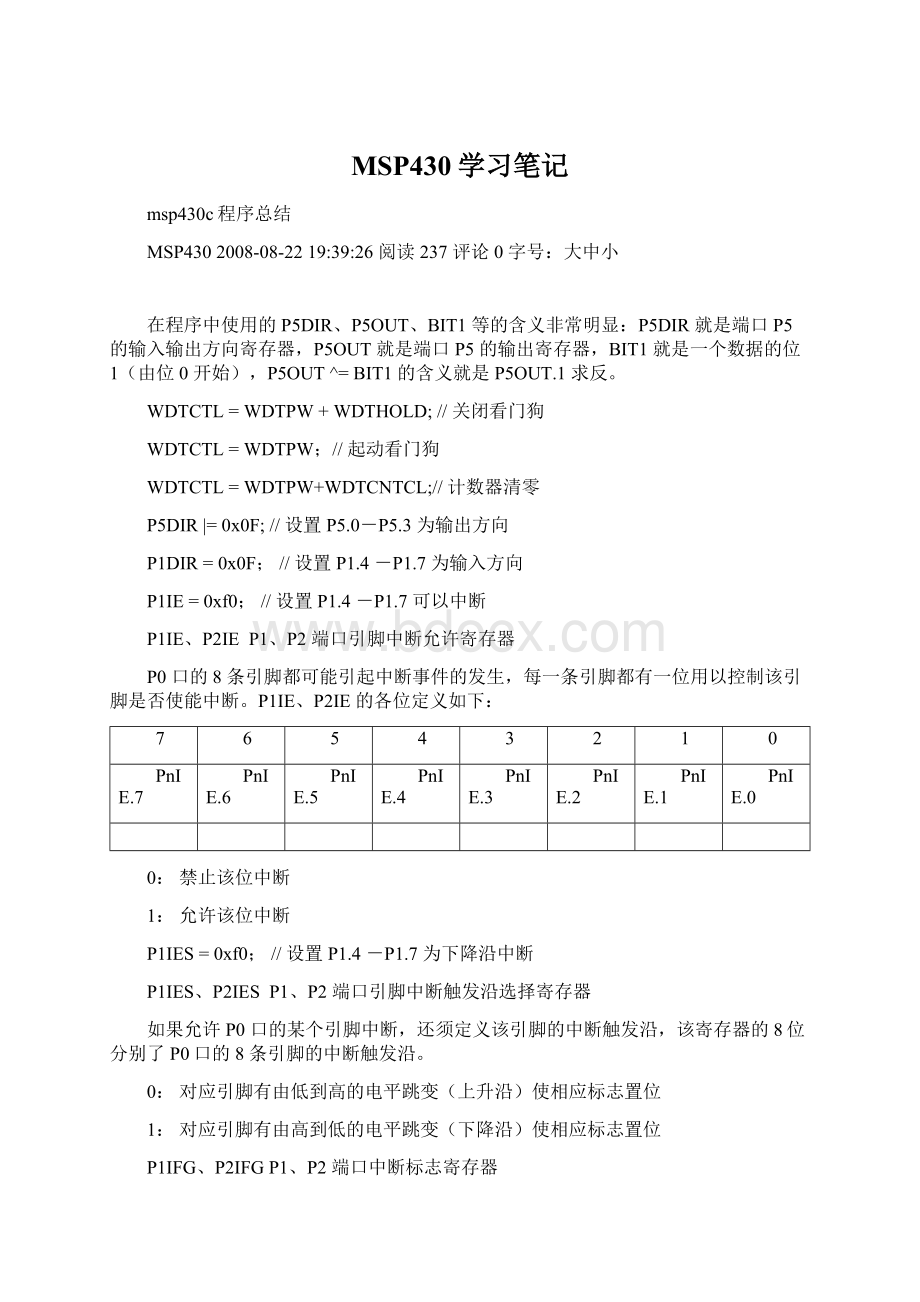

P1IE、P2IE P1、P2端口引脚中断允许寄存器

P0口的8条引脚都可能引起中断事件的发生,每一条引脚都有一位用以控制该引脚是否使能中断。

P1IE、P2IE的各位定义如下:

7

6

5

4

3

2

1

0

PnIE.7

PnIE.6

PnIE.5

PnIE.4

PnIE.3

PnIE.2

PnIE.1

PnIE.0

0:

禁止该位中断

1:

允许该位中断

P1IES=0xf0;//设置P1.4-P1.7为下降沿中断

P1IES、P2IES P1、P2端口引脚中断触发沿选择寄存器

如果允许P0口的某个引脚中断,还须定义该引脚的中断触发沿,该寄存器的8位分别了P0口的8条引脚的中断触发沿。

0:

对应引脚有由低到高的电平跳变(上升沿)使相应标志置位

1:

对应引脚有由高到低的电平跳变(下降沿)使相应标志置位

P1IFG、P2IFGP1、P2端口中断标志寄存器

该寄存器有6个标志位,它们含有相应引脚是否有待处理中断的信息,或相应引脚是否与中断请求。

如果P1、P2口的某个引脚允许中断,同时选择上升沿,当在该引脚发生电平由低向高跳变时,P1IFG或P2IFG的相应位就会置位,表明在该引脚上有中断事件发生。

8个标志位分别对应8位,如下所示。

7

6

5

4

3

2

1

0

PnIFG.7

PnIFG.6

PnIFG.5

PnIFG.4

PnIFG.3

PnIFG.2

PnIFG.1

PnIFG.0

0:

没有中断

1:

有中断请求。

P1SEL、P2SELP1、P2功能选择寄存器

P1、P2两端口还有其它片内外设功能,考虑减少引脚,将这些功能与芯片外的联系通过复用P1、P2引脚的方式以实现。

P1SEL、P2SEL用来选择引脚的I/O(输入/输出)端口功能与外围模块功能。

0:

选择引脚为I/O端口

1:

选择引脚为外围模块功能

TACTL为最主要的控制寄存器,它决定TA的输入时钟信号、TA的工作模式、TA的开启与停止、中断的申请等工作。

TACTL寄存器为16位寄存器,必须使用字指令对其访问。

该寄存器在POR信号后全部复位,但在PUC信号后不受影响。

该寄存器中各位的含义:

15~10

9

8

7

6

5

4

3

2

1

0

未用

SSEL1

SSEL0

ID1

ID0

MC1

MC0

未用

CLR

TAIE

TAIFG

SSEL1、SSEL0选择输入分频器的输入时钟源。

SSEL1 SSEL0输入信号输入信号说明

0 0 TACLK使用外部引脚信号作为输入

0 1 ACLK辅助时钟

1 0 MCLK系统主时钟

1 1 INCLK外部输入时钟(见芯片手册)

ID1、ID0选择输入分频器的分频系数。

00:

直通,不分频

01:

1/2分频

10:

1/4分频

11:

1/8分频

MC1、MC0选择定时器模式

00:

停止模式,用于定时器暂停

01:

增计数到CCR0模式,该模式下,计数器计数到CCR0,再清零计数

10:

连续增计数模式,计数器增计数到“FFFFH”,再清零计数

11:

增/减模式,增计数到CCR0,再减计数到0

CLR定时器清除位,计数器内容清零

TAIE中断允许位,该位允许定时器溢出中断

TAIFG定时器溢出标志位,在不同的定时器模式下,该位置位条件不一样。

增计数模式:

当定时器由CCR0计数到“0”时TAIFG置位

连续模式:

当定时器由0FFFFH计数到“0”时TAIFG置位

增/减模式:

当定时器由“1”减计数到“0”时TAIFG置位

由此可见TACTL寄存器几乎控制了Timer_A的第一部分——计数器部分。

下面我们对照原理图理解。

工作模式控制如图2.11.5。

由MC1、MC0两位选择。

图2.11.5

TACTL|=MC0;//以增计数模式开始Timer_a

_EINT();

for(;;)

{

-BIS-SR(LPM3-bits);//-BIS-SR(CPUOFF)

-NOP();

}

1.#pragmavector=TIMERA0-VECTOR/WDT-VECTOR

-interruptvoidTimer-A(void)/watchdog-timer(void)

{

P1OUT^=ox01;

}

2.interrupt[WDT-VECTOR]voidwatchdog-timer(void)

{

P1OUT^=ox01;

}

CCTL1=OUTMOD_7PWM复位/置位

BCSCTL1&=~XT2OFF;//打开XT2振荡器

IFG1&=~OFIFG;//清除振荡器失效标志

BCSCTL1基准时钟系统控制寄存器1

7

6

5

4

3

2

1

0

XT2OFF

TXS

DIVA.1

DIVA.0

XT5V

RESEL.2

RESEL.1

RESEL.0

XT2OFF控制振荡器的开启与关闭

XT2OFF=0振荡器开启

XT2OFF=1振荡器关闭

TXS控制LFXT1工作模式,选择需结合实际晶体振荡器连接情况。

XTS=0,LFXT1工作在低频模式(默认)

XTS=1,LFXT1工作在高频模式(必须连接有高频相应的高频钟源)

DIVA.1,DIVA.0控制分频

0 不分频

1 2分频

2 4分频

3 8分频

XT5V此位设置为0

RESEL.0,RESEL.1,RESEL.2三位控制某个内部电阻以决定标称率。

RESEL=0选择最低的标称频率

………

RESEL=7选择最高的标称频率

BCSCTL2基准时钟系统控制寄存器2

7

6

5

4

3

2

1

0

SELM.1

SELM.0

DIVM.1

DIVM.0

SELS

DIVM.1

DIVM.0

DCOR

SELM.1SELM.0选择MCLK时钟源

0时钟源为DCOCLK(默认)

1时钟源为DCOCLK

2时钟源为LFXT1CLK(MSP430F11/12X),时钟源为XT2CLK(MSP430F13/14/15/16X)

3时钟源为LFTXTICLK

DIVM.1,DIVM.0选择MCLK分频

0 不分频(默认)

1 2分频

2 4分频

3 8分频

SELS选择SMCLK时钟源

0时时钟源LFTXTICLK

1时时钟源时钟源为LFXT1CLK(MSP430F11/12X),时钟源为XT2CLK(MSP430F13/14/15/16X)

DIVS.1,DIVS.0选择SMCLK分频

0 不分频(默认)

1 2分频

2 4分频

3 8分频

DCOR选择DCO电阻

0内部电阻

1外部电阻

ADC12CTL0转换控制寄存器0

15—12

11—8

7

6

5

4

3

2

1

0

SHT1

SHT0

MSC

2.5V

REFON

ADC

12ON

ADC

12TOVIE

ADC

12TVIE

ENC

ADC

12SC

在不同条件ADC12SC的含义

NC=1

SHP=1

ADC12SC由0变为1启动转换

AD转换完成后自动复位

ISSH=0

SHP=0

ADC12SC保持高电平时采集

ADC12SC复位时启动一次转换

ENC=1表示转换允许;ISSH=0表示采样输入信号为同相输入;SHP=1表示采样信号SAMPCON来源于采样定时器;SHP=0表示采样直接由ADC12SC控制。

使用ADC12SC时,需注意以上表格信号的匹配。

用软件启动一次AD转换,需要使用一条指令来完成ADC12与ENC的设置。

ENC转换允许位

0 ADC12为初始状态,不能启动AD转换

1首次转换由SAMPCON上沿启动

只有在该位为高电平时,才能用软件或外部启动转换。

在不同转换模式,ENC由高电平变为低电平的影响不同:

当CONSEQ=0(单通道单次转换模式)且ADC12BUSY=1(ADC12处于采样或者转换)时,中途撤走ENC信号9高电平变为低电平),则当前操作结束,并可能得到错误结果。

所以在单通道单次转换模式整个过程中,都必须保证ENC信号有效。

当CONSEQ=0(非单通道单词转换)时,ENC由高电平变为低电平,则当前转换正常结束,且转换结束有效,在当前转换结束时停止操作。

ADC12TVIE转换时间溢出中断允许位

0没有发生转换时间溢出

1发生转换时间溢出

当前转换还没有完成时又发生了一次采样请求,则会发生转换时间溢出。

如果允许中断,则会发生中断请求。

多次采样/转换位

ADC12OVIE溢出中断允许位

0没有发生溢出

1发生溢出

当ADC12MEMx中原有的数据还没有被读出,而现在又有新的转换结果数据要写入时,则会发生溢出。

如果相应的中断允许。

则会发生中断请求。

ADC12ON ADC12内核控制位

0关闭ADC12内核

1打开ADC12内核

REFON参考电压控制位

0内部参考电压发生器关闭

1内部参考电压发生器打开

2.5V内部参考电的电压值选择位

0选择1.5V内部参考电压

1选择2.5V内部参考电压

MSC多次采样/转换位

有效条件

MSC值

含义

SHP=1

0

每次转换需要信号的上升沿触发采集定时器

CONSE!

=0

1

仅首次转换通信号的上升沿触发采样定时器,而后采样转换将在前一次转换完成立即进行

其中CONSE!

=0表示当前转换模式不是单通道单次转换。

SHT1,SHT0采集保持定时器1,采集保持定时器0,这是定义了每通道转换结果中的转换时序与采样时钟ADC12CLK的关系。

采样周期是ADC12CLK周期的整4倍,则:

Tsample=4*Tadc12clk*N

SHT1,SHT0采集保持定时器1,采集保持定时器0的分频因子

SHIx

0

1

2

3

4

5

6

7

8

9

10

11

12--15

N

1

2

4

8

16

24

32

48

64

96

128

192

256

ADC12CTL2

15-12

CSSTARTADD

11-10

SHS

9

SHP

8

ISSH

7-5

ADC12DIV

4,3

ADC12SEL

2,1

CONSEQ

0

ADC12BUSY

大多数位只有在ENC=0时才可被修改,如3-15位。

CSSTARTADD转换存储器地址位,这4位表示二进制数0-15分别对应ADC12MEM0-15。

可以定义单次转换地址或序列转换的首地址。

SHS采样触发输入源选择位

0 ADC12SC

1 Timer-A.OUT1

2 Timer-B.OUT0

3 Timer-B.OUT1

SHP采样信号(SAMPCON)选择控制位

0 SAMPCON源自采样触发输入信号

1 SAMPCON源自采样定时器,由采样信号的上升沿触发采样定时器

ISSH采样输入信号方向控制位

0采样输入信号位同向输入

1采样输入信号位反向输入

ADC12DIV ADC12时钟源分频因子选择位,分频因子为3位二进制数价1

ADC12SEL ADC12内核时钟源选择

0 ADC12内部时钟源:

ADC120SC

1 ACLK

2 MCLK

3 SMCLK

CONSEQ转换模式选择位

0单通道单次转换模式

1序列通道单次转换模式

2单通道多次转换模式

3序列通道多次转换模式

ADC12BUSY ADC12忙标志位

0表示没有活动的操作

1表示ADC12正处在采样期间,转换或序列转换期间。

ADC12BUSY只用于单通道单次转换模式,如果NEC复位则转换立即停止,转换结果不可靠,需要在时NEC=0之前,测试ADC12BUSY位以确定是否为0。

其它转换模式下此位是无效的

ADC12MEM0-ADC12MEM15转换存储器

15

14

13

12

11—0

0

0

0

0

MSB

LSB

这16位寄存器是用来存储AD转换结果,只用其中低12位,高四位在读出时为0。

ADC12MCTLX转换存储器控制寄存器

ADC12IFG中断标志寄存器

ADC12IE中断使能寄存器

ADC12IV中断向量寄存器

UxCTL控制寄存器

7

6

5

4

3

2

1

0

PENA

PEV

SPB

CHAR

LISTEN

SYNC

MM

SWRST

PENA校验允许位

0校验禁止

1校验允许

校验允许时,发送端发送校验,接收端接收该校验,地址位包含校验操作。

PEV奇偶校验位,该位在校验允许时有效

0奇有效

1偶有效

SPB停止位选择。

决定发送的停止唯书,但接收时接收器只检测1位停止位。

0 1位停止位

1 2位停止位

CHAR字符长度

0 7位

1 8位

LISTEN反馈选择。

选择是否发送数据由内部反馈给接收器

0无反馈

1有反馈,发送信号有内部反馈接收器

SYNCUSART模块的模式选择

0 UART模式[异步]

1 SPI模式[同步]

MM多机模式选择

0 线路空闲多机协议

1 地址多机协议

SWRST控制位

上电时该位置位,此时USART状态极和运行标志初始化城复位状态。

(URXIFG=0,URXIE=0,UTXIE=0UTXIFG=1).所有受影响的逻辑保持在复位状态,直至SWRST复位。

也就是说一次系统复位后,只有对SWRST复位,USART才能重新被允许。

而接收和发送允许标志URXE和UTXE不会因SWRST而更改.

SWRST位会使URXIE、UTXIE、URXIFG、RXWAKE、TXWAKE、RXERR、BRK、PE、OE及FE等复位。

UCB0CTL1&=~UCSWRST; //进入I2C工作模

UCB0CTL1|=UCSSEL1;//时钟源选择smclk

SPI模式

UCAxCTL0,USCI_AxControlRegister0

UCBxCTL0,USCI_BxControlRegister0

7 6 5 4 3 2 1 0

UCCKPH

UCCKPL

UCMSB

UC7BIT

UCMST

UCMODEx

UCSYNC=1

rw-0 rw-0 rw-0 rw-0 rw-0 rw-0rw-0

UCCKPHBit7Clockphaseselect.

0DataischangedonthefirstUCLKedgeandcapturedonthe

followingedge.

1DataiscapturedonthefirstUCLKedgeandchangedonthe

followingedge.

UCCKPLBit6Clockpolarityselect.

0Theinactivestateislow.

1Theinactivestateishigh.

UCMSBBit5MSBfirstselect.Controlsthedirectionofthereceiveandtransmitshift

register.

0LSBfirst

1MSBfirst

UC7BITBit4Characterlength.Selects7-bitor8-bitcharacterlength.

08-bitdata

17-bitdata

UCMSTBit3Mastermodeselect

0Slavemode

1Mastermode

UCMODExBits

2-1

USCIMode.TheUCMODExbitsselectthesynchronousmodewhen

UCSYNC=1.

00 3-PinSPI

01 4-PinSPIwithUCxSTEactivehigh:

slaveenabledwhenUCxSTE=1

10 4-PinSPIwithUCxSTEactivelow:

slaveenabledwhenUCxSTE=0

11 I2CMode

UCSYNCBit0Synchronousmodeenable

0 Asynchronousmode

SynchronousMode

UCB0CTL1|=UCTR+UCTXSTT; //发送起始位,并将主机设为发送模式

UCAxCTL1,USCI_AxControlRegister1

UCBxCTL1,USCI_BxControlRegister1

7

6 5 4 3 2 1

0

UCSSELx

Unused

UCSWRST

rw-0

rw-0 rw-0 rw-0 rw-0 rw-0 rw-0

rw-1

UCSSELxBits

7-6

USCIclocksourceselect.ThesebitsselecttheBRCLKsourceclockinmastermode.UCxCLKisalwaysusedinslavemode.

00NA

01ACLK

10SMCLK

11SMCLK

UnusedBits5-1

Unused

UCSWRSTBit0Softwareresetenable

0 Disabled.USCIresetreleasedforoperation.

1 Enabled.USCIlogicheldinresetstate.

IE2|=UCB0TXIE; //使能UCB0TX发送中断

IE2,InterruptEnableRegister2

7

6

5

4

3

2

1

0

UCB0TXIE

UCB0RXIE

UCA0TXIE

UCA0RXIE

rw-0

rw-0

rw-0

rw-0

Bits 7-4

Thesebitsmaybeusedbyothermodules.Seedevice-specificdatasheet.

UCB0TXIEBit3USCI_B0transmitinterruptenable

0 Interruptdisabled

1 Interruptenabled

UCB0RXIEBit2USCI_B0receiveinterruptenable

0 Interruptdisabled

1 Interruptenabled

UCA0TXIEBit1USCI_A0transmitinterruptenable

0 Interruptdisabled

1 Interruptenabled

UCA0RXIEBit0USCI_A0receiveinterruptenable

0 Interruptdisabled

1 Interruptenabled

IFG2&=~UCB0TXIFG; //清发送标志位

IFG2,InterruptFlagRegister2

7 6 5 4 3 2 1 0

UCB0

RXIFG

UCB0

TXIFG

UCA0

TXIFG

UCA0

RXIFG

rw-1 rw-0 rw-1 rw-0

Bits7-4 Thesebitsmaybeusedbyothermodules.Seedevice-specificdatasheet.

UCB0TXIFG Bit3 USCI_B0transmitinterruptflag.UCB0TXIFGissetwhenUCB0TXBUFisempty.

0Nointerruptpending

1Interruptpending

UCB0RXIFG Bit2 USCI_B0receiveinterruptflag.UCB0RXIFGissetwhenUCB0RXBUFhas

receivedacompletecharacter.

0Nointerruptpending

1Interruptpending

UCA0TXIFG Bit1 USCI_A0tr