数字电子电路与逻辑 刘可文主编 第四章 集成逻辑门电路 答案.docx

《数字电子电路与逻辑 刘可文主编 第四章 集成逻辑门电路 答案.docx》由会员分享,可在线阅读,更多相关《数字电子电路与逻辑 刘可文主编 第四章 集成逻辑门电路 答案.docx(13页珍藏版)》请在冰豆网上搜索。

数字电子电路与逻辑刘可文主编第四章集成逻辑门电路答案

习题4

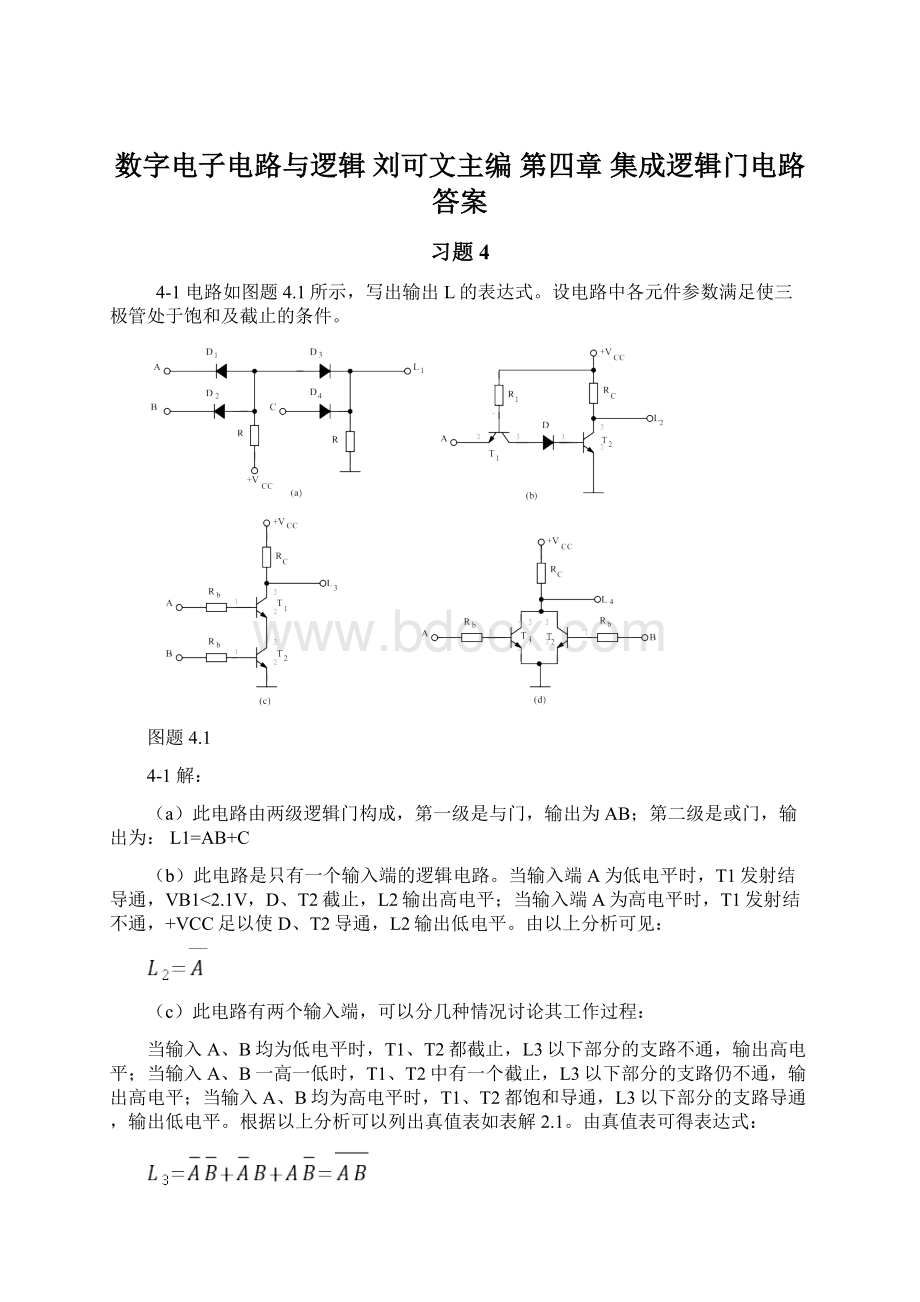

4-1电路如图题4.1所示,写出输出L的表达式。

设电路中各元件参数满足使三极管处于饱和及截止的条件。

图题4.1

4-1解:

(a)此电路由两级逻辑门构成,第一级是与门,输出为AB;第二级是或门,输出为:

L1=AB+C

(b)此电路是只有一个输入端的逻辑电路。

当输入端A为低电平时,T1发射结导通,VB1<2.1V,D、T2截止,L2输出高电平;当输入端A为高电平时,T1发射结不通,+VCC足以使D、T2导通,L2输出低电平。

由以上分析可见:

(c)此电路有两个输入端,可以分几种情况讨论其工作过程:

当输入A、B均为低电平时,T1、T2都截止,L3以下部分的支路不通,输出高电平;当输入A、B一高一低时,T1、T2中有一个截止,L3以下部分的支路仍不通,输出高电平;当输入A、B均为高电平时,T1、T2都饱和导通,L3以下部分的支路导通,输出低电平。

根据以上分析可以列出真值表如表解2.1。

由真值表可得表达式:

(d)此电路有两个输入端,可以分几种情况讨论其工作过程:

当输入A、B均为低电平时,T1、T2都截止,L4以下部分的支路不通,输出高电平;当输入A、B一高一低时,T1、T2中有一个饱和导通,L4以下部分的支路导通,输出低电平;当输入A、B均为高电平时,T1、T2都饱和导通,L4以下部分的支路导通,输出低电平。

根据以上分析可以列出真值表如表解4.1。

由真值表可得表达式:

表解2.1

A

B

L3

L4

0

0

1

1

0

1

0

1

1

1

1

0

1

0

0

0

图题4.5

4-2为什么说TTL与非门的输入端在以下4种接法下都属于逻辑0:

(1)输入端接地;

(2)输入端接低于0.8V的电源;(3)输入端接同类与非门的输出低电压0.3V;(4)输入端通过200Ω的电阻接地。

4-2解:

TTL与非门的输入端接地、接低于0.8V的电源、接同类与非门的输出低电压0.3V时,输入电压均低于其关门电平VOFF(VOFF=1.3V),因此门的输出电压均高于其输出高电平的最小值VOH(min)(VOH(min)=2.4V),都属于高电平,所以以上三种输入的接法都属于逻辑0。

当输入端通过200Ω的电阻接地时,见图解4.2。

由电路分析得:

可见,输入电压小于关门电平,所以此种输入的接法也属于逻辑0。

图解4.2图解4.9

4-3为什么说TTL与非门的输入端在以下4种接法下,都属于逻辑1:

(1)输入端悬空;

(2)输入端接高于2V的电源;(3)输入端接同类与非门的输出高电压3.6;(4)输入端接10kΩ的电阻到地。

4-3解TTL与非门的输入端悬空时,对应T1管的发射结不通,VCC使T2、、T3管饱和导通,输出低电平,所以此时相当于输入逻辑1。

TTL与非门的输入端接高于2V的电源、接同类与非门的输出高电压3.6V时,输入电压均高于其开门电平VON(VON略大于1.3V),因此门的输出电压均低于其输出低电平的最大值VOL(max)(VOL(max)=0.4V),都输出低电平,所以以上两种输入的接法都属于逻辑1。

当输入端接10kΩ的电阻到地时,见图解4.2。

可见,输入电压高于开门电平,所以此种输入的接法也属于逻辑1。

但要注意的是,在这种输入的作用下,会使T1的集电结正偏导通、T2、T3管饱和导通,VB1=2.1V。

而R的存在致使T1的发射结也是导通的,所以输入电压Vi最终被钳制在1.4V上。

4-4某TTL反相器的主要参数为IIH=20μA,IIL=1.4mA;IOH=400μA;IOL=14mA,求它能带多少个同样的门。

4-4输出低电平时的扇出系数:

NOL=10。

输出高电平时的扇出系数:

NOH=20。

取两者中的较小值作为门电路的扇出系数,用NO表示:

NO=10。

4-5电路如图题4.5所示,写出输出L的表达式。

4-5解

4-6在图题4.6所示的TTL门电路中,要求实现下列规定的逻辑功能时,其连接有无错误?

如有错误请改正。

(a)(b)(c)

图题2.6

图题4.6

4-6解:

(a)有错误。

普通门电路不允许输出端直接相连,应将图中的逻辑门改为OC门。

(b)正确。

图中第二个门是同或门,同或表达式:

。

当同或门一端接VCC时,相当于输入1,这时输出信号与另一输入信号是相等的。

由图题2.6(b)可见,它可以实现

。

(c)有错误。

正确的连接请见图解2.6。

图解4.6图解4.8

*讨论:

异或和同或是数字电路中常见的逻辑关系。

其逻辑表达式如下:

异或:

当C=0时,L=D。

当C=1时,

。

同或:

当C=0时,

。

当C=1时,L=D。

4-7在图题4.7中Gl为TTL三态与非门,G2为TTL普通与非门,电压表内阻为100kΩ.试求下列四种情况下的电压表读数和G2输出电压VO值:

(1)B=0.3V,开关K打开;

(2)B=0.3V,开关K闭合;

(3)B=3.6V,开关K打开;

(4)B=3.6V,开关K闭合;

图题4.7

4-7

(1)B=0.3V,三态与非门处于工作状态,电压表读数:

3.6V;开关K打开,G2门输入端悬空相当于输入高电平,输出电压:

VO=0.3V。

(2)B=0.3V,三态与非门处于工作状态,电压表读数:

3.6V;开关K闭合,G2门输入高电平,输出电压:

VO=0.3V。

(3)B=3.6V,三态与非门处于高阻态,又知开关K打开,可见电压表读数:

0V;G2门输入端悬空相当于输入高电平,输出电压:

VO=0.3V。

(4)B=3.6V,三态与非门处于高阻态,又知开关K闭合,此时G2门输入端的情况

如图解4.2所示。

其输入电压:

显然G2门输入高电平,这使得输出电压:

VO=0.3V;而G2门中T1的集电结和T2、T3的发射结这三个串联的PN结导通,VB1=2.1V,而电压表读数为:

VB1-0.7V=1.4V。

4-8在图题4.8中,所有的门电路都为TTL门,设输入A、B、C的波形如图4.8(d)所示,试定量画出各输出的波形图。

图题4.8

4-8解:

分析图题2.8中各电路的逻辑关系:

图(a):

。

图(b):

。

图(c):

其中的第一个门是低电平有效的三态与非门。

当C=0时,三态门输出为

,

。

当C=1时,三态门处于高阻态,对于后一级与门来说相当于输入1,所以L3=A。

根据以上分析,可以画出各电路的输出波形,如图解4.8所示。

*讨论:

画组合逻辑电路的工作波形时要注意:

首先分析电路的逻辑关系,写出表达式,不必列真值表。

然后依据表达式体现的逻辑关系画出波形。

画波形时可以根据输入信号的变化分段处理,并要注意将输入与输出波形在时间坐标上对应起来。

4-9用OC门实现逻辑函数

,画出逻辑电路图。

4-9用OC门实现逻辑函数

的逻辑电路如图解4.9所示。

4-10电路如图题4.10所示,试用表格方式列出各门电路的名称,输出逻辑表达式以及当ABCD=1001时,各输出函数的值。

图题4.10

4-10解答见表解4.10。

表解4.10

门电路的名称

输出逻辑表达式

ABCD=1001时,各输出函数值

同或门

L1=0

与或非门

L2=0

OC门

L3=0

三态与非门

B=0时

B=1时

B=0L4=1

4-11写出图题4.11所示电路的逻辑表达式。

4-11解:

图题4.11所示为NMOS逻辑电路。

其表达式:

4-12写出图题4.12所示电路的逻辑表达式。

4-12解:

图题4.2所示为CMOS逻辑电路。

其表达式:

4-13列出图题4.13所示电路的真值表。

图题4.11

图题4.12

4-13图题4.13(a)电路的真值表如表解4.13(a)所示;图题4.13(b)电路的真值表如表解4.13(b)所示。

表解4.13(a)表解4.13(b)

C

A

B

L1

1

0

0

1

0

1

0

1

0

0

1

1

0

0

×

高阻

B

A

L2

0

0

0

1

1

1

×

高

阻

4-14试设计一个NMOS异或门,画出逻辑电路图。

4-14解NMOS异或门电路的逻辑电路如图解4.14所示。

图解4.14图解4.15

4-15试设计一个CMOS门电路,实现逻辑关系L=AB+C,画出逻辑电路图。

4-15解实现逻辑关系L=AB+C的CMOS逻辑电路如图解4.15所示。

4-16试利用CMOS传输门设计一个CMOS三态输出的两输入端与非门,画出逻辑电路图并列出其真值表。

4-16解:

CMOS三态输出的两输入端与非门电路见图解4.16,真值表见表解4.16。

图中的与非门是典型的CMOS结构的电路,由CMOS传输门实现三态输出。

当控制端C为高电平时,传输门导通,电路实现与非功能;当控制端C为低电平时,传输门不通,输出呈现高阻。

表解4.16

C

A

B

L

1

0

0

1

0

1

1

1

0

1

1

1

0

0

×

高阻

图解4.16

4-17当TTL和CMOS两种门电路相互连接时,主要考虑哪几个电压和电流参数?

试列出这些参数,并对每一参数进行解释。

图题4.13

4-17解:

当TTL和CMOS两种门电路相互连接时,驱动门必须要为负载门提供符合要求的高低电平和足够的输入电流,即要满足下列条件:

驱动门的VOH(min)≥负载门的VIH(min)

驱动门的VOL(max)≤负载门的VIL(max)

驱动门的IOH(max)≥负载门的IIH(总)

驱动门的IOL(max)≥负载门的IIL(总)

其中,VOH(min)指输出高电平电压;VIH(min)指输入高电平电压;VOL(max)指输出低电平电压;VIL(max)指输入低电平电压;IOH(max)指输出高电平电流;IIH(总)指各负载门输入高电平电流IIH(max)的和;IOL(max)指输出低电平电流;IIL(总)指各负载门输入低电平电流IIL(max)的和。

4-18分析图题4.18所示电路,求输入S1、S0各种取值下的输出Y,填入表题4.18中。

图题4.18

4-18解:

在输入S1、S0各种取值下的输出Y见表解4.18。

表解4.18

输入

输出

S1

S0

Y

0

0

0

1

1

0

1

1

4-19设发光二极管的正向导通电流为10mA;与非门的电源电压为5V,输出低电平为0.3V,输出低电平电流为15mA,试画出与非门驱动发光二极管的电路,并计算出发光二极管支路中的限流电阻阻值。

4-19解:

与非门驱动发光二极管的电路如图解4.19所示。

发光二极管支路中的限流电阻阻值:

图解4.19

4-20电路如图题4.20所示,已知CMOS门电路的输出电压VOH=4.7V,VOL=0.1V,试计算接口电路的输出电压VO(三极管的集电极电位)。

并说明接口参数选择是否合理。

图题4.20

4.20当VOH=4.7V时:

因IB>IBS,所以三极管饱和:

Vo≈0.3V。

能够为TTL门提供合适的输入低电平。

当VOL=0.1V时:

因电压达不到发射结的门坎电压,所以三极管截止:

Vo=VCC-RC×4IIH=4.6V(取IIH=50μA)

可见,能够为TTL门提供合适的输入高电平。

由以上分析知,接口参数选择合理。