双通路信号源发生器设计程序.docx

《双通路信号源发生器设计程序.docx》由会员分享,可在线阅读,更多相关《双通路信号源发生器设计程序.docx(16页珍藏版)》请在冰豆网上搜索。

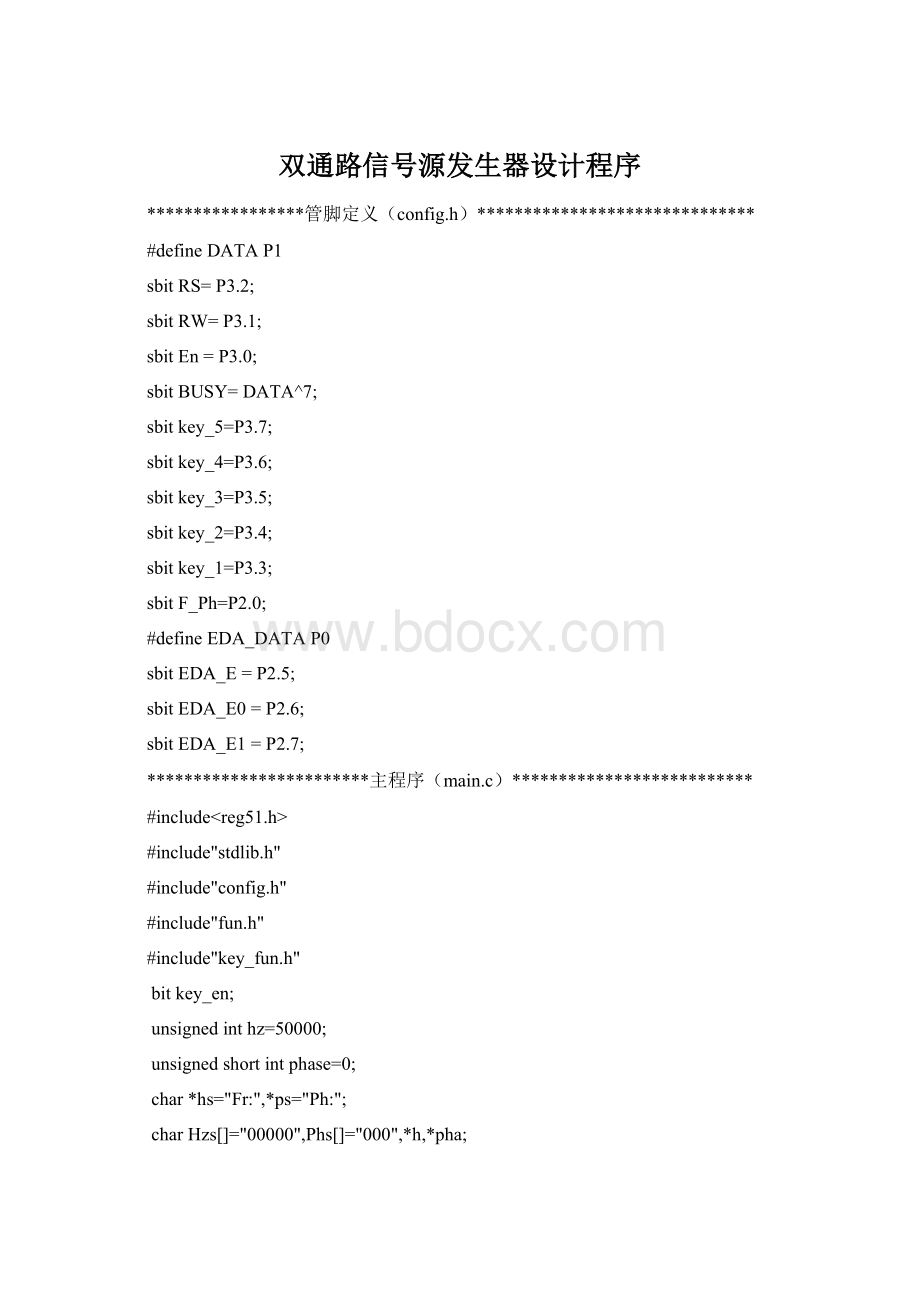

双通路信号源发生器设计程序

*****************管脚定义(config.h)******************************

#defineDATAP1

sbitRS=P3.2;

sbitRW=P3.1;

sbitEn=P3.0;

sbitBUSY=DATA^7;

sbitkey_5=P3.7;

sbitkey_4=P3.6;

sbitkey_3=P3.5;

sbitkey_2=P3.4;

sbitkey_1=P3.3;

sbitF_Ph=P2.0;

#defineEDA_DATAP0

sbitEDA_E=P2.5;

sbitEDA_E0=P2.6;

sbitEDA_E1=P2.7;

************************主程序(main.c)**************************

#include

#include"stdlib.h"

#include"config.h"

#include"fun.h"

#include"key_fun.h"

bitkey_en;

unsignedinthz=50000;

unsignedshortintphase=0;

char*hs="Fr:

",*ps="Ph:

";

charHzs[]="00000",Phs[]="000",*h,*pha;

voidsend_EDA_data(bita,bitb,intdat)

{

EDA_E0=a;

EDA_E1=b;

EDA_DATA=dat;

EDA_E=1;

EDA_E=0;

}

bitkey_fun()

{

bitz=0;

if(key_5==0&&key_4==1&&key_3==1&&key_2==1&&key_1==1&&F_Ph==1&&key_en==0)

{

key_en=1;

hz=hz-10000;

if(hz>50000)

hz=50000;

z=0;

}

if(key_5==1&&key_4==0&&key_3==1&&key_2==1&&key_1==1&&F_Ph==1&&key_en==0)

{

key_en=1;

hz=hz-1000;

if(hz>50000)

hz=50000;

z=0;

}

if(key_5==1&&key_4==1&&key_3==0&&key_2==1&&key_1==1&&F_Ph==1&&key_en==0)

{

key_en=1;

hz=hz-100;

if(hz>50000)

hz=50000;

z=0;

}

if(key_5==1&&key_4==1&&key_3==1&&key_2==0&&key_1==1&&F_Ph==1&&key_en==0)

{

key_en=1;

hz=hz-10;

if(hz>50000)

hz=50000;

z=0;

}

if(key_5==1&&key_4==1&&key_3==1&&key_2==1&&key_1==0&F_Ph==1&&key_en==0)

{

key_en=1;

hz=hz-1;

if(hz>50000)

hz=50000;

z=0;

}

if(key_5==1&&key_4==1&&key_3==1&&key_2==0&&key_1==1&&F_Ph==0&&key_en==0)

{

key_en=1;

phase=phase+9;

if(phase>=72)

phase=0;

z=0;

}

if(key_5==1&&key_4==1&&key_3==1&&key_2==1&&key_1==0&&F_Ph==0&&key_en==0)

{

key_en=1;

phase=phase+1;

if(phase>=72)

phase=0;

z=0;

}

if(key_5==1&&key_4==1&&key_3==1&&key_2==1&&key_1==1&&key_en==1)

{

key_en=0;

z=1;

}

returnz;

}

voidmain()

{

h=&Hzs[0];pha=&Phs[0];EDA_E=0;

loop:

lcd_init();

wr_com(0x80);

conv_tostring(50000-hz,h);

conv_tostring1(phase*5,pha);

lcd_string(hs);

lcd_string(h);

wr_data('0');

wr_data('H');

wr_data('z');

wr_com(0xc0);

lcd_string(ps);

lcd_string(pha);

send_EDA_data(1,1,phase);

send_EDA_data(0,1,hz/256);

send_EDA_data(1,0,hz%256);

send_EDA_data(0,0,0);

while

(1)

{

if(key_fun())

gotoloop;

}

}

****************液晶显示LCD1602的读写子程序(fun.h)***************

voidrd_b()

{

DATA=0XFF;

RS=0;

RW=1;

while(BUSY==1)

{

En=0;

En=1;

}

En=0;

}

voidwr_com(chara)

{

rd_b();

RS=0;

RW=0;

DATA=a;

En=1;;

En=0;

}

voidwr_data(chara)

{

rd_b();

RS=1;

RW=0;

DATA=a;

En=1;;

En=0;

}

voidlcd_init()

{

wr_com(0x38);

wr_com(0x0f);

wr_com(0x06);

wr_com(0X01);

}

voidlcd_string(char*p)

{

while

(1)

{

if(*p=='\0')

{

break;

}

wr_data(*p);

p++;

}

}

*****************整型转字符串的子程序(stdlib.h)********************

charnumc[]={48,49,50,51,52,53,54,55,56,57};

intnbit[]={1,1,10,100,1000,10000};

voidconv_tostring(unsignedintn,char*p)

{

shortmaxbit=5;

for(;maxbit>0;maxbit--)

*(p+maxbit-1)='0';

if(n>9999)

maxbit=5;

elseif(n>999)

maxbit=4;

elseif(n>99)

maxbit=3;

elseif(n>9)

maxbit=2;

elsemaxbit=1;

for(;maxbit>0;maxbit--)

{

*(p+5-maxbit)=numc[n/nbit[maxbit]];

n=n%nbit[maxbit];

}

}

voidconv_tostring1(unsignedshortintn,char*p)

{

shortmaxbit=3;

for(;maxbit>0;maxbit--)

*(p+maxbit-1)='0';

if(n>99)

maxbit=3;

elseif(n>9)

maxbit=2;

elsemaxbit=1;

for(;maxbit>0;maxbit--)

{

*(p+3-maxbit)=numc[n/nbit[maxbit]];

n=n%nbit[maxbit];

}

}

1EDA程序

--********************地址选择(selec_addr.vhd)**********************

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityselecis

port(e0:

instd_logic;

e1_2:

instd_logic_vector(1downto0);

data:

instd_logic_vector(7downto0);

clk:

instd_logic;

out_addr1,out_addr2:

outintegerrange0to360);

endselec;

architecturebehavofselecis

signaltar:

std_logic_vector(15downto0);

signalph:

integerrange0to255;

begin

process(clk)

variablesum:

integerrange0to100000;

variableaddr1_m,addr2_m:

integerrange0to360;

begin

ifclk='1'then

sum:

=conv_integer(sum+tar);

ifsum<50000then

addr1_m:

=addr1_m+1;

ifaddr1_m=360then

addr1_m:

=0;

endif;

addr2_m:

=addr1_m+5*ph;

elsesum:

=sum-50000;

endif;

endif;

out_addr1<=addr1_m;

out_addr2<=addr2_m;

endprocess;

process(e0,e1_2)

begin

ife0='1'then

casee1_2is

when"01"=>tar(15downto8)<=data;

when"10"=>tar(7downto0)<=data;

when"11"=>ph<=conv_integer(data);

whenothers=>null;

endcase;

endif;

endprocess;

endbehav;

--***********************ROM(rom_data.vhd)********************

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityromis

port(

addr1,addr2:

inintegerrange0to360;

data1,data2:

outstd_logic_vector(7downto0));

endrom;

architecturebehavofromis

typemem_blockisarray(0to360)ofstd_logic_vector(7downto0);

constantrom_data:

mem_block:

=(

x"80",x"82",x"84",x"86",x"88",x"8b",x"8d",x"8f",x"91",x"93",

x"96",x"98",x"9a",x"9c",x"9e",x"a0",x"a3",x"a5",x"a7",x"a9",

x"ab",x"ad",x"af",x"b1",x"b3",x"b5",x"b7",x"b9",x"bb",x"bd",

x"bf",x"c1",x"c3",x"c5",x"c7",x"c9",x"ca",x"cc",x"ce",x"d0",

x"d1",x"d3",x"d5",x"d6",x"d8",x"da",x"db",x"dd",x"de",x"e0",

x"e1",x"e3",x"e4",x"e5",x"e7",x"e8",x"e9",x"ea",x"ec",x"ed",

x"ee",x"ef",x"f0",x"f1",x"f2",x"f3",x"f4",x"f5",x"f6",x"f7",

x"f7",x"f8",x"f9",x"f9",x"fa",x"fb",x"fb",x"fc",x"fc",x"fd",

x"fd",x"fd",x"fe",x"fe",x"fe",x"ff",x"ff",x"ff",x"ff",x"ff",

x"ff",x"ff",x"ff",x"ff",x"ff",x"ff",x"fe",x"fe",x"fe",x"fd",

x"fd",x"fd",x"fc",x"fc",x"fb",x"fb",x"fa",x"f9",x"f9",x"f8",

x"f7",x"f7",x"f6",x"f5",x"f4",x"f3",x"f2",x"f1",x"f0",x"ef",

x"ee",x"ed",x"ec",x"ea",x"e9",x"e8",x"e7",x"e5",x"e4",x"e3",

x"e1",x"e0",x"de",x"dd",x"db",x"da",x"d8",x"d6",x"d5",x"d3",

x"d1",x"d0",x"ce",x"cc",x"ca",x"c9",x"c7",x"c5",x"c3",x"c1",

x"bf",x"bd",x"bb",x"b9",x"b7",x"b5",x"b3",x"b1",x"af",x"ad",

x"ab",x"a9",x"a7",x"a5",x"a3",x"a0",x"9e",x"9c",x"9a",x"98",

x"96",x"93",x"91",x"8f",x"8d",x"8b",x"88",x"86",x"84",x"82",

x"80",x"7d",x"7b",x"79",x"77",x"74",x"72",x"70",x"6e",x"6c",

x"69",x"67",x"65",x"63",x"61",x"5f",x"5c",x"5a",x"58",x"56",

x"54",x"52",x"50",x"4e",x"4c",x"4a",x"48",x"46",x"44",x"42",

x"40",x"3e",x"3c",x"3a",x"38",x"36",x"35",x"33",x"31",x"2f",

x"2e",x"2c",x"2a",x"29",x"27",x"25",x"24",x"22",x"21",x"1f",

x"1e",x"1c",x"1b",x"1a",x"18",x"17",x"16",x"15",x"13",x"12",

x"11",x"10",x"0f",x"0e",x"0d",x"0c",x"0b",x"0a",x"09",x"08",

x"08",x"07",x"06",x"06",x"05",x"04",x"04",x"03",x"03",x"02",

x"02",x"02",x"01",x"01",x"01",x"00",x"00",x"00",x"00",x"00",

x"00",x"00",x"00",x"00",x"00",x"00",x"01",x"01",x"01",x"02",

x"02",x"02",x"03",x"03",x"04",x"04",x"05",x"06",x"06",x"07",

x"08",x"08",x"09",x"0a",x"0b",x"0c",x"0d",x"0e",x"0f",x"10",

x"11",x"12",x"13",x"15",x"16",x"17",x"18",x"1a",x"1b",x"1c",

x"1e",x"1f",x"21",x"22",x"24",x"25",x"27",x"29",x"2a",x"2c",

x"2e",x"2f",x"31",x"33",x"35",x"36",x"38",x"3a",x"3c",x"3e",

x"40",x"42",x"44",x"46",x"48",x"4a",x"4c",x"4e",x"50",x"52",

x"54",x"56",x"58",x"5a",x"5c",x"5f",x"61",x"63",x"65",x"67",

x"69",x"6c",x"6e",x"70",x"72",x"74",x"77",x"79",x"7b",x"7d",x"7f");

begin

data1<=rom_data(addr1);

data2<=rom_data(addr2);

endbehav;

--*********************(altp110.vhd)****************************

LIBRARYieee;

USEieee.std_logic_1164.all;

LIBRARYaltera_mf;

USEaltera_mf.all;

ENTITYaltpll0IS

PORT

(

inclk0:

INSTD_LOGIC:

='0';

c0:

OUTSTD_LOGIC

);

ENDaltpll0;

ARCHITECTURESYNOFaltpll0IS

SIGNALsub_wire0:

STD_LOGIC_VECTOR(5DOWNTO0);

SIGNALsub_wire1:

STD_LOGIC;

SIGNALsub_wire2:

STD_LOGIC;

SIGNALsub_wire3:

STD_LOGIC_VECTOR(1DOWNTO0);

SIGNALsub_wire4_bv:

BIT_VECTOR(0DOWNTO0);

SIGNALsub_wire4:

STD_LOGIC_VECTOR(0DOWNTO0);

COMPONENTaltpll

GENERIC(

clk0_divide_by:

NATURAL;

clk0_duty_cycle:

NATURAL;

clk0_multiply_by:

NATURAL;

clk0_phase_shift:

STRING;

compensate_clock:

STRING;

inclk0_input_frequency:

NATURAL;

intended_device_family:

STRING;

lpm_type:

STRING;

operation_mode:

STRING;

port_activeclock:

STRING;

port_areset:

STRING;

port_clkbad0:

STRING;

port_clkbad1:

STRING;

port_clkloss:

STRING;

port_clkswitch:

STRING;

port_configupdate:

STRING;

port_fbin:

STRING;

port_inclk0:

STRING;

port_inclk1:

STRING;

port_locked:

STRING;

port_pfdena:

STRING;

port_phasecounterselect:

STRING;

port_phasedone:

STRING;

port_phasestep:

STRING;

port_phaseupdown:

STRING;

port_pllena:

STRING;

port_scanaclr:

STRING;

port_scanclk:

STRING;

port_scanclkena:

STRING;

port_scandata:

STRING;

port_scandataout:

STRING;

port_scandone:

STRING;

port_scanread:

STRING;

port_scanwrite:

STRING;

port_clk0:

STRING;

port_clk1:

STRING;

port_clk2:

STRING;

port_clk3:

STRING;

port_clk4:

STRING;

port_clk5:

STRING;

port_clkena0:

STRING;

port_clkena1:

STRING;

port_clkena2:

STRING;

port_clkena3:

STRING;

port_clkena4:

STRING;

port_clkena5:

STRING;

port_extclk0:

STRING;

port_extclk1:

STRING;

port_extclk2:

STRING;

port_extclk3:

STRING

);

PORT(

inclk:

INSTD_LOGIC_VECTOR(1DOWNTO0);

clk:

OUTSTD_LOGIC_VECTOR(5DOWNTO0)

);

ENDCOMPONENT;

BEGIN

sub_wire4_bv(0DOWNTO0)<="0";