基于VHDL语言信号发生器的设计EDA课程设计.docx

《基于VHDL语言信号发生器的设计EDA课程设计.docx》由会员分享,可在线阅读,更多相关《基于VHDL语言信号发生器的设计EDA课程设计.docx(16页珍藏版)》请在冰豆网上搜索。

基于VHDL语言信号发生器的设计EDA课程设计

基于VHDL语言信号发生器的设计

1、设计目的

1)掌握使用EDA工具设计信号发生器系统的设计思路和设计方法,体会使用EDA综合过程中电路设计方法和设计思路的不同,理解层次化设计理念。

2)熟悉在QuartusII环境中,用文本输入方式与原理图输入方式完成电路的设计,同时掌握使用这两种方式相结合的EDA设计思路。

3)通过这一部分的学习,对VHDL语言的设计方法进行进一步的学习,对其相关语言设计规范进行更深层次的掌握,能够更加熟练的做一些编程设计

2、设计的主要内容和要求

通过使用VHDL语言及QuartusII软件,设计多功能信号发生器的每个模块,将正弦波模块,方波模块,三角波模块,阶梯波模块创建相应的元件符号,同时设计好4选1数据选择器模块,再通过原理图输入方式,将各个模块组合起来,设计成一个完整的多种信号发生器电路,同时将各个模块单独进行仿真,设计各个模块的仿真波形,最后进行总原理图电路仿真,设计该信号发生器的总的仿真波形。

信号发生器:

体现在它能自动的实现四种波形的转换。

根据题目的分析与整体构思可知,要完成设计任务必须完成以下要求:

1、设计好用于波形切换的四路数据选择器selector4_1;

2、设计好用于总电路设计的各个信号输出模块;

3、设计好数模(D/A)转换器。

3、整体设计方案

基本设计方案:

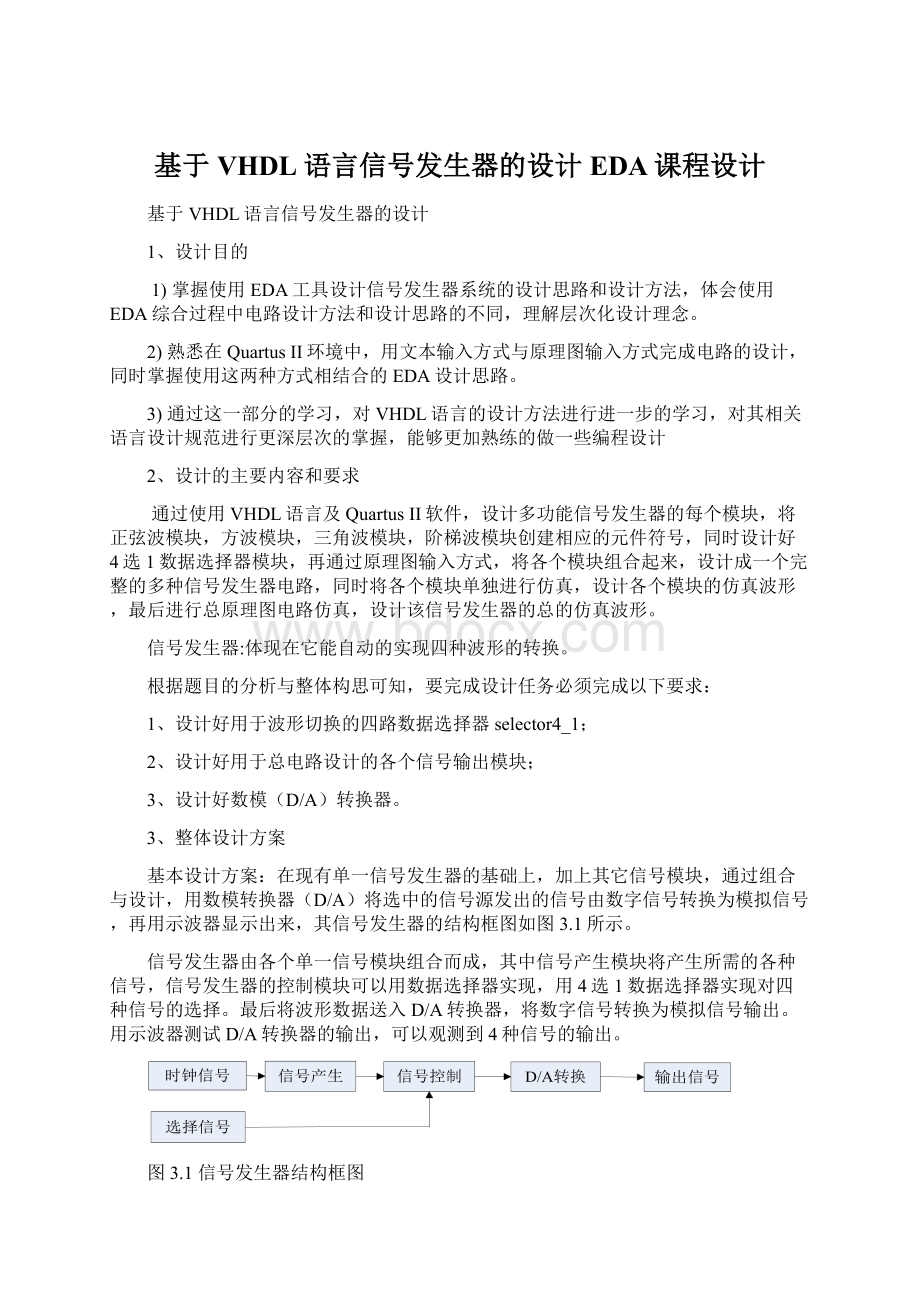

在现有单一信号发生器的基础上,加上其它信号模块,通过组合与设计,用数模转换器(D/A)将选中的信号源发出的信号由数字信号转换为模拟信号,再用示波器显示出来,其信号发生器的结构框图如图3.1所示。

信号发生器由各个单一信号模块组合而成,其中信号产生模块将产生所需的各种信号,信号发生器的控制模块可以用数据选择器实现,用4选1数据选择器实现对四种信号的选择。

最后将波形数据送入D/A转换器,将数字信号转换为模拟信号输出。

用示波器测试D/A转换器的输出,可以观测到4种信号的输出。

图3.1信号发生器结构框图

通过查找资料把各类信号模块的程序输入到QuartusⅡ中进行运行仿真,每一步都要慎重小心,错误难免的,还需要通过课本和资料一一更正。

最后,在前面模块做好的基础上再考虑如何输出波形的问题,通过对四种波形采样就可以得到。

4、硬件电路的设计与软件设计

根据题目分析与整体构思可知,要完成设计任务必须设计出以下模块:

4.1正弦波发生器的实现

该模块产生以64个时钟为一个周期的正弦波。

其VHDL语言源程序代码如下所示:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;--打开库文件

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYsinqiIS

PORT(clk:

INSTD_LOGIC;--声明clk是标准逻辑位类型的输入端口clr:

INSTD_LOGIC;--声明clr是标准逻辑位类型的输入端口

d:

OUTintegerrange0to255);--声明d是标准逻辑向量类型的--输出端口

ENDsinqi;

ARCHITECTUREsinbOFsinqiIS

BEGIN

PROCESS(clr,clk)

variabletemp:

integerrange0to63;

BEGIN

IFclr='0'THENd<=0;--clr为低电平d为0

ELSIFclk'EVENTANDclk='1'THEN--clk为上升沿

IFtemp=63THENtemp:

=0;

ELSE

temp:

=temp+1;

ENDIF;

CASEtempIS

when00=>d<=255;when01=>d<=254;when02=>d<=252;

when03=>d<=249;when04=>d<=245;when05=>d<=239;

when06=>d<=233;when07=>d<=225;when08=>d<=217;

when09=>d<=207;when10=>d<=197;when11=>d<=186;

when12=>d<=174;when13=>d<=162;when14=>d<=150;

when15=>d<=137;when16=>d<=124;when17=>d<=112;

when18=>d<=99;when19=>d<=87;when20=>d<=75;

when21=>d<=64;when22=>d<=53;when23=>d<=43;

when24=>d<=34;when25=>d<=26;when26=>d<=19;

when27=>d<=13;when28=>d<=8;when29=>d<=4;

when30=>d<=1;when31=>d<=0;when32=>d<=0;

when33=>d<=1;when34=>d<=4;when35=>d<=8;

when36=>d<=13;when37=>d<=19;when38=>d<=26;

when39=>d<=34;when40=>d<=43;when41=>d<=53;

when42=>d<=64;when43=>d<=75;when44=>d<=87;

when45=>d<=99;when46=>d<=112;when47=>d<=124;

when48=>d<=137;when49=>d<=150;when50=>d<=162;

when51=>d<=174;when52=>d<=186;when53=>d<=197;

when54=>d<=207;when55=>d<=217;when56=>d<=225;

when57=>d<=233;when58=>d<=239;when59=>d<=245;

when60=>d<=249;when61=>d<=252;when62=>d<=254;

when63=>d<=255;whenothers=>null;--当temp值不是选择值,Q作未知

--处理

ENDCASE;

ENDIF;

ENDPROCESS;

ENDsinb;

4.2方波信号发生器的实现

该模块产生方波,是通过交替送出全0和全1实现,每16个时钟翻转一次。

其VHDL语言源程序代码如下所示:

LIBRARYIEEE;--打开库文件

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYfangboqiIS

PORT(clk:

INSTD_LOGIC;--声明clk是标准逻辑位类型的输入端口

clr:

INSTD_LOGIC;--声明clr是标准逻辑位类型的输入端口

q:

OUTSTD_LOGIC_VECTOR(7DOWNTO0));--声明q是标准逻辑--向量类型的输出端口

ENDfangboqi;

ARCHITECTUREfangbo1OFfangboqiIS--结构体说明

SIGNALa:

STD_LOGIC;

BEGIN

PROCESS(clk,clr)

VARIABLEtmp:

std_logic_vector(3downto0);--变量定义

BEGIN

IFclr='0'THENa<='0';

ELSIFclk'eventANDclk='1'THEN--clk为上升沿

IFtmp="1111"THENtmp:

="0000";

ELSE

tmp:

=tmp+1;

ENDIF;

IFtmp<"1000"THEN

a<='1';

ELSE

a<='0';

ENDIF;

ENDIF;

ENDPROCESS;

PROCESS(clk,a)

BEGIN

IFclk'eventANDclk='1'THEN--clk为上升沿

IFa='1'THEN

q<="11111111";--q赋值

ELSE

q<="00000000";--q赋值

ENDIF;

ENDIF;

ENDPROCESS;--结束进程

ENDfangbo1;--结束结构体

4.3三角波信号发生器的实现

该模块产生的三角波形以64个时钟为一个周期,输出q每次加减8

其VHDL语言源程序代码如下所示:

LIBRARYIEEE;--打开库文件

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYsjboIS

PORT(clk:

INSTD_LOGIC;--声明clk是标准逻辑位类型的输入端口

clr:

INSTD_LOGIC;--声明clr是标准逻辑位类型的输入端口

q:

OUTSTD_LOGIC_VECTOR(7DOWNTO0));--声明q是标准逻辑--向量类型的输出端口

ENDsjbo;

ARCHITECTUREsjqiOFsjboIS--结构体说明

BEGIN

PROCESS(clk,clr)

VARIABLEtmp:

STD_LOGIC_VECTOR(7DOWNTO0);--变量说明

VARIABLEa:

STD_LOGIC;

BEGIN

IFclr='0'THENtmp:

="00000000";

ELSIFclk'eventANDclk='1'THEN--clk为上升沿

IFa='0'THEN

IFtmp="11111000"THEN

tmp:

="11111111";

a:

='1';

ELSE

tmp:

=tmp+8;

ENDIF;

ELSE

IFtmp="00000111"THEN

tmp:

="00000000";

a:

='0';

ELSE

tmp:

=tmp-8;

ENDIF;

ENDIF;

ENDIF;

q<=tmp;--q赋值

ENDPROCESS;

ENDsjqi;

4.4阶梯波信号发生器的实现

该模块产生的是阶梯波形。

其VHDL语言源程序代码如下所示:

LIBRARYIEEE;--打开库文件

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYjietiboqiIS

PORT(clk:

INSTD_LOGIC;--声明clk是标准逻辑位类型的输入端口

clr:

INSTD_LOGIC;--声明clr是标准逻辑位类型的输入端口

Q:

BUFFERSTD_LOGIC_VECTOR(7DOWNTO0));

ENDjietiboqi;

ARCHITECTUREjietiboOFjietiboqiIS--结构体说明

BEGIN

PROCESS(clk,clr)

VARIABLEtmp:

STD_LOGIC_VECTOR(7DOWNTO0);--变量定义

BEGIN

IFclr='0'THENtmp:

="00000000";--变量赋值

ELSEIFclk'eventANDclk='1'THEN--clk为上升沿

IFtmp="11111111"THEN

tmp:

="00000000";

ELSE

tmp:

=tmp+30;

ENDIF;

ENDIF;

ENDIF;

Q<=tmp;

ENDPROCESS;--结束进程

ENDjietibo;

4.5四选一数据选择器的实现

该模块的VHDL语言源程序代码如下所示:

LIBRARYIEEE;--打开库文件

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYselector4_1IS--实体说明

PORT(--端口说明

sel:

INSTD_LOGIC_VECTOR(1DOWNTO0);

D0,D1,D2,D3:

INSTD_LOGIC_VECTOR(7DOWNTO0);

Q:

OUTSTD_LOGIC_VECTOR(7DOWNTO0));

ENDselector4_1;

ARCHITECTUREoneOFselector4_1IS--结构体说明

BEGIN

PROCESS(sel,D0,D1,D2,D3)

BEGIN

CASEselIS

WHEN"00"=>Q<=D0;

WHEN"01"=>Q<=D1;

WHEN"10"=>Q<=D2;

WHEN"11"=>Q<=D3;

WHENothers=>Q<=null;--当sel的值不是选择值时,Q作未知处理

ENDCASE;

ENDPROCESS;

ENDone;

4.6数模转换器(D/A)

图4.6数模转换器DAC0832的连接电路图

选择一个D/A转换器,将数据选择器的输出信号与D/A转换器的输入端相连接,D/A转换器的可选择范围很宽,这里选择常用的DAC0832,其DAC0832的连接电路如上图4.6所示。

4.7信号发生器程序流程框图

当输入端有时钟信号输入时,各个信号发生器模块独立运行,独立存在,发出各种信号,这些信号作为数据选择器的输入信号,在数据选择器的作用下,波形切换到相应的模块输出,再通过数模转换器(D/A),将通过示波器显示出相应的波形图,其程序流程图如下图4.7所示:

图4.7信号

发生器程序流程框图

5、系统仿真

通过QuartusⅡ软件设计出各个模块的原理图及其相关仿真波形示意图如下:

在QuartusII的软件环境下,通过文本方式编写各个信号波形模块的VHDL

语言源程序,且进行仿真。

接下来将各个信号波形模块产生相应的元件符号,新建一个工程,加载上述模块,利用原理图输入法生成整体多波形信号发生器。

5.1正弦波发生器的原理图及其仿真波形图:

正弦波信号发生器的原理图如下图所示:

图5.1.1正弦波信号发生器原理图

正弦波信号发生器的仿真波形图如下图所示:

图5.1.2正弦波信号发生器仿真波形图

Clk由0到1交替变更,clr一直处于高电平状态,Q端则由00001000到00010000并依次加00001000

5.2方波发生器的原理图及其仿真波形图:

方波信号发生器的原理图如下图所示:

图5.2.1方波信号发生器的原理图

方波信号发生器的仿真波形图如下图所示:

图5.2.2方波信号发生器的仿真波形图

Clk由0到1交替变更,clr一直处于高电平状态,q端则由00000000到11111111并依次交替下去

5.3三角波发生器的原理图及其仿真波形图:

三角波信号发生器的原理图如下图所示:

图5.3.1三角波信号发生器的原理图

三角波信号发生器的仿真波形图如下图所示:

图5.3.2三角波信号发生器的仿真波形图

Clk、clr均同时由0到1交替变更Q端则由00000000到00000001并依次加00000001进行下去

5.4阶梯波发生器的原理图及其仿真波形图

阶梯波信号发生器的原理图如下图所示:

图5.4.1阶梯波信号发生器的原理图

阶梯波信号发生器的仿真波形图如下图5.8所示:

图5.4.2阶梯波信号发生器的仿真波形图

Clk由0到1交替变更,clr一直处于高电平状态,Q端从00000000开始则高四位依次由0001每次加0010进行下去,第四位依次由1110每次减0010进行下去。

5.54选1数据选择器的原理图及其仿真波形图

4选1数据选择器的原理图如下图所示:

图5.5.14选1数据选择器的原理图

4选1数据选择器的仿真波形图如下图所示:

图5.5.24选1数据选择器的仿真图

sel由00每次加01交替变更,依次选择Q的输出值。

5.6信号发生器的原理图及其仿真波形图

整体信号发生器的原理图如下图所示:

图5.6.1信号发生器原理图

整体信号发生器的仿真波形图如下图所示:

图5.6.2多功能信号发生器的仿真图

clk由0到1交替变更,clr一直处于高电平状态,Q端则由56每次加8依次进行下去。

6、使用说明

6.1从QuartusII软件环境中编写各个相关信号模块的VHDL语言源程序及生成相关模块的元件符号名称:

sinqi:

正弦波信号发生器模块;

fangboqi:

方波信号发生器模块;

sjqi1:

三角波信号发生器模块;

jietiboqi:

阶梯波信号发生器模块;

selector4_1:

四选一数据选择器输出模块;

多功能信号发生器输出波形可以由sel中位的组合形式选择,从而控制信号发生器波形的输出,通过sel的不同值可以选取正弦波信号发生器模块、方波信号发生器模块、正弦波信号发生器模块及三角波信号发生器模块、

6.2整体电路的综合分析

在QuartusII软件环境原理图输入方式中放置各个元件符号,放置输入和输出接口、组合各个信号模块、连线、编译、建立波形仿真图、仿真。

所有的操作都是在QuartusII软件环境中进行,输入信号从各个信号发生器模块输入端输入,通过数据选择器输出所选择的的信号来切换输出相应波形的输出,在通过数模转换器(D/A)将数字信号转换为模拟信号,最后由示波器显示相应的波形。

7、总结

在本次课程设计中,我的设计较好地完成了既定目标,能够产生正弦波、方波、三角波和阶梯波波形,很成功的完成系统的功能实现。

通过该课程设计使我全面熟悉、掌握了VHDL语言基本知识,掌握利用VHDL语言对信号发生器的编程和时序逻辑电路的编程,把编程和实际结合起来,熟悉编制和调试程序的技巧,掌握分析结果的若干有效办法,进一步提高动手能力,培养使用设计综合电路的能力,养成提供文档资料的习惯和规范编程的思想。

在设计的过程中,也遇到了很多问题,在同学和指导老师的帮助下,都一一得到了解决。

从选题到定稿,从了解到熟悉,用了大概一个星期的时间,在这段时间内,苦恼、思考、喜悦、收获,感受颇多。

当然此次设计也体现出我平时学习中有许多不足和欠缺之处,此后需通过学习来查漏补缺。

参考文献

[1]江国强.EDA技术与应用(M).电子工业出版社,2010.20(3):

36-39

[2]赵建东,陈小乐.基于Internet的智能家庭网络控制器的实现[J].电子技术应用,2002,34(12):

23-25.

[3]李永东,岳继光,李炳宇.PIC单片机在楼宇对讲系统中的应用[J].电

[4]李强华,张根宝,段力.基于单片机控制的楼宇对讲系统的设计[J].电气应用,2007,12(01):

04-06.

[5]江国强.EDA技术与应用(第3版)2010,4(11):

10-22

[6]吴庆元,卢益民.智能小区系统通信协议的设计[J].通信技术,2003,19(7):

98-99.