SignalTap自己总结使用精华.docx

《SignalTap自己总结使用精华.docx》由会员分享,可在线阅读,更多相关《SignalTap自己总结使用精华.docx(27页珍藏版)》请在冰豆网上搜索。

SignalTap自己总结使用精华

SignalTapⅡ嵌入式逻辑分析仪的使用

随着FPGA设计任务复杂性的不断提高,FPGA设计调试工作的难度也越来越大,在设计验证中投入的时间和花费也会不断增加。

为了让产品更快投入市场,设计者必须尽可能减少设计验证时间,这就需要一套功能强大且容易使用的验证工具。

AlteraSignalTapⅡ逻辑分析仪可以用来对AlteraFPGA内部信号状态进行评估,帮助设计者很快发现设计中存在问题的原因。

QuartusⅡ软件中的SignalTapⅡ逻辑分析仪是非插入式的,可升级,易于操作且对QuartusⅡ用户**。

SignalTapⅡ逻辑分析仪允许设计者在设计中用探针的方式探查内部信号状态,帮助设计者调试FPGA设计。

SignalTapⅡ逻辑分析仪支持下面的器件系列:

StratixⅡ、Stratix、StratixGX、CycloneⅡ、Cyclone、APEXⅡ、APEX20KE、APEX20KC、APEX20K、Excalibur和Mercury。

10.1在设计中嵌入SignalTapⅡ逻辑分析仪

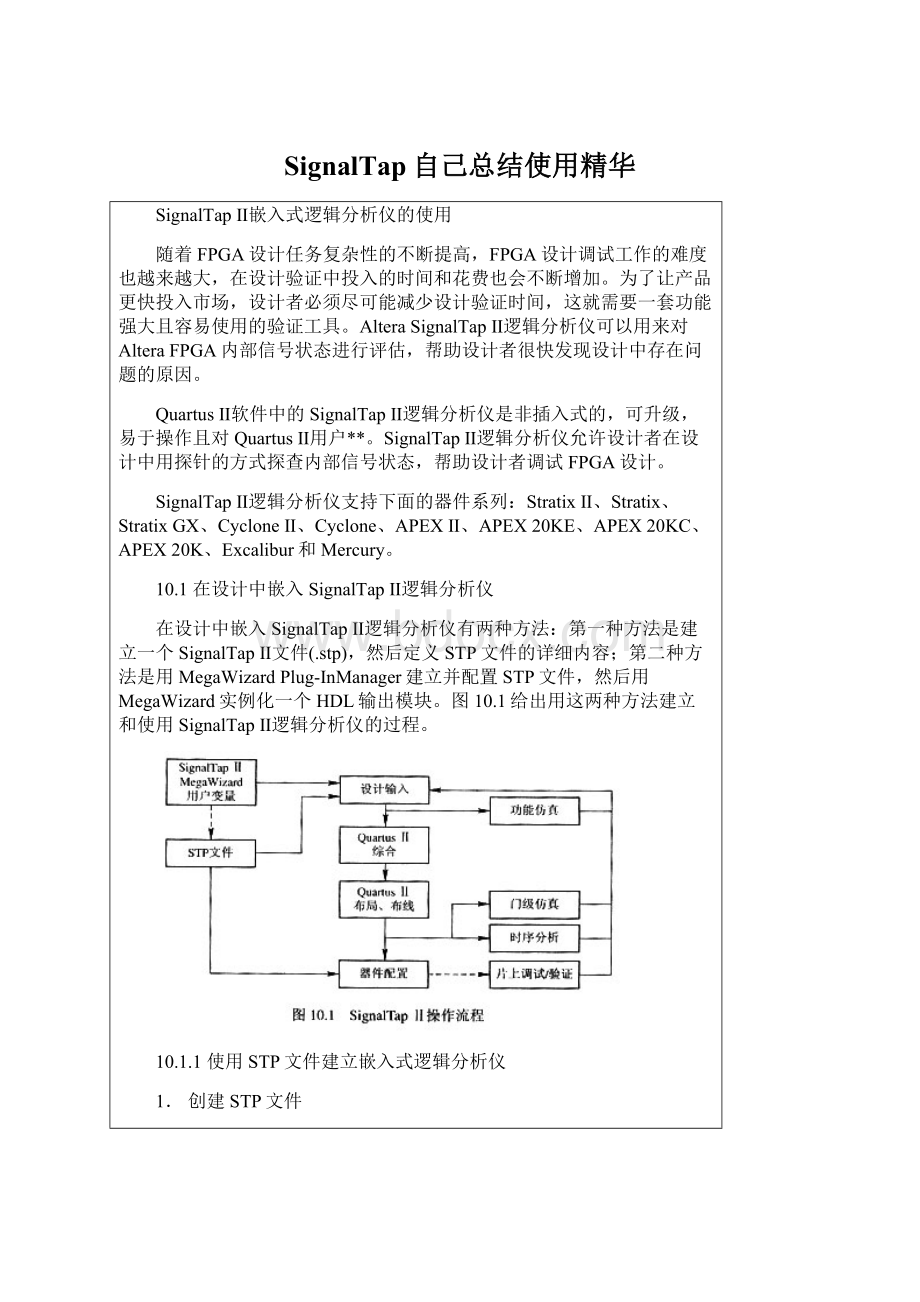

在设计中嵌入SignalTapⅡ逻辑分析仪有两种方法:

第一种方法是建立一个SignalTapⅡ文件(.stp),然后定义STP文件的详细内容;第二种方法是用MegaWizardPlug-InManager建立并配置STP文件,然后用MegaWizard实例化一个HDL输出模块。

图10.1给出用这两种方法建立和使用SignalTapⅡ逻辑分析仪的过程。

10.1.1使用STP文件建立嵌入式逻辑分析仪

1.创建STP文件

STP文件包括SignalTapⅡ逻辑分析仪设置部分和捕获数据的查看、分析部分。

创建一个STP文件的步骤如下:

(1)在QuartusⅡ软件中,选择File→New命令。

(2)在弹出的New对话框中,选择OtherFiles标签页,从中选择SignalTapⅡ File

如图10.2所示。

(3)点击OK按钮确定,一个新的SignalTapⅡ窗口如图10.3所示。

上面的操作也可以通过Tools→SignalTap ⅡLogicAnalyzer命令完成,这种方法也可以用来打开一个已经存在的STP文件。

2.设置采集时钟

在使用SignalTapⅡ逻辑分析仪进行数据采集之前,首先应该设置采集时钟。

采集时钟在上升沿处采集数据。

设计者可以使用设计中的任意信号作为采集时钟,但Altera建议最好使用全局时钟,而不要使用门控时钟。

使用门控时钟作为采集时钟,有时会得到不能准确反映设计的不期望数据状态。

QuartusⅡ时序分析结果给出设计的最大采集时钟频率。

设置SignalTapⅡ采集时钟的步骤如下:

(1)在SignalTapⅡ逻辑分析仪窗口选择Setup标签页。

(2)点击Clock栏后面的BrowseNodeFinder按钮,打开NodeFinder对话框。

(3)在NodeFinder对话框中,在Filter列表中选择SignalTapⅡ:

pre-synthesis。

(4)在Named框中,输入作为采样时钟的信号名称;或点击List按钮,在NodesFound列表中选择作为采集时钟的信号。

(5)点击OK确定。

(6)在SignalTapⅡ窗口中,设置作为采样时钟的信号显示在Clock栏中。

用户如果在SignalTapⅡ窗口中没有分配采集时钟,QuartusⅡ软件会自动建立一个名为auto_stp_external_clk的时钟引脚。

在设计中用户必须为这个引脚单独分配一个器件引脚,在用户的印刷电路板(PCB)上必须有一个外部时钟信号驱动该引脚。

3.在STP文件中分配信号

在STP文件中,可以分配下面两种类型的信号:

(1)Pre—synthesis:

该信号在对设计进行Analysis&Elaboration操作以后存在,这些信号表示寄存器传输级(RTL)信号。

在SignalTapⅡ中要分配Pre-synthesis信号,应选择Processing→StartAnalysis&Elaboration命令。

对设计进行修改以后,如果要在物理综合之前快速加入一个新的节点名,使用这项操作特别有用。

(2)Post-fitting:

该信号在对设计进行物理综合优化以及布局、布线操作后存在。

4.分配数据信号

(1)首先完成设计的Analysis&Elaboration或Analysis&Synthesis,或全编译过程。

(2)在SignalTapⅡ逻辑分析仪窗口,点击Setup标签页。

(3)在STP窗口的Setup标签页中双击鼠标左键,弹出NodeFinder对话框。

(4)在NodeFinder对话框的Filter列表中选择SignalTapⅡ:

pre-synthesis或SignalTap

Ⅱ:

post-fitting。

(5)在Named框中输入节点名、部分节点名或通配符,点击List按钮查找节点。

(6)在NodesFound列表中选择要加入STP文件中的节点或总线。

(7)点击“>”按钮将选择的节点或总线拷贝到SelectedNodes列表中。

(8)点击OK按钮,将选择的节点或总线插入STP文件,如图10.4所示。

5.逻辑分析仪触发控制

逻辑分析仪触发控制包括设置触发类型和触发级数。

1)触发类型选择Basic

如果触发类型选择Basic,在STP文件中必须为每个信号设置触发模式(TriggerPattern)。

SignalTapⅡ逻辑分析仪中的触发模式包括:

Don’tCare(无关项触发),Low(低电平触发),High(高电平触发),FallingEdge(下降沿触发),RisingEdge(上升沿触发)以及EitherEdge(双沿触发)。

当选定触发级数的所有信号的“逻辑与”结果为TRUE时,SignalTapⅡ逻辑分析仪开始捕捉数据,如图10.5所示。

2)触发类型选择Advanced

如果触发类型选择Advanced,则设计者必须为逻辑分析仪建立触发条件表达式。

一个逻辑分析仪最关键的特点就是它的触发能力。

如果不能很好地为数据捕获建立相应的触发条件,逻辑分析仪就可能无法帮助设计者调试设计。

在SignalTapⅡ逻辑分析仪中,使用如图10.6所示的高级触发条件编辑器(AdvancedTriggerConditionEditor),用户可以在简单的图形界面中建立非常复杂的触发条件。

设计者只需要将运算符拖动到触发条件编辑器窗口中,即可建立复杂的触发条件。

3)触发级数选择

SignalTapⅡ逻辑分析仪的多级触发特性为设计者提供了更精确的触发条件设置功能。

在多级触发中,Signal]1apII逻辑分析仪首先对第一级触发模式进行触发;当第一级触发表达式满足条件,测试结果为TRUE时,SignalTapⅡ逻辑分析仪对第二级触发表达式进行测试;依次类推,直到所有触发级完成测试,并且最后一级触发条件测试结果为TRUE时,SignalTapⅡ逻辑分析仪开始捕获信号状态。

在图10.3的触发级数选择列表中选择触发级数,SignalTapⅡ逻辑分析仪最大可以选择触发级数为10级。

6.指定采样点数及触发位置

在触发事件开始之前,用户可以指定要观测数据的采样点数,即数据存储深度,以及触发事件发生前后的采样点数。

在sTP文件窗口的Data栏中,在Sampledepth列表中可以选择逻辑分析仪的采样点数;在Bufferacquisitionmode栏中,在circular列表中可以选择超前触发数据和延时触发数据之间的比例,其中:

?

Pretriggerposition:

保存触发信号发生之前的信号状态信息(88%触发前数据,12%触发后数据);

?

Centertriggerposition:

保存触发信号发生前后的数据信息,各占50%;

?

Posttriggerposition:

保存触发信号发生之后的信号状态信息(12%触发前数据,88%触发后数据);

?

Continuoustriggerposition:

连续保存触发采样数据,直到设计者停止采集数据为止。

触发位置设置允许用户指定SignalTapⅡ逻辑分析仪在触发信号发生前后需要捕获的采样点数。

采集数据被放置在一个环形数据缓冲区中。

在数据采集过程中,新的数据可以替代旧的数据,如图10.7所示。

这个环形数据缓冲区的大小等于用户设置的数据存储深度。

7.编译嵌入SignalTapⅡ逻辑分析仪的设计

配置好STP文件以后,在使用SignalTapⅡ逻辑分析仪之前必须编译QuartusⅡ设计工程。

首次建立并保存STP文件时,QuartusⅡ软件自动将STP文件加入工程中。

也可以采用下面的步骤手动添加STP文件:

(1)选择Assignments→Settings命令,弹出Settings对话框。

(2)在Category列表中选择SignalTapⅡLogicAnalyzer。

(3)在SignalTapⅡLogicAnalyzer页中,使能EnableSignalTapⅡLogicAnalyzer选项。

(4)在SignalTapⅡFileName栏中输入STP文件名。

(5)点击OK按钮确认。

(6)选择Processing→StartCompilation命令开始编译。

10.1.2使用MegaWizardPlug-InManager建立嵌入式逻辑分析仪

使用MegaWizardPlug-InManager建立SignalTapⅡ逻辑分析仪不需要建立STP文件。

MegaWizardPlug-InManager生成一个可以在设计中实例化的HDL文件。

1.建立SignalTapⅡ逻辑分析仪的HDL描述

在QuartusⅡ软件中,执行SignalTapⅡ兆函数(Mega)可以很容易地使用MegaWizardPlug-InManager建立SignalTapⅡ逻辑分析仪。

步骤如下:

(1)在QuartusⅡ软件中选择Tools→MegaWizardPlug-InManager命令。

(2)在弹出的MegaWizardPlug-InManager对话框中选择Createanewcustommegavariation项。

(3)点击Next按钮。

(4)在弹出的对话框中选择SignalTapⅡLogicAnalyzer,并选择输出文件类型,输入SignalTapⅡ兆函数名,如图10.8所示。

(5)点击Next按钮。

(6)在弹出的下一个对话框中,指定逻辑分析仪的采样深度(Sampledepth)、存储器类型(RAMtype)、数据输入端口宽度(Datainputportwidth)、触发输入端口宽度(Triggerinputportwidth)以及触发级数(Triggerlevels),如图10.9所示。

(7)点击Next按钮。

(8)通过选择Basic或Advanced设置每一级触发选项,如图10.10所示。

(9)点击Finish按钮,完成建立SignalTapⅡ逻辑分析仪HDL描述的过程。

如果在第(8)步中选择了Advanced,将弹出如图10.6所示的高级触发条件编辑器界面。

2.SignalTapⅡ兆函数端口

表10.1给出了SignalTap口兆函数端口的描述。

3.在设计文件中实例化SignalTapⅡ逻辑分析仪

在设计中实例化SignalTapⅡ逻辑分析仪的过程与实例化其他VHDL或VerilogHDL兆函数相同。

在设计中实例化SignalTapⅡ文件以后,为了在目标FPGA器件中适配逻辑分析仪,必须编译QuartusⅡ工程文件。

图10.11所示为SignalTap口逻辑分析仪的实例化结果。

编译完加入了SignalTapⅡ逻辑分析仪实例化模块的设计工程以后,要捕获并观测数据,必须从SignalTapⅡMegaWizard的输出文件建立STP文件。

选择File→Create/UpdateMenu→CreateSignalTapⅡFilefromDesignInstance(s)命令,输入STP文件名,则根据SignalTapⅡMegaWizard中的设置自动建立并打开STP文件。

SignalTapⅡ嵌入式逻辑分析仪的使用

(2)

2008-05-3120:

58

10.1.3SignalTapⅡ分析器件编程

在设计中嵌入SignalTalⅡ逻辑分析仪并编译完成以后,打开STP文件,完成嵌入SignalTapⅡ逻辑分析仪器件编程的步骤如下:

(1)在STP文件中,在JTAGChain设置部分选择嵌入SignalTapⅡ逻辑分析仪的SRAM对象文件(.sot)。

(2)点击ScanChain按钮。

(3)在Device列表中选择目标器件。

(4)点击ProgramDevice图标进行器件编程,如图10.12所示。

10.1.4查看SignalTapⅡ采样数据

在SiganlTapⅡ窗口中,选择RunAnalysis或AutoRunAnalysis按钮启动SignalTapⅡ逻辑分析仪。

当触发条件满足时,SignalTapⅡ逻辑分析仪开始捕获数据。

SignalTapⅡ工具条上有四个执行逻辑分析仪选项,如图10.13左上角所示,其中:

?

RunAnalysis:

单步执行SignalTapⅡ逻辑分析仪。

即执行该命令后,SignalTapⅡ逻辑分析仪等待触发事件,当触发事件发生时开始采集数据,然后停止。

?

AutoRunAnalysis:

执行该命令后,SignalTapⅡ逻辑分析仪连续捕获数据,直到用户按下StopAnalysis为止。

?

StopAnalysis:

停止SignalTapⅡ分析。

如果触发事件还没有发生,则没有接收数据显示出来。

?

ReadData:

显示捕获的数据。

如果触发事件还没有发生,用户可以点击该按钮查看当前捕获的数据。

SignalTap Ⅱ逻辑分析仪自动将采集数据显示在SignalTapⅡ界面的Data标签页中,如图10.13所示。

10.2在SOPCBuilder中使用SignalTapⅡ逻辑分析仪

SignalTapⅡ是在片上系统设计(SOPC)中捕捉和显示实时信号的系统级调试工具。

在SOPCBuilder生成的系统中使用SignalTapⅡ嵌入式逻辑分析仪(ElA),设计者可以观测在软件执行过程中硬件(如外设寄存器、存储器总线以及其他片上组件)响应的状态。

本节主要介绍使用SignalTapⅡ嵌入式逻辑分析仪检测由SOPCBuilder生成的系统模块内部信号。

图10.14给出了一个SOPCBuilder系统模块的例子,这个系统包含了一个Nios处理器、一个DMA控制器、一个片上存储器和一个外部SDRAM存储器接口等。

在该例中,Nios处理器执行一个简单的C程序等待一个按键动作的发生。

一个按键被按下后,处理器初始化一个DMA传输,这时我们可以使用SignalTapⅡ逻辑分析仪进行分析。

本节将演示用SignalTapⅡ嵌入式逻辑分析仪测试图10.14中所标识的三种不同类型信号的方法,这三种信号分别是:

(1)连接外部SDRAM存储器的外部I/O接口信号。

(2)系统模块内部的外设控制寄存器信号,如本例中的DMA外设。

(3)Avalon开关结构逻辑(AvalonSwitchFabricLogic)与系统模块内部设备(如本例的片上存储器)之间的Avalon接口信号。

通过观察这些信号,可以检查DMA外部设备从外部SDRAM到片上存储器传输数据的情况。

将软件使能DMA传输信号作为触发条件,即DMA外设控制寄存器的第三位为高电平(逻辑1)时。

为了更好地完成本节的学习,需要以下的系统配置:

?

QuartusⅡ软件3.0以上版本;

?

Nios开发工具3.1以上版本或NiosⅡIDE开发工具,或Nios处理器的一个OpenCorePlus评估版授权;

?

Nios开发板,Cyclone或Stratix;

?

ByteBlasterⅡ或ByteBlasterMV下载电缆。

本节的设计实例在安装Nios开发工具时会自动安装在tutorials目录中,也可直接从网站http:

//www.altera.com/literature/lit-nio.html下载UsingSignalTapⅡEmbeddedLogicAnalyzersinSOPCBuilderSystems设计文件。

该例中包含一个锁相环(PLL)模块、一个级数延时模块和一个SOPC系统设计模块,如图10.15所示,其中SOPC系统设计模块包含图10.14中的各个功能模块。

下面的步骤将在QuartusⅡ软件中打开设计实例或新建一个QuartusⅡ工程,产生SOPCBuilder系统模块,并在系统中创建一个分析信号的SignalTapⅡ嵌入式逻辑分析仪。

1.打开并产生SOPCBuilder系统

(1)在QuartusⅡ软件中打开设计实例工程文件SignalTap.bdf。

(2)在工程导航栏中双击顶层文件名,打开顶层设计文件,如图10.15所示。

(3)选择Tools→SOPCBuilder命令,QuartusⅡ自动在SOPCBuilder中打开系统模型,其中包括用户接口,如图10.16所示

(4)在SOPCBuilder界面的SystemContents页面中,从TargetDeviceFamily列表中选择与Nios开发板匹配的目标器件系列。

(5)在SystemGeneration标签页中,点击Generate按钮产生系统逻辑。

(6)SOPC系统模块产生完成以后,点击Exit退出SOPCBuilder界面,返回QuartusⅡ软件界面。

(7)如果QuartusⅡ弹出对话框,问是否要更新SOPC系统符号,选择Yes。

(8)完成下面的步骤,执行Tcl脚本文件,完成Nios开发板上目标器件的引脚分配:

?

选择View→UtilityWindows→TclConsole命令,打开Tcl控制台窗门。

?

根据Nios开发板上的器件类型,在Tcl控制台输入并执行下面的Tcl脚本:

sourcedevice_assignments_lslO.tcl(回车)

或 sourcedevice_assignments_lc20.tcl(回车)

(9)选择Processing→Start→StartAnalysis&Synthesis编译设计。

2.创建一个新的SignalTapⅡ文件并加入监测信号

(1)选择File→New…命令。

(2)在弹出的New对话框中,选择OtherFiles标签页,从中选择SignalTapⅡFile,如图10.2所示。

(3)点击OK按钮,建立一个新的SignalTapⅡ界面。

(4)在界面的Signal设置中为嵌入式逻辑分析仪选择PLD_CLOCKINPUT输入信号作为同步时钟,如图10.17所示。

(5)在Data栏中,从Sample深度列表中选择采样点数为256,如图l0.17所示。

(6)在SignalTapⅡ界面下,用鼠标左键在Setup空白区内双击,打开NodeFinder对话框。

在NodeFinder对话框内,Filter栏中将显示SignalTapⅡ:

pre-synthesis,如图10.18所示。

下面的步骤主要介绍如何在NodeFinder对话框中查找要监测的信号,并将它们加入到SignalTapⅡ逻辑分析仪中。

(7)在图10.18所示的NodeFinder对话框中,在Named栏内输入“SDRAM*”。

(8)点击右边的List按钮开始查找SDRAM节点,在NodesFound中将列出所有找到的SDRAM节点名。

(9)在NodesFound列表中,选择下面的SDRAMI/O引脚并拷贝到右边的SelectedNodes栏中,其结果如图10.19所示:

SDRAM_A总线、SDRAM_BA总线、SDRAM_CAS_N信号、SDRAM_CKE信号、SDRAM_CS_N信号、SDRAM_DQ总线、SDRAM_DQM总线、SDRAM_RAS_N信号和SDRAM_WE_N信号。

(10)在图10.18所示的NodeFinder对话框中,点击Look栏后面的浏览按钮,弹出SelectHierarchyLevel对话框,如图10.20所示,从中选择SOPC_system:

inst层下面的DMA:

the_DMA单元,点击OK按钮确定,返回NodeFinder对话框。

在NodeFinder对话框中的Look栏中显示出所选的查找范围,点击List按钮,选择下面列出的DMA外设内部寄存器并拷贝到SelectedNodes栏中,其结果如图10.2l所示:

控制寄存器(*DMAIcontr01)、完成位(*DMAIdone)、读地址总线(*DMAIread_address)和写地址总线(*DMAlwrite_address)。

(11)在SelectHierarchyLevel对话框(如图10.20所示)中选择SOPC_system:

inst层下面的onchip_memory:

the_onchip_memory单元,点击OK按钮确定,返回NodeFinder对话框。

点击NodeFinder对话框中的List按钮,选择下面列出的片上存储器信号,其结果如图lO.22所示:

片上存储器写数据总线(*onchip_memorylwritedata)、片上存储器地址总线、(*onchip_memoryladdress)和写信号(*onchip_memorylwrite)。

(12)指明了上面所有要监测的节点以后,点击NodeFinder对话框上的OK按钮确定,返回到SignalTapⅡ窗口,所有选择的信号都在Setup区域中列出,如图10.23所示。

(13)设置SignalTapⅡ嵌入式逻辑分析仪的触发条件。

?

在Setup区域中,点击SOPC_system:

instlDMA:

the_DMAIcontrol寄存器总线前面的加号“+”号将其展开。

?

在*DMA:

the_DMAIcontrol[3]行的TriggerLevels列点击鼠标右键,从弹出的右键菜单中选择High,如图10.23所示。

(14)保