信号发生器实验报告.docx

《信号发生器实验报告.docx》由会员分享,可在线阅读,更多相关《信号发生器实验报告.docx(17页珍藏版)》请在冰豆网上搜索。

信号发生器实验报告

信号发生器设计

1.设计任务

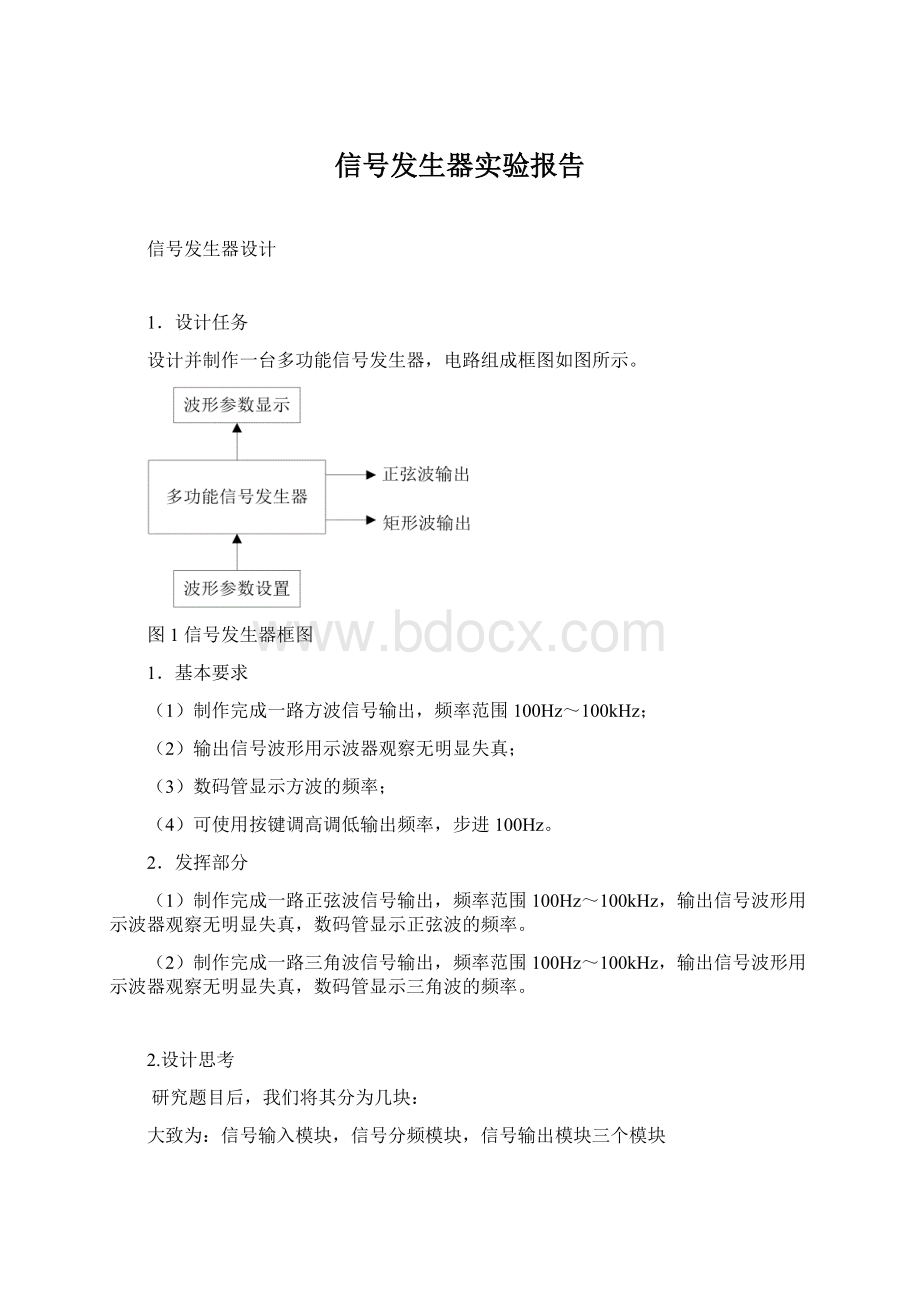

设计并制作一台多功能信号发生器,电路组成框图如图所示。

图1信号发生器框图

1.基本要求

(1)制作完成一路方波信号输出,频率范围100Hz~100kHz;

(2)输出信号波形用示波器观察无明显失真;

(3)数码管显示方波的频率;

(4)可使用按键调高调低输出频率,步进100Hz。

2.发挥部分

(1)制作完成一路正弦波信号输出,频率范围100Hz~100kHz,输出信号波形用示波器观察无明显失真,数码管显示正弦波的频率。

(2)制作完成一路三角波信号输出,频率范围100Hz~100kHz,输出信号波形用示波器观察无明显失真,数码管显示三角波的频率。

2.设计思考

研究题目后,我们将其分为几块:

大致为:

信号输入模块,信号分频模块,信号输出模块三个模块

我们使用VHDL语言,利用QuartusII中由程序建模块的功能,FPGA及SmartSOPC实验箱来完成此次设计。

设计的流程图如下所示:

图一.设计流程图

FPGA中的波形发生器控制电路,它通过外来控制信号和高速时钟信号,向波形数据ROM发出地址信号,输出波形的频率由发出的地址信号的速度决定;当以固定频率扫描输出地址时,模拟输出波形是固定频率,而当以周期性时变方式扫描输出地址时,则模拟输出波形为扫频信号。

波形数据ROM中存有发生器的波形数据,如正弦波或三角波数据。

当接受来自FPGA的地址信号后,将从数据线输出相应的波形数据,地址变化得越快,则输出数据的速度越快,从而使D/A输出的模拟信号的变化速度越快。

波形数据ROM可以由多种方式实现,如在FPGA外面外接普通ROM;由逻辑方式在FPGA中实现(如例11-1);或由FPGA中的EAB模块担当,如利用LPM_ROM实现。

相比之下,第1种方式的容量最大,但速度最慢;,第2种方式容量最小,但速度最最快;第3种方式则兼顾了两方面的因素;

D/A转换器负责将ROM输出的数据转换成模拟信号,经滤波电路后输出。

输出波形的频率上限与D/A器件的转换速度有重要关系,本例采用DAC0832器件。

DAC0832是8位D/A转换器,转换周期为1µs,其引脚信号以及与FPGA目标器件典型的接口方式如附图2-15所示。

其参考电压与+5V工作电压相接(实用电路应接精密基准电压)。

DAC0832的引脚功能简述如下:

ILE(PIN19):

数据锁存允许信号,高电平有效,系统板上已直接连在+5V上。

WR1、WR2(PIN2、18):

写信号1、2,低电平有效。

XFER(PIN17):

数据传送控制信号,低电平有效。

VREF(PIN8):

基准电压,可正可负,-10V~+10V。

RFB(PIN9):

反馈电阻端。

IOUT1/IOUT2(PIN11、12):

电流输出1和2。

D/A转换量是以电流形式输出的,所以必须如实验结构图NO.5C所示的连接方式将电流信号变为电压信号。

AGND/DGND(PIN3、10):

模拟地与数字地。

在高速情况下,此二地的连接线必须尽可能短,且系统的单点接地点须接在此连线的某一点上。

例11-1中的正弦波波型数据由64个点构成,此数据经DAC0832,并经滤波器后,可在示波器上观察到光滑的正弦波(若接精密基准电压,可得到更为清晰的正弦波形)。

3.实验过程

首先根据设计原理,完成基础部分,完成波形发生器和扫频信号源的设计,仿真测试及实验系统上的硬件测试。

(1)、在QuartusII中建立一个工程项目文件.qpf,并在该项目下新建VHDL源程序文件输入源程序代码并保存。

因为我们的设计需要三个模块,所以需要三个程序。

因此我们建立三个VHDL源程序文件。

各模块源程序见附录。

(2)、编译正确后,我们建立一个总的工程ep1c12_27_signal_generator,再在其中加入程序,对其编译,再选择File--create--createsymbolfileforcurrentfile,对相应程序建立模块,将三模块在同一Blockdiagram/Schematicfile中连接起来,分频数设为48000000,添加INPUT和OUTPUT引脚。

模块如下所示:

图二.信号输入模块

图三.分频模块

图四.信号输出模块

(3)选择目标器件并对相应的引脚进行锁定,在这里在这里所选择的目标器件为Altera公司Cyclone系列的EP1C12Q240C8芯片,引脚锁定,将未使用的管脚设置为三态输入。

引脚锁定如下图所示:

图五.工程中引脚锁定图

硬件实验中注意DAC0832及滤波电路须接+/-12V电压。

然后将实验系统左下角选择插针处用短路帽短路“D/A直通”,而“滤波1”,“滤波0”处通过短路或不接短路帽达到不同的滤波方式。

将示波器的地与EDA实验系统的地相接,信号端与“AOUT”信号输出端相接;建议CLK接clock0,由此50MHz频率,此频率扫描波形数据;CLK1接clock5,由此接“1024Hz”,此频率决定扫频速度;选电路模式1;KK接键8,当为高电平时,正弦波点频输出,11位输入数据DATA由键3、键2和键1控制,信号源的输出频率由此3键输入的12位二进制数决定,数值越大,输出频率越高;“FD0”时为最高频率;键8低电平时,正弦波扫频输出,扫频速度由clock5的频率决定。

输向0832的8位数据由DD输出。

(4)、再设计中插入一个LPM_ROM模块,将原例中的波形数据放在内部ROM中。

必要时增加波形点数,以利低频输出时,仍保持良好波形。

波形数据可由其它方式自动生成,然后重复以上的测试和硬件实验。

建立途径是:

tools--magawizardplug_Inmanager--create--storage下的LPM_ROM。

其程序如下见附录。

(5)、对该工程文件进行全程编译处理,若在编译过程中发现错误,则找出并更正错误,直至编译成功为止。

设计整体模块图如下:

图六.设计整体图

四.实验器材

5.实验故障

我们按照要求连接实验各模块后,在示波器上未能显示我们要求得到的正弦波形。

故障1.D/A模块与SmartSOPC实验箱核心模块件电阻没有连接

解决:

我们用跳线按顺序连接了各个引脚

但是这样做完后,并没有出现正弦波形。

故障2.地线连接不够好

解决:

加强了地线的连接

做完此工作后,波形可以出现了。

6.实验心得

附录:

信号输入模块源程序

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_Arith.ALL;

USEIEEE.STD_LOGIC_Unsigned.ALL;

ENTITYsine_testIS

PORT(

clock:

INSTD_LOGIC;--系统时钟

key:

INSTD_LOGIC_VECTOR(3DOWNTO0);

select01:

OUTSTD_LOGIC;--发送数据使能.

data:

OUTSTD_LOGIC_VECTOR(11DOWNTO0);--要发送的数据

seg:

OUTSTD_LOGIC_VECTOR(7DOWNTO0);--数码管段码输出。

dig:

OUTSTD_LOGIC_VECTOR(7DOWNTO0)--数码管位码输出。

);

END;

ARCHITECTUREoneOFsine_testIS

SIGNALdata_r:

STD_LOGIC_VECTOR(11DOWNTO0);

SIGNALselect01_r:

STD_LOGIC;

SIGNALseg_r,dig_r:

STD_LOGIC_VECTOR(7DOWNTO0);

SIGNALcount:

STD_LOGIC_VECTOR(16DOWNTO0);--时钟分频计数器.

SIGNALdout1,dout2,dout3:

STD_LOGIC_VECTOR(3DOWNTO0);--消抖寄存器

SIGNALbuff:

STD_LOGIC_VECTOR(3DOWNTO0);--边沿检测寄存器

SIGNALcnt:

STD_LOGIC_VECTOR(1DOWNTO0);--数码管扫描计数器.

SIGNALdisp_dat:

STD_LOGIC_VECTOR(3DOWNTO0);--数码管扫描显存

SIGNALdiv_clk:

STD_LOGIC;--分频时钟

SIGNALkey_edge:

STD_LOGIC_VECTOR(3DOWNTO0);

BEGIN

PROCESS(clock)--时钟分频部分.

BEGIN

IFRISING_EDGE(clock)THEN

IFcount<120000THEN

count<=count+1;

div_clk<='0';

ELSE

count<=B"0_0000_0000_0000_0000";

div_clk<='1';

ENDIF;

ENDIF;

ENDPROCESS;

----------------------------------<<按键消抖部分

PROCESS(clock)

BEGIN

IFRISING_EDGE(clock)THEN

IFdiv_clk='1'THEN

dout1<=key;

dout2<=dout1;

dout3<=dout2;

ENDIF;

ENDIF;

ENDPROCESS;

PROCESS(clock)--按键边沿检测部分

BEGIN

IFRISING_EDGE(clock)THEN

buff<=dout1ORdout2ORdout3;

ENDIF;

ENDPROCESS;

key_edge<=NOT(dout1ORdout2ORdout3)ANDbuff;

PROCESS(clock)--按键1

BEGIN

IFRISING_EDGE(clock)THEN

IFkey_edge(0)='1'THEN--下降沿检测

data_r(11DOWNTO8)<=data_r(11DOWNTO8)+1;

ENDIF;

ENDIF;

ENDPROCESS;

PROCESS(clock)--按键2

BEGIN

IFRISING_EDGE(clock)THEN

IFkey_edge

(1)='1'THEN--下降沿检测

data_r(7DOWNTO4)<=data_r(7DOWNTO4)+1;

ENDIF;

ENDIF;

ENDPROCESS;

PROCESS(clock)--按键3

BEGIN

IFRISING_EDGE(clock)THEN

IFkey_edge

(2)='1'THEN--下降沿检测

data_r(3DOWNTO0)<=data_r(3DOWNTO0)+1;

ENDIF;

ENDIF;

ENDPROCESS;

PROCESS(clock)--按键4

BEGIN

IFRISING_EDGE(clock)THEN

IFkey_edge(3)='1'THEN--下降沿检测

select01_r<=NOTselect01_r;

ENDIF;

ENDIF;

ENDPROCESS;

PROCESS(clock)--数码管扫描显示部分

BEGIN

IFRISING_EDGE(clock)THEN

IFdiv_clk='1'THEN

cnt<=cnt+1;

ENDIF;

ENDIF;

ENDPROCESS;

PROCESS(clock)

BEGIN

IFRISING_EDGE(clock)THEN

IFdiv_clk='1'THEN

CASEcntIS--选项择扫描显示数据.

WHEN"00"=>disp_dat<=data_r(11DOWNTO8);--第一个数码管.

WHEN"01"=>disp_dat<=data_r(7DOWNTO4);--第二个数码管.

WHEN"10"=>disp_dat<=data_r(3DOWNTO0);--第三个数码管

WHEN"11"=>disp_dat<="000"&select01_r;--第八个数码管

ENDCASE;

CASEcntIS--选择数码管显示示位.

WHEN"00"=>dig_r<="01111111";--选择第一个数码管显示

WHEN"01"=>dig_r<="10111111";--选择第二个数码管显示

WHEN"10"=>dig_r<="11011111";--选择第三个数码管显示

WHEN"11"=>dig_r<="11111110";--选择第八个数码管显示

ENDCASE;

ENDIF;

ENDIF;

ENDPROCESS;

PROCESS(disp_dat)--七段译码

BEGIN

CASEdisp_datIS

WHENX"0"=>seg_r<=X"c0";--显示0

WHENX"1"=>seg_r<=X"f9";--显示1

WHENX"2"=>seg_r<=X"a4";--显示2

WHENX"3"=>seg_r<=X"b0";--显示3

WHENX"4"=>seg_r<=X"99";--显示4

WHENX"5"=>seg_r<=X"92";--显示5

WHENX"6"=>seg_r<=X"82";--显示6

WHENX"7"=>seg_r<=X"f8";--显示7

WHENX"8"=>seg_r<=X"80";--显示8

WHENX"9"=>seg_r<=X"90";--显示9

WHENX"a"=>seg_r<=X"88";--显示a

WHENX"b"=>seg_r<=X"83";--显示b

WHENX"c"=>seg_r<=X"c6";--显示c

WHENX"d"=>seg_r<=X"a1";--显示d

WHENX"e"=>seg_r<=X"86";--显示e

WHENX"f"=>seg_r<=X"8e";--显示f

WHENOTHERS=>seg_r<=X"FF";

ENDCASE;

ENDPROCESS;

seg<=seg_r;

dig<=dig_r;

select01<=select01_r;

data<=data_r;

END;

分频模块源程序

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;--这3个程序包足发应付大部分的VHDL程序设计

USEIEEE.STD_LOGIC_Arith.ALL;

USEIEEE.STD_LOGIC_Unsigned.ALL;

ENTITYint_divIS

GENERIC(N:

Integer:

=3);--此处定义了一个默认值N=3,即电路为3分频电路;

Port

(Clockin:

INSTD_LOGIC;

ClockOut:

OUTSTD_LOGIC

);

END;

ARCHITECTUREDeviderOFint_divIS

SIGNALCounter:

IntegerRANGE0TON-1;

SIGNALTemp1,Temp2:

STD_LOGIC;--信号的声明在结构体内,进程外部

BEGIN

PROCESS(Clockin)

BEGIN

IFRISING_EDGE(Clockin)THEN

IFCounter=N-1THEN

counter<=0;

Temp1<=NotTemp1;

ELSE

Counter<=Counter+1;

ENDIF;

ENDIF;

IFfalling_edge(clockin)THEN

IFCounter=N/2THEN

Temp2<=NOTTemp2;

ENDIF;

ENDIF;

ENDPROCESS;

ClockOut<=Temp1XORTemp2;

END;

信号输出模块源程序

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_Arith.ALL;

USEIEEE.STD_LOGIC_Unsigned.ALL;

ENTITYsineIS

PORT(

clock:

INSTD_LOGIC;--系统时钟

swept_clk:

INSTD_LOGIC;--扫描时钟

select01:

INSTD_LOGIC;--攻能选择,波形产生&扫频.

data:

INSTD_LOGIC_VECTOR(11DOWNTO0);--频率控制.

dout:

OUTSTD_LOGIC_VECTOR(9DOWNTO0);--数据输出.

da_clk:

OUTSTD_LOGIC;--DA时钟输出

da_mode:

OUTSTD_LOGIC--D/A数据模式选择.

);

END;

ARCHITECTUREoneOFsineIS

COMPONENTsin_rom--元器件调用声明.

PORT

(

address:

INSTD_LOGIC_VECTOR(7DOWNTO0);

clock:

INSTD_LOGIC;

q:

OUTSTD_LOGIC_VECTOR(9DOWNTO0)

);

ENDCOMPONENT;

SIGNALload_count:

STD_LOGIC_VECTOR(11DOWNTO0);--数控分频器重装值

SIGNALscan_data:

STD_LOGIC_VECTOR(11DOWNTO0);--扫频控制值

SIGNALcount:

STD_LOGIC_VECTOR(11DOWNTO0);--数控分频计数器

SIGNALrom_clk:

STD_LOGIC;--ROM波表时钟

SIGNALaddr:

STD_LOGIC_VECTOR(7DOWNTO0);--ROM地址.

BEGIN

PROCESS(clock)

BEGIN

IFRISING_EDGE(clock)THEN--选择数控分频器初值.

IFselect01='1'THEN

load_count<=data;--由外部输入.

ELSE

load_count<=scan_data;--由内部扫频产生.

ENDIF;

ENDIF;

ENDPROCESS;

PROCESS(clock)--数控分频器.

BEGIN

IFRISING_EDGE(clock)THEN

IFcount=X"FFF"THEN

count<=load_count;

rom_clk<='1';

ELSE

count<=count+1;

rom_clk<='0';

ENDIF;

ENDIF;

ENDPROCESS;

PROCESS(clock)

BEGIN

IFRISING_EDGE(clock)THEN--产生ROM地址.

IFrom_clk='1'THEN

addr<=addr+1;

ENDIF;

ENDIF;

ENDPROCESS;

PROCESS(swept_clk)

BEGIN

IFRISING_EDGE(swept_clk)THEN

scan_data<=scan_data+1;

ENDIF;

ENDPROCESS;

U1:

sin_romPORTMAP(address=>addr,clock=>rom_clk,q=>dout);

da_clk<=rom_clk;--D/A时钟输出.

da_mode<='0';--D/A数据模式选择以二进制输入.

END;

LPM_ROM模块源程序

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYDACIS

PORT(CLK,CLK1,KK:

INSTD_LOGIC;

DATA:

INSTD_LOGIC_VECTOR(11DOWNTO0);

DD:

OUTINTEGERRANGE255DOWNTO0);

END;

ARCHITECTUREDACCOFDACIS

SIGNALQ:

INTEGERRANGE63DOWNTO0;

SIGNALD:

INTEGERRANGE255DOWNTO0;

SIGNALFSS:

STD_LOGIC;

SIGNALCOUNT12,DATA2,DATA1:

STD_LOGIC_VECTOR(11DOWNTO0);

BEGIN

PROCESS(FSS)

BEGIN

IF(FSS'EVENTANDFSS='1')THENQ<=Q+1;

ENDIF;

ENDPROCESS;

PROCESS(Q)

BEGIN

CASEQIS

WHEN00=>D<=255;WHEN01=>D<=254;WHEN02=>D<=252;WHEN03=>D<=249;

WHEN04=>D<=245;WHEN05=>D<=239;WHEN06=>D<=233;WHEN07=>D<=225;

WHEN08=>D<=217;WHEN09=>D<=207;WHEN10=>D<=197;WHEN11=>D<=186;

WHEN12=>D<=174;WHEN13=>D<=162;WHEN14=>D<=150;WHEN15=>D<=137;

WHEN16=>D<=124;WHEN17=>D<=112;WHEN18=>D<=99;WHEN19=>D<=87;

WHEN20=>D<=75;WHEN21=>D<=64;WHEN22=>D<=53;WHEN23=>D<=43;

WHEN24=>