湘潭大学计算机原理 实验一 算术逻辑运算实验预习报告.docx

《湘潭大学计算机原理 实验一 算术逻辑运算实验预习报告.docx》由会员分享,可在线阅读,更多相关《湘潭大学计算机原理 实验一 算术逻辑运算实验预习报告.docx(18页珍藏版)》请在冰豆网上搜索。

湘潭大学计算机原理实验一算术逻辑运算实验预习报告

实验一算术逻辑单元ALU

一.实验目的

1.理解算术逻辑单元ALU的工作原理。

2.掌握算术逻辑单元ALU的设计方法。

3.验证32位算术逻辑单元ALU的加、减、与、移位功能。

4.按给定数据,完成几种指定的算术和逻辑运算。

二.实验内容

算术逻辑单元ALU的设计如图1-1所示。

其中运算器addsub32能实现32位的加减运算。

参加运算的两个32位数据分别为A[31..0]和B[31..0],运算模式由aluc[3..0]的16种组合决定,而aluc[3..0]的值由4位2进制计数器LPM_COUNTER产生,计数时钟是Sclk(图1-1);r[31..0]为输出结果,Z为运算后的零标志位。

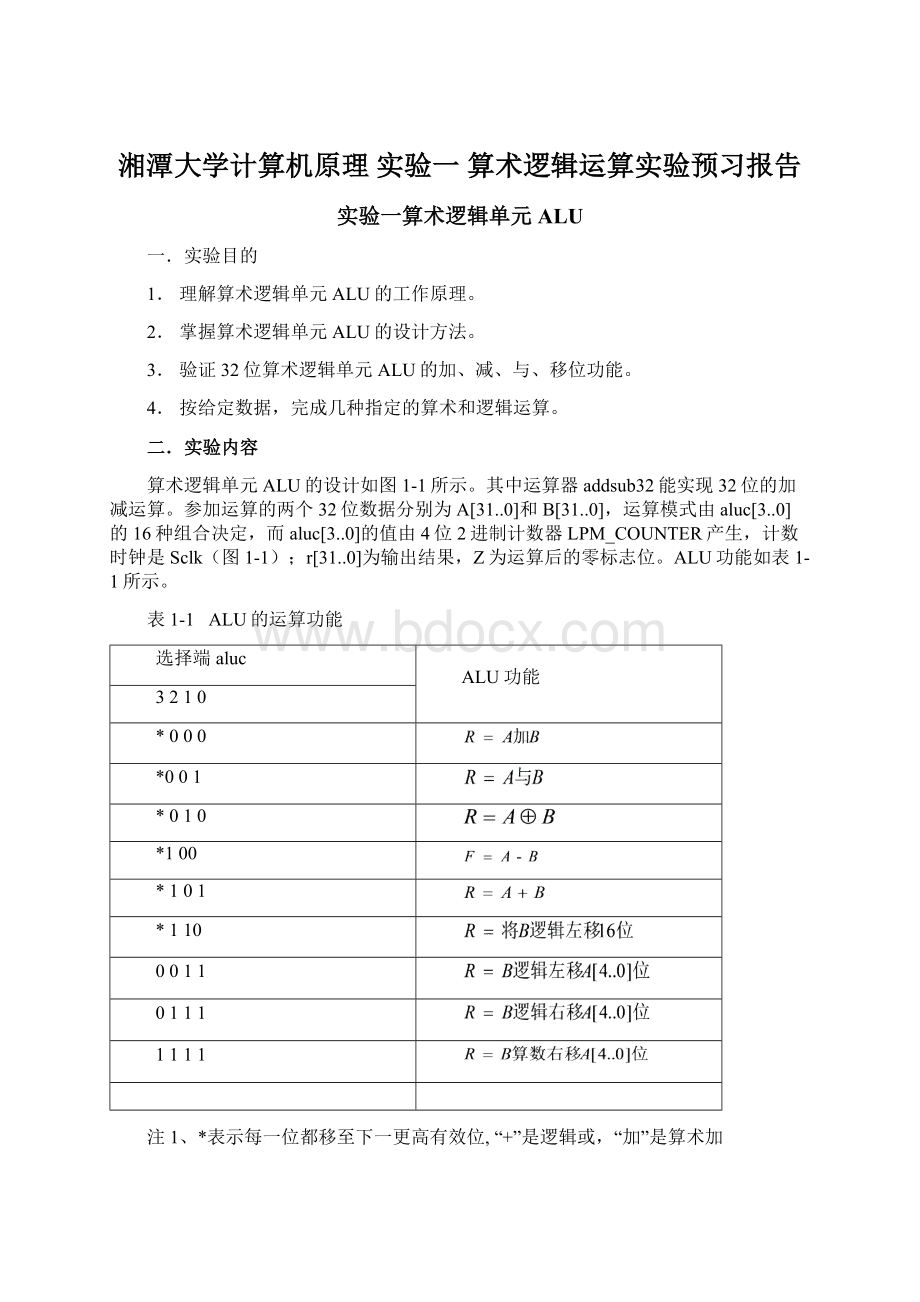

ALU功能如表1-1所示。

表1-1ALU的运算功能

选择端aluc

ALU功能

3210

*000

*001

*010

*100

*101

*110

0011

0111

1111

注1、*表示每一位都移至下一更高有效位,“+”是逻辑或,“加”是算术加

三.实验步骤

(1)设计ALU元件

在QuartusII环境下,用文本输入编辑器TextEditor输入ALU.V算术逻辑单元文件,编译VerilogHDL文件,并将ALU.V文件制作成一个可调用的原理图元件。

(2)以原理图方式建立顶层文件工程

选择图形方式。

根据图1-1输入实验电路图,从QuartusII的基本元件库中将各元件调入图形编辑窗口、连线,添加输入输出引脚。

将所设计的图形文件ALU_sy.bdf保存到原先建立的文件夹中,将当前文件设置成工程文件,以后的操作就都是对当前工程文件进行的。

(3)器件选择

选择Cyclone系列,在Devices中选择器件EP1C12QC240C8。

编译,引脚锁定,再编译。

引脚锁定后需要再次进行编译,才能将锁定信息确定下来,同时生成芯片编程/配置所需要的各种文件。

(4)芯片编程Programming(可以直接选择光盘中的示例已完成的设计进行验证实验)

打开编程窗口。

将配置文件ALU_sy.sof下载进GW48系列现代计算机组成原理系统中的FPGA中。

(5)选择实验系统的电路模式是NO.0,验证ALU的运算器的算术运算和逻辑运算功能

根据表1-1,从键盘输入数据A[7..0]和B[7..0],并设置S[3..0]、M、Cy,验证ALU运算器的算术运算和逻辑运算功能,记录实验数据。

图1-1算术逻辑单元ALU实验原理图

四.实验任务

(1)按图1-1所示,在本验证性示例中用数据选择开关(键3控制)的高/低电平选择总线通道上的8位数据进入对应的数据锁存器lpm_latch中;即首先将键3输入高电平,用键2、键1分别向DA[7..0]置数01010101(55H),这时在数码管4/3上显示输入的数据(55H);然后用键3输入低电平,再用键2、键1分别向DB[7..0]置数10101010(AAH),这时在数码管2/1上显示输入的数据(AAH);这时表示在图1-1中的两个锁存器中分别被锁入了加数55H和被加数AAH。

可双击图1-1的ALU元件,了解其VerilogHDL描述。

(2)键6控制时钟SCLK,可设置表1-1的aluc[3..0]=0~F。

现连续按动键6,设置操作方式选择aluc[3..0]=0000(加法操作),使数码管8显示0,以验证ALU的算术运算功能:

当键7设置clr=0时,数码管6/5=FF(55H+AAH=FFH);

当键7设置cn=1(复位)时,数码管7/6/5=100(Z=1);

键KEY6控制时钟SCLK,设置aluc[3..0]=0~F,KEY7设置clr=0或clr=1,验证ALU的逻辑运算功能,并记录实验数据。

表1-2DA[7..0],DB[7..0]设置值检查

R[7..0]

Z

寄存器内容

ALUC3210

CLR

DA[7..0]

DB[7..0]

01010101

1010101010

01010101

1010101010

(3)验证ALU的算术运算和逻辑运算功能,ALU模块功能可参照表1-1。

表1-3给定了寄存器DRl=DA[7..0]和DR2=DB[7..0]的数据(十六进制),要求根据此数据对照逻辑功能表所得的理论值(要求课前完成)与实验结果值进行比较(均采用正逻辑0)。

表1-3

ALUC3210

DA[7..0]

DB[7..0]

ALU功能

运算结果R[7..0](CLR=0)

0000

AA

55

0001

AA

55

0010

AA

55

0011

AA

55

0100

FF

01

0101

FF

01

0110

FF

01

0111

FF

01

1000

FF

FF

1001

FF

FF

1010

FF

FF

1011

FF

FF

1100

55

01

1101

55

01

1110

55

01

1111

55

01

五.实验要求

1、做好实验预习,掌握运算器的数据传送通路和ALU的功能特性,并熟悉本实验中所用的控制台开关的作用和使用方法。

2、写出实验报告,内容是:

①实验目的;

②按理论分析值填写好表1-2、表1-3,给出对应的仿真波形。

③列表比较实验数据

(2)的理论分析值与实验结果值;并对结果进行分析。

实验结果与理论分析值比较,有没有不同?

为什么?

④通过本实验,你对运算器ALU有何认识,有什么心得体会?

六.实验题与思考题

1.用VerilogHDL实现输入暂存器lpm_latch的功能,及模式选择计数器LPM_COUNTER的功能。

2.用VerilogHDL表达整个ALU实验电路的功能,对电路进行仿真、引脚锁定、并在实验台上实现其功能。

3.用VerilogHDL设计一个64位的ALU,实现基本的算术逻辑运算。

4.对ALU进行算术运算和逻辑运算的功能仿真,并记录仿真波形。

附录:

GW48CP+主系统使用说明

第一节GW48教学实验系统原理与使用介绍

一、GW48系统使用注意事项(用户必读!

!

!

)

a:

闲置不用GW48系统时,必须关闭电源!

!

!

b:

在实验中,当选中某种模式后,要按一下右侧的复位键,以使系统进入该结构模式工作。

注意此复位键仅对实验系统的监控模块复位,而对目标器件FPGA没有影响,FPGA本身没有复位的概念,上电后即工作,在没有配置前,FPGA的I/O口是随机的,故可以从数码管上看到随机闪动,配置后的I/O口才会有确定的输出电平。

c:

换目标芯片时要特别注意,不要插反或插错,也不要带电插拔,确信插对后才能开电源。

其它接口都可带电插拔。

请特别注意,尽可能不要随意插拔适配板,及实验系统上的其他芯片。

二、GW48系统主板结构与使用方法

以下将详述GW48系列实验系统结构与使用方法,对于这2种型号的不同之处将给予单独指出。

该系统的实验电路结构是可控的。

即可通过控制接口键,使之改变连接方式以适应不同的实验需要。

因而,从物理结构上看,实验板的电路结构是固定的,但其内部的信息流在主控器的控制下,电路结构将发生变化---重配置。

这种“多任务重配置”设计方案的目的有3个:

1、适应更多的实验与开发项目;2、适应更多的PLD公司的器件;3、适应更多的不同封装的FPGA和CPLD器件。

系统板面主要部件及其使用方法说明如下。

以下是对GW48系统主板功能块的注释。

(1)“模式选择键”:

按动该键能使实验板产生12种不同的实验电路结构。

这些结构如第二节的13张实验电路结构图所示。

例如选择了“NO.3”图,须按动系统板上此键,直至数码管“模式指示”数码管显示“3”,于是系统即进入了NO.3图所示的实验电路结构。

(2)适配板:

这是一块插于主系统板上的目标芯片适配座。

对于不同的目标芯片可配不同的适配座。

可用的目标芯片包括目前世界上最大的六家FPGA/CPLD厂商几乎所有CPLD、FPGA和所有ispPAC等模拟EDA器件。

第七节的表中已列出多种芯片对系统板引脚的对应关系,以利在实验时经常查用。

(3)ByteBlasterMV编程配置口:

如果要进行独立电子系统开发、应用系统开发、电子设计竞赛等开发实践活动,首先应该将系统板上的目标芯片适配座拔下(对于Cyclone器件不用拔),用配置的10芯编程线将“ByteBlasterMV”口和独立系统上适配板上的10芯口相接,进行在系统编程(如GWDVP-B板),进行调试测试。

“ByteBlasterMV”口能对不同公司,不同封装的CPLD/FPGA进行编程下载,也能对isp单片机89S51等进行编程。

编程的目标芯片和引脚连线可参考附图1,从而进行二次开发。

(4)ByteBlasterII编程配置口:

该口主要用于对Cyclone系列AS模式专用配置器件EPCS4和EPCS1等编程。

附图1GW48系统电子设计二次开发信号图

(5)混合工作电压源:

系统不必通过切换即可为CPLD/FPGA目标器件提供5V、3.3V、2.5V、1.8V和1.5V工作电源,此电源位置可参考附图1。

(6)并行下载口:

此接口通过下载线与微机的打印机口相连。

来自PC机的下载控制信号和CPLD/FPGA的目标码将通过此口,完成对目标芯片的编程下载。

计算机的并行口通信模式最好设置成“EPP”模式。

(7)键1~键8:

为实验信号控制键,此8个键受“多任务重配置”电路控制,它在每一张电路图中的功能及其与主系统的连接方式随模式选择键的选定的模式而变,使用中需参照第二节中的电路图。

(8)数码管1~8/发光管D1~D16:

受“多任务重配置”电路控制,它们的连线形式也需参照第二节的电路图。

(9)“时钟频率选择”:

位于主系统的右小侧,通过短路帽的不同接插方式,使目标芯片获得不同的时钟频率信号。

对于“CLOCK0”,同时只能插一个短路帽,以便选择输向“CLOCK0”的一种频率:

信号频率范围:

0.5Hz–50MHz。

由于CLOCK0可选的频率比较多,所以比较适合于目标芯片对信号频率或周期测量等设计项目的信号输入端。

右侧座分三个频率源组,它们分别对应三组时钟输入端:

CLOCK2、CLOCK5、CLOCK9。

例如,将三个短路帽分别插于对应座的2Hz、1024Hz和12MHz,则CLOCK2、CLOCK5、CLOCK9分别获得上述三个信号频率。

需要特别注意的是,每一组频率源及其对应时钟输入端,分别只能插一个短路帽。

也就是说最多只能提供4个时钟频率输入FPGA:

CLOCK0、CLOCK2、CLOCK5、CLOCK9。

(10)扬声器:

与目标芯片的“SPEAKER”端相接,通过此口可以进行奏乐或了解信号的频率,它与目标器件的具体引脚号,应该查阅附录第3节的表格。

(11)PS/2接口:

通过此接口,可以将PC机的键盘和/或鼠标与GW48系统的目标芯片相连,从而完成PS/2通信与控制方面的接口实验,GW48-GK/PK2含另一PS/2接口,引脚连接情况参见实验电路结构NO.5(附图7)。

(12)VGA视频接口:

通过它可完成目标芯片对VGA显示器的控制。

详细连接方式参考附图7(对GW48-PK2主系统),或附图13(GW48-CK主系统)。

(13)单片机接口器件:

它与目标板的连接方式也已标于主系统板上:

连接方式可参见附图11。

注1、对于GW48-PK2系统,实验板右侧有一开关,若向“TO_FPGA”拨,将RS232通信口直接与FPGA相接;若向“TO_MCU”拨,则与89S51单片机的P30和P31端口相接。

于是通过此开关可以进行不同的通信实验,详细连接方式可参见附图11。

平时此开关应该向“TO_MCU”拨,这样可不影响FPGA的工作!

(14)RS-232串行通讯接口:

此接口电路是为FPGA与PC通讯和SOPC调试准备的。

或使PC机、单片机、FPGA/CPLD三者实现双向通信。

对于GW48-EK系统,其通信端口是与中间的双排插座上的TX30、RX31相连的。

详细连接方式参考附图11。

(15)“AOUT”D/A转换:

利用此电路模块,可以完成FPGA/CPLD目标芯片与D/A转换器的接口实验或相应的开发。

它们之间的连接方式可参阅附图7(实验电路结构NO.5):

D/A的模拟信号的输出接口是“AOUT”,示波器可挂接左下角的两个连接端。

当使能拨码开关8:

“滤波1”时,D/A的模拟输出将获得不同程度的滤波效果。

注意,进行D/A接口实验时,需打开系统上侧的+/-12V电源开关(实验结束后关上此电源!

)。

(16)“AIN0”/“AIN1”:

外界模拟信号可以分别通过系统板左下侧的两个输入端“AIN0”和“AIN1”进入A/D转换器ADC0809的输入通道IN0和IN1,ADC0809与目标芯片直接相连。

通过适当设计,目标芯片可以完成对ADC0809的工作方式确定、输入端口选择、数据采集与处理等所有控制工作,并可通过系统板提供的译码显示电路,将测得的结果显示出来。

此项实验首先需参阅第二节的“实验电路结构NO.5”有关0809与目标芯片的接口方式,同时了解系统板上的接插方法以及有关0809工作时序和引脚信号功能方面的资料。

注意:

不用0809时,需将左下角的拨码开关的“A/D使能”和“转换结束”打为禁止:

向上拨,以避免与其他电路冲突。

ADC0809A/D转换实验接插方法(如,附图7,实验电路结构NO.5图所示):

1.左下角拨码开关的“A/D使能”和“转换结束”拨为使能:

向下拨,即将ENABLE(9)与PIO35相接;若向上拨则禁止,即则使ENABLE(9)0,表示禁止0809工作,使它的所有输出端为高阻态。

2.左下角拨码开关的“转换结束”使能,则使EOC(7)PIO36,由此可使FPGA对ADC0809的转换状态进行测控。

(17)VR1/“AIN1”:

VR1电位器,通过它可以产生0V~+5V幅度可调的电压。

其输入口是0809的IN1(与外接口AIN1相连,但当AIN1插入外输入插头时,VR1将与IN1自动断开)。

若利用VR1产生被测电压,则需使0809的第25脚置高电平,即选择IN1通道,参考“实验电路结构NO.5”。

(18)AIN0的特殊用法:

系统板上设置了一个比较器电路,主要以LM311组成。

若与D/A电路相结合,可以将目标器件设计成逐次比较型A/D变换器的控制器件参考“实验电路结构NO.5”。

(19)系统复位键:

此键是系统板上负责监控的微处理器的复位控制键,同时也与接口单片机和LCD控制单片机的复位端相连。

因此兼作单片机的复位键。

(20)跳线座SPS:

短接“T_F”可以使用“在系统频率计”。

频率输入端在主板右侧标有“频率计”处。

模式选择为“A”。

短接“PIO48”时,信号PIO48可用,如实验电路结构图NO.1中的PIO48。

平时应该短路“PIO48”。

(21)目标芯片万能适配座CON1/2:

在目标板的下方有两条80个插针插座(GW48-CK系统),其连接信号如附图1所示,此图为用户对此实验开发系统作二次开发提供了条件。

对于GW48-GK/PK2/EK系统,此适配座在原来的基础上增加了20个插针,功能大为增强。

增加的20插针信号与目标芯片的连接方式可参考“实验电路结构NO.5”、附图11和第3节表格。

GW48-EK系统中此20的个插针信号全开放。

(22)+/-12V电源开关:

在实验板左上角。

有指示灯。

电源提供对象:

1)与082、311及DAC0832等相关的实验;2)模拟信号发生源;3)GW48-DSP/DSP+适配板上的D/A及参考电源;此电源输出口可参见附图1。

平时,此电源必须关闭!

(23)模拟信号发生源:

(GK/PK2型含此)信号源主要用于DSP/SOPC实验及A/D高速采样用信号源。

使用方法如下:

1)打开+/-12V电源;2)用一插线将右下角的某一频率信号(如65536Hz)连向单片机上方插座“JP18”的INPUT端;3)这时在“JP17”的OUTPUT端及信号挂钩“WAVEOUT”端同时输出模拟信号,可用示波器显示输出模拟信号(这时输出的频率也是65536Hz);4)实验系统右侧的电位器上方的3针座控制输出是否加入滤波:

向左端短路加滤波电容;向右短路断开滤波电容;5)此电位器是调谐输出幅度的,应该将输出幅度控制在0-5V内。

(24)使用举例:

若模式键选中了“实验电路结构图NO.1”,这时的GW48系统板所具有的接口方式变为:

FPGA/CPLD端口PI/O31~28(即PI/O31、PI/O30、PI/O29、PI/O28)、PI/O27~24、PI/O23~20和PI/O19~16,共4组4位二进制I/O端口分别通过一个全译码型7段译码器输向系统板的7段数码管。

这样,如果有数据从上述任一组四位输出,就能在数码管上显示出相应的数值,其数值对应范围为:

FPGA/CPLD输出

0000

0001

0010

…

1100

1101

1110

1111

数码管显示

0

1

2

…

C

D

E

F

端口I/O32~39分别与8个发光二极管D8~D1相连,可作输出显示,高电平亮。

还可分别通过键8和键7,发出高低电平输出信号进入端口I/049和48;键控输出的高低电平由键前方的发光二极管D16和D15显示,高电平输出为亮。

此外,可通过按动键4至键1,分别向FPGA/CPLD的PIO0~PIO15输入4位16进制码。

每按一次键将递增1,其序列为1,2,…9,A,…F。

注意,对于不同的目标芯片,其引脚的I/O标号数一般是同GW48系统接口电路的“PIO”标号是一致的(这就是引脚标准化),但具体引脚号是不同的,而在逻辑设计中引脚的锁定数必须是该芯片的具体的引脚号。

具体对应情况需要参考第3节的引脚对照表。

第二节实验电路结构图

1.实验电路信号资源符号图说明

结合附图2-1,以下对实验电路结构图中出现的信号资源符号功能作出一些说明:

附图2A实验电路信号资源符号图

(1)附图2-1a是16进制7段全译码器,它有7位输出,分别接7段数码管的7个显示输入端:

a、b、c、d、e、f和g;它的输入端为D、C、B、A,D为最高位,A为最低位。

例如,若所标输入的口线为PIO19~16,表示PIO19接D、18接C、17接B、16接A。

(2)附图2-1b是高低电平发生器,每按键一次,输出电平由高到低、或由低到高变化一次,且输出为高电平时,所按键对应的发光管变亮,反之不亮。

(3)附图2A-1c是16进制码(8421码)发生器,由对应的键控制输出4位2进制构成的1位16进制码,数的范围是0000~1111,即^H0至^HF。

每按键一次,输出递增1,输出进入目标芯片的4位2进制数将显示在该键对应的数码管上。

(4)直接与7段数码管相连的连接方式的设置是为了便于对7段显示译码器的设计学习。

以图NO.2为例,如图所标“PIO46-PIO40接g、f、e、d、c、b、a”表示PIO46、PIO45..PIO40分别与数码管的7段输入g、f、e、d、c、b、a相接。

(5)附图2-1d是单次脉冲发生器。

每按一次键,输出一个脉冲,与此键对应的发光管也会闪亮一次,时间20ms。

(6)附图2-1e是琴键式信号发生器,当按下键时,输出为高电平,对应的发光管发亮;当松开键时,输出为高电平,此键的功能可用于手动控制脉冲的宽度。

具有琴键式信号发生器的实验结构图是NO.3。

2.各实验电路结构图特点与适用范围简述

(1)结构图NO.0:

目标芯片的PIO19至PIO44共8组4位2进制码输出,经外部的7段译码器可显示于实验系统上的8个数码管。

键1和键2可分别输出2个四位2进制码。

一方面这四位码输入目标芯片的PIO11~PIO8和PIO15~PIO12,另一方面,可以观察发光管D1至D8来了解输入的数值。

例如,当键1控制输入PIO11~PIO8的数为^HA时,则发光管D4和D2亮,D3和D1灭。

电路的键8至键3分别控制一个高低电平信号发生器向目标芯片的PIO7至PIO2输入高电平或低电平,扬声器接在“SPEAKER”上,具体接在哪一引脚要看目标芯片的类型,这需要查第3节的引脚对照表。

如目标芯片为FLEX10K10,则扬声器接在“3”引脚上。

目标芯片的时时钟输入未在图上标出,也需查阅第3节的引脚对照表。

例如,目标芯片为XC95108,则输入此芯片的时钟信号有CLOCK0至CLOCK9,共4个可选的输入端,对应的引脚为65至80。

具体的输入频率,可参考主板频率选择模块。

此电路可用于设计频率计,周期计,计数器等等。

(2)结构图NO.1:

适用于作加法器、减法器、比较器或乘法器等。

例如,加法器设计,可利用键4和键3输入8位加数;键2和键1输入8位被加数,输入的加数和被加数将显示于键对应的数码管4-1,相加的和显示于数码管6和5;可令键8控制此加法器的最低位进位。

(3)结构图NO.2:

可用于作VGA视频接口逻辑设计,或使用数码管8至数码管5共4个数码管作7段显示译码方面的实验;而数码管4至数码管1,4个数码管可作译码后显示,键1和键2可输入高低电平。

(4)结构图NO.3:

特点是有8个琴键式键控发生器,可用于设计八音琴等电路系统。

也可以产生时间长度可控的单次脉冲。

该电路结构同结构图NO.0一样,有8个译码输出显示的数码管,以显示目标芯片的32位输出信号,且8个发光管也能显示目标器件的8位输出信号。

(5)结构图NO.4:

适合于设计移位寄存器、环形计数器等。

电路特点是,当在所设计的逻辑中有串行2进制数从PIO10输出时,若利用键7作为串行输出时钟信号,则PIO10的串行输出数码可以在发光管D8至D1上逐位显示出来,这能很直观地看到串出的数值。

(6)结构图NO.5:

此电路结构有较强的功能,主要用于目标器件与外界电路的接口设计实验。

主要含以9大模块:

1.普通内部逻辑设计模块。

在图的左下角。

此模块与以上几个电路使用方法相同,例如同结构图NO.3的唯一区别是8个键控信号不再是琴键式电平输出,而是高低电平方式向目标芯片输入。

此电路结构可完成许多常规的实验项目。

3.VGA视频接口。

4.两个PS/2键盘接口。

5.A/D转换接口。

6.D/A转换接口。

7.LM311接口。

8.单片机接口。

9.RS232通信接口。

注意,结构图NO.5中并不是所有电路模块都可以同时使用,这是因为各模块与目标器件的IO接口有重合:

1.当使用RAM/ROM时,数码管3、4、5、6、7、8共6各数码管不能同时使用,这时,如果有必要使用更多的显示,必须使用以下介绍的扫描显示电路。

但RAM/ROM可以与D/A转换同时使用,尽管他们的数据口(PIO24、25、26、27、28、29、30、31)是重合的。

这时如果希望将RAM/ROM中的数据输入D/A中,可设定目标器件的PIO24、25、26、27、28、29、30、31端口为高阻态;而如果希望用目标器件FPGA直接控制D/A器件,可通过拨码开关禁止RAM/ROM数据口。

RAM/ROM能与VGA同时使用,但不能与PS/2同时使用,这时可以使用以下介绍的PS/2接口。

2.A/D不能与RAM/ROM同时使用,由于他们有