移动通信实验1抗衰落技术.docx

《移动通信实验1抗衰落技术.docx》由会员分享,可在线阅读,更多相关《移动通信实验1抗衰落技术.docx(17页珍藏版)》请在冰豆网上搜索。

移动通信实验1抗衰落技术

第一章抗衰落技术

实验一卷积码编码及译码实验

一、实验目的

通过本实验掌握卷积编码的特性、产生原理及方法,卷积码的译码方法,尤其是维特比译码的原理、过程、特性及其实现方法。

二、实验内容

1、观察NRZ基带信号及其卷积编码信号。

2、观察帧同步信号的生成及巴克码的特性。

3、观察卷积编码信号打孔及码速率匹配方法。

4、观察接收端帧同步过程及帧同步信号。

5、观察译码结果并深入理解维特比译码的过程。

6、观察随机过失及突发过失对卷积译码的影响。

三、根本原理

1、卷积码编码

卷积码是一种纠错编码,它将输入的k个信息比特编成n个比特输出,特别适合以串行形式进展传输,时延小。

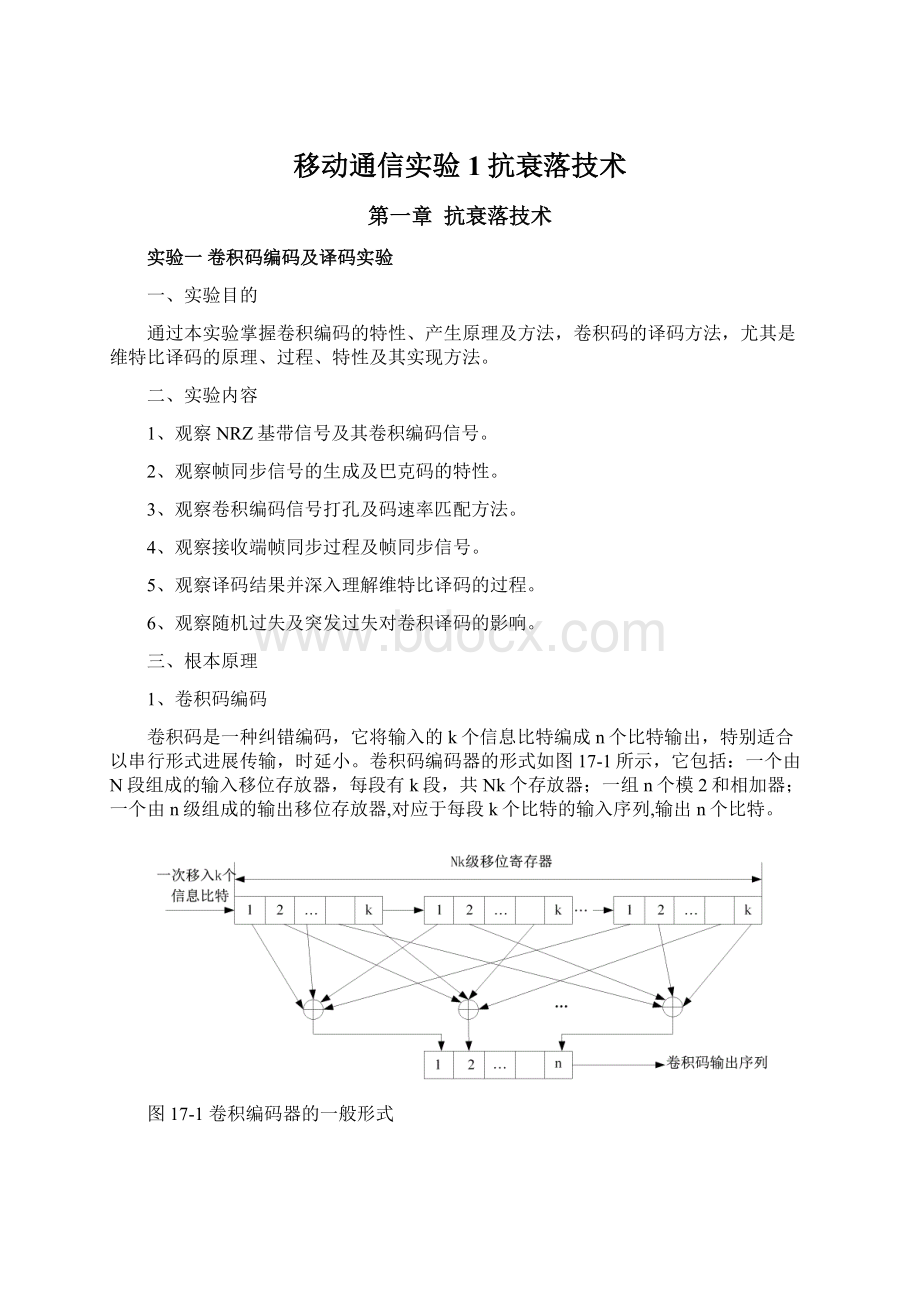

卷积码编码器的形式如图17-1所示,它包括:

一个由N段组成的输入移位存放器,每段有k段,共Nk个存放器;一组n个模2和相加器;一个由n级组成的输出移位存放器,对应于每段k个比特的输入序列,输出n个比特。

图17-1卷积编码器的一般形式

由图17-1可以看到,n个输出比特不仅与当前的k个输入信息有关,还与前〔N-1〕k个信息有关。

通常将N称为约束长度〔有的书中也把约束长度定为nN或N-1〕。

常把卷积码记为:

〔n、k、N〕,当k=1时,N-1就是存放器的个数。

编码效率定义为:

卷积码的表示方法有图解表示法和解析表示法两种:

解析法,它可以用数学公式直接表达,包括离散卷积法、生成矩阵法、码生成多项式法;图解表示法,包括树状图、网络图和状态图〔最的图形表达形式〕三种。

一般情况下,解析表示法比拟适合于描述编码过程,而图形法比拟适合于描述译码。

〔1〕图解表示法

下面以〔2,1,3〕卷积编码器为例详细讲述卷积码的产生原理和表示方法。

〔2,1,3〕卷积码的约束长度为3,编码速率为1/2,编码器的构造如图17-2所示。

图17-2〔2,1,3〕卷积编码器

如图17-2所示,卷积码的输出信息p1,j,p2,j不仅与本地输入信息

有关,还与已存入到存放器的

、

有关,关系式为:

假定移位存放器的初始状态mj-1、mj-2为00,那么当第一个输入比特mj为0时,由式〔17-2〕可知,输出的比特为00;当第一个输入比特mj为1时,输出的比特为11。

随着后面比特的相继输入,存放器中的比特相继右移,此时输出比特按照式〔17-2〕可以依次算得。

随着信息序列的不断输入,卷积编码器可能产生的各种序列可以用如图17-3所示的树状图表示。

树状图中,每条树杈上所标注的码元为输出比特,每个节点上标注对a、b、c、d分别为移位存放器的状态,a表示mj-2mj-1=00,b表示mj-2mj-1=01,c表示mj-2mj-1=10,d表示mj-2mj-1=11,一般情况下,共有2N-1种状态。

每条树叉上所标注的码元为输出比特p1,jp2,j,每条树叉的上支路对应输入比特0,下支路对应输入比特1。

树状图从a点开场画,此时移位存放器状态为00。

当第一个输入比特mj为0时,输出比特特p1,jp2,j为00;mj为1时,输出比特p1,jp2,为11。

所以从最左边的a点出发有两条支路可认选择,mj为0时取上支路,mj为1时取下支路。

依次类推可以得到如图17-3所示的树状图。

图17-3〔2,1,3〕卷积码的树状图

对于第

个输入比特有

条支路,但当

时,移位存放器〔树状图的节点〕开场重复出现四个状态。

把图17-3中一样状态的节点合并在一起,可以得到卷积码的另外一种表示形式:

网格图。

在网格图中,输入比特mj为0〔对应码树中的上支路〕时用实线表示,输入比特mj为1〔对应码树中的下支路〕时用虚线表示,各支路上标注的码元为输出比p1,jp2,j,比自上面下的四行节点分别表示abcd四种状态。

〔2,1,3〕卷积码的网格图如图17-4所示。

由图17-4可知,从左至右第N节开场,网格图开场重复而完全一样。

取出图17-4中从第N节起的一节网格,便可得到图17-5所示的状态图。

状态图中的约定与前面的网络图和树状图一样,实线表示输入比特mj为0,虚线表示输入比特mj为1。

图17-4〔2,1,3〕卷积码的网格图

图17-5〔2,1,3〕卷积码的状态图

〔2〕解析法

这里我们主要介绍码多项式法。

我们可以用多项式来表示输入序列、输出序列、编码器中移位存放器与模2和的连接关系。

为了简化,仍以上述〔2,1,3〕卷积码为例,例如输入序列1011100…可表示为

在一般情况下,输入序列可表示为

这里m1,m2,m3,m4…为二进制表示〔1或0〕的输入序列。

x称为移位算子或延迟算子,它标志着位置状况。

我们可以用多项式表示移位存放器各级与模2加的连接关系。

假设某级存放器与模2加相连接,那么相应多项式项的系数为1;反之,无连接线时的相应多项式项系数为0,以图17-2编码器为例,相应的生成多项式为

利用生成多项式与输入序列多项式相乘,可以产生输出序列多项式,即得到输出序列。

对应的码组为

2、卷积码译码

卷积码的译码方法有两类:

一类是大数逻辑译码,又称门限译码;另一类是概率译码,概率译码又能分为维特比译码和序列译码两种。

门限译码方法是以分组理论为根底的,其译码设备简单,速度快,但其误码性能要比概率译码法差。

这里我们主要介绍维特比译码。

维特比〔Viterbi〕译码和序列译码都属于概率译码。

当卷积码的约束长度不太大时,与序列译码相比,维特比译码器比拟简单,计算速度更快。

维特比译码算法,以后简称VB算法。

采用概率译码的一种根本想法是:

把已接收序列与所有可能的发送序列做比拟,选择其中码距最小的一个序列做为发送序列。

如果发送L组信息比特对于

卷积码来说,可能发送的序列有

个,计算机或译码器需存储这些序列并进展比拟,以找到码距最小的那个序列。

当传信率和信息组数L较大时,使得译码器难以实现。

VB算法那么对上述概率译码〔又称最大似然解码〕做了简化,以至成为了一种实用化的概率算法。

它并不是在网格图上一次比拟所有可能的

条路径〔序列〕,而是接收一段,计算和比拟一段,选择一段有最大似然可能的码段,从而到达整个码序列是一个有最大似然值的序列。

下面将用图17-2的〔2,1,3〕卷积码编码器所编出的码为例,来说明维特比解码的方法和运作过程。

为了能说明解码过程,这里给出该码的状态图,如图17-5所示。

维特比译码需要利用图来说明译码过程。

根据前面的画网格的例子,读者可检验和画个该码网格图如图17-4所示。

该图设输入信息数目L=5,所以画有L+N=8个时间单位〔节点〕。

这里设编码器从a状态开场运作。

该网格图的每一条路径都对应着不同的输入信息序列。

由于所有的可能输入信息序列共有

个,因而网格图中所有可能路径也有

条。

这里节点a=00,b=01,c=10,d=11。

设输入编码器的信息序列为(11011000),那么由编码器输出的序列Y=(1101010001011100),编码器的状态转移路线为abcdbdca。

假设收到的序列R=〔0101011001011100〕,对照网格图来说明维特比译码的方法。

由于该卷积码的约束长度为6位,因此先选择接收序列的前6位序列

=〔010101〕同到达第3时刻可能的8个码序列〔即8条路径〕进展比拟,并计算出码距。

该例中到达第3时刻

点的路径序列是〔000000〕和〔111011〕,它们与

的距离分别是3和4;到达第3时刻

点的路径序列是〔000011〕和〔111000〕,它们与

的距离分别是3和4,到达第3时刻

点的路径序列是〔001110〕和〔110101〕,与

的距离分别是4和1;到达第3时刻

点的路径序列是〔001101〕和〔110110〕,与

的距离分别是2和3。

上述每个节点都保存码距较小的路径为幸存路径,所以幸存路径码序列是〔000000〕、〔000011〕、〔110101〕和〔001101〕,如图17-6〔a〕所示。

用与上面类同的方法可以得到第4、5、6、7时刻的幸存路径。

需指出对于某一个节点而言比拟两条路径与接收序列的累计码距时,假设发生两个码距值相等,那么可以任选一路径作为幸存路径,此时不会影响最终的译码结果。

图17-6〔b〕给出了第5时刻的幸存路径,读者可自行验证。

在码的终了时刻a状态,得到一根幸存路径,如图17-6〔c〕所示。

由此看到译码器输出是

=〔1101010001011100〕,即可变换成序列〔11011000〕,恢复了发端原始信息。

比拟

和

序列,可以看到在译码过程中己纠正了在码序列第1和第7位上的过失。

当然,过失出现太频繁,以至超出卷积码的纠错能力,那么会发生误纠,这是不希望的。

图17-6维特比译码图解

〔a〕第3时刻幸存路径;〔b〕第5时刻幸存路径;〔b〕第8时刻幸存路径

从译码过程看到,维特比算法所需要的存储量是

,在上例中仅为8。

这对于约束长度N<10的译码是很有吸引力的。

四、实验原理

1、实验模块简介

本实验需用到基带成形模块、信道编码及交织模块〔以下简称编码模块〕及信道译码及解交织模块〔以下简称译码模块〕。

〔1〕基带成形模块:

本模块主要功能:

产生PN31伪随机序列作为信源;将基带信号进展串并转换;按调制要求进展基带成形,形成两路正交基带信号。

本实验只用该模块输出的位同步信号作为编码模块的基带信号驱动源。

〔2〕信道编码及交织模块:

本模块主要功能:

产生PN31伪随机序列作为信源,并进展〔2,1,4〕卷积编码,然后可选择有无块交织,再加上帧同步信号组成成帧数据后输出,输出的码可以选择有无过失、随机过失或突发过失。

〔3〕信道译码及解交织模块:

本模块主要功能:

完成帧同步捕获,同步后取出信息元进展〔2,1,4〕维特比卷积译码及解交织。

2、实验框图

3、编码输出帧格式

A:

帧同步头,为11位巴克码:

。

B:

经卷积编码、打孔后的信息数据,共484位。

C:

帧数据补足位,共1位,固定为0。

4、卷积编码生成多项式

本实验采用〔2,1,4〕卷积编码,生成多项式为:

·

G0=x3+x2+1

G1=x3+x2+x+1

5、实验原理

编码时,输入16K时钟信号,经2分频后驱动PN31伪随机码发生器,输出8K速率、一个周期31位的PN码。

PN31码每8个周期〔248bits〕组成一组,加上4个全0尾比特,形成252位一组的数据,经卷积编码后输出504位,然后打孔,每25位打掉一位,即每25位去掉一位,共去掉20位,变为484位〔打孔的目的是使数据输出满足速率要求〕,然后放入数据帧中,形成496位一组的数据包,用16K速率输出。

数据包可按实验要求设置随机误码或突发误码。

译码时,首先用滑动相关法捕获帧同步信号,获得帧同步后,取出484位的信息数据,根据打孔算法补上被打掉的数据位,由于被打掉的数据位已无法知道是0还是1,在本实验中全部补为0。

经补位后,数据复原为504位一组,送入卷积译码器进展维特比译码,译码完成后输出252位数据,去掉4位尾比特,将248bits数据用8K速率输出,完成译码。

五、实验步骤

1、在实验箱上正确安装基带成形模块〔以下简称基带模块〕、信道编码及交织模块〔以下简称编码模块〕及信道译码及交织模块〔以下简称译码模块〕。

2、卷积码编码实验。

a﹑用台阶插座线完成如下连接:

源端口

目的端口

连线说明

基带模块:

BS

编码模块:

BSIN

提供时钟信号

编码模块:

NRZD

编码模块:

PN31

提供PN31信号

*检查连线是否正确,检查无误后翻开电源。

b﹑观察PN31发生器输出信号

用示波器探头分别接编码模块上“BSIN〞和“PN31〞端信号,观察“PN31〞端信号应为8K伪随机码。

c﹑观察编码输出信号及帧同步信号

用示波器探头分别接编码模块上“编码OUT〞及“FSOUT〞测试点,观察编码输出信号及帧同步信号,写出帧同步信号序列。

d﹑观察随机过失和突发过失情况

示波器探头分别接编码模块上“编码OUT〞及“ERROR〞测试点,并将该模块上拨码开关“过失〞位拨向上,其它位向下,观察随机过失情况〔为方便观察,实际上是伪随机过失〕。

将拨码开关“过失〞、“错型〞位拨向上,其它位向下,观察突发过失情况。

e、将编码模块和译码模块上各拨位开关拨向下,关闭实验箱总电源。

3、进展卷积码译码实验。

a﹑保持上面连线不变,用台阶插座线继续连线:

源端口

目的端口

连线说明

编码模块:

BSOUT

译码模块:

BSIN

提供时钟信号

编码模块:

编码OUT

译码模块:

编码IN

将已编码信号进展译码

编码模块:

原码OUT

译码模块:

原码IN

方便译码端信号的比照

*检查连线是否正确,检查无误后翻开电源。

b、示波器探头分别接译码模块上“编码IN〞及“FSOUT〞测试点,观察编码输出信号和帧同步信号。

c﹑比照观察原码和译码后信号

示波器探头分别接译码模块上“译码OUT〞及“原码OUT〞测试点,比拟译码结果是否正确,假设发现不正确按编码模块复位键或译码模块复位键即可正确。

d﹑将编码模块上拨位开关“过失〞位拨向上,其它位拨下,示波器探头分别接译码模块上“译码OUT〞及“原码OUT〞测试点,比照观察在随机过失情况下的译码结果。

e﹑将编码模块上拨位开关“过失〞、“错型〞位拨向上,其它位拨下,观察在突发过失情况下的译码结果。

f﹑在比拟译码结果是否正确时,可借助译码模块上的“ERROR〞测试点的信号确定错码位的位置。

该测试点的信号指示相对于输入的原码而言哪个位发生了错误,假设该点无信号表示没有发现错码。

六、思考题

1、卷积编码后的信号打孔对译码有何影响?

2、为什么要在编码后的信号前加上帧同步头?

实验二块交织及解交织实验

一、实验目的

通过本实验掌握块交织的特性、产生原理及方法,掌握块交织对译码性能的影响。

二、实验内容

1、观察经交织后的卷积编码信号。

2、观察随机过失经解交织后的过失分布,观察突发过失经解交织后的过失分布。

3、观察交织对卷积编码突发过失信号纠错的性能改善。

三、根本原理

当移动通信信道出现深衰落时,数字信号的传输可能出现成串的突发过失。

一般的过失编码〔如卷积码〕只能纠正有限个错误,对于大量的突发误码无能为力。

通信系统采用交织编码和卷积码结合的方式来纠正突发过失。

交织的目的是把一个较长的突发过失离散成随机过失,使得纠错编码技术更容易纠正。

常用的交织技术主要有两类:

块交织和卷积交织。

块交织通常在数据分块分帧的情况下使用,卷积交织对连续的数据流来说比拟使用。

在码分多址系统中,基于数据分帧的情况采用了块交织的形式,所以这里我们仅介绍块交织的有关内容。

描述交织器性能的几个参数如下:

1突发长度:

突发错误的长度,用B表示。

2最小间隔:

突发连续错误分布的最小距离,用S表示。

3交织时延:

由于交织和解交织引起的编码时延,用D表示。

4存储要求:

交织或解交织过程需要的存储单元的大小,用M表示

交织器的性能通常用S/D以及S/M来描述,最小间隔S越大越好,交织时延D和存储要求M越小越好

交织器的实现框图如图18-1所示

图18-1分组〔块〕交织器实现框图

由图18-1可见,交织、解交织由如下几步构成:

⑴假设发送数据〔块〕

经信道编码后为:

;

⑵发送端交织存储器为一个行列交织矩阵存储器

,它按列写入,按行读出,即

⑶交织器输出后并送入突发信道的信号为

⑷假设在突发信道中受到两个突发干扰:

第一个突发干扰影响5位,即产生于

至

;第二个突发干扰影响4位,即产生于

至

。

那么突发信道的输出端信号

可以表示为

⑸在接收端,将受突发干扰的信号送入解交织器,解交织器也是一个行列交织矩阵的存储器

,它是按行写入,按列读出〔正好与交织矩阵规律相反〕,即

⑹经解交织存储器解交织以后的输出信号

,那么

为

可见,由上述分析,经过交织矩阵和解交织矩阵变换后,原来信道中的突发性连错,即两个突发一个连错5位、另一个连错4位却变成了

输出中的随机独立过失。

从交织器实现原理来看,一个实际上的突发信道,经过发送端交织器和接收端解交织器的信息处理后,就完全等效成一个随机独立过失信道,正如图中虚线方框所示。

所以从原理上看,信道交织编码实际上就是一类信道改造技术,它将一个突发信道改造成一个随机独立过失信道。

它本身并不具备信道编码检、纠错功能,仅起到信号预处理的作用。

我们可以将上述一个简单的5×5矩阵存储交织器的例子推广到一般情况。

假设分组〔块〕长度为:

,即由

列

行的矩阵构成。

其中交织矩阵存储器是按列写入、行读出,而解交织矩阵存储器是按相反的顺序按行写入、列读出,正是利用这种行、列顺序的倒换,可以将实际的突发信道变换成等效的随机独立过失信道。

矩阵中行的数目称为交织深度。

交织深度越大,符号的离散性就越大,抗突发过失的能力也越强。

但是,交织深度越大,交织编码的处理时间即交织时延也越长,所以说,交织编码的抗突发能力是以时间为代价的。

两个突发错误之间的最小间隔满足下式:

交织器的最小间隔可以通过改变读出行的顺序来改变,但交织时延和存储要求不随读出的顺序改变而改变,但交织时延和存储要求不随读出的顺序的改变而改变。

因为交织和解交织均有时延,所以交织器的交织时延为:

D=2IJ/Rc,其中Rc为符号速率。

交织器的存储要求为:

M=2IJ。

交织编码的主要缺点是:

在交织和解交织过程中,会产生2IJ个符号的附加处理时延,这对实时业务,特别是语音业务将带来很不利的影响。

所以对于语音等实时业务应用交织编码时,交织器的容量即尺寸不能取得太大。

交织器的改良主要是处理附加时延大及由于采用某种固定形式的交织方式就有可能产生很特殊的相反效果,即存在能将一些独立随机过失交织为突发过失的可能性。

为了克制以上两个主要缺点,人们研究了不少有效措施,如采用卷积交织器和伪随机交织器等。

四、实验原理

1、实验模块简介

本实验需用到基带成形模块、信道编码及交织模块〔以下简称编码模块〕及信道译码及解交织模块〔以下简称译码模块〕。

〔1〕基带成形模块:

本模块主要功能:

产生PN31伪随机序列作为信源;将基带信号进展串并转换;按调制要求进展基带成形,形成两路正交基带信号。

本实验只用该模块输出的位同步信号作为编码模块的基带信号驱动源。

〔2〕信道编码及交织模块:

本模块主要功能:

产生PN31伪随机序列作为信源,并进展〔2,1,4〕卷积编码,然后可选择有无块交织,再加上帧同步信号组成成帧数据后输出,输出的码可以选择有无过失、随机过失或突发过失。

〔3〕信道译码及解交织模块:

本模块主要功能:

完成帧同步捕获,同步后取出信息元进展〔2,1,4〕维特比卷积译码及解交织。

2、实验框图及电路说明

3、编码输出帧格式

A:

帧同步头,为11位巴克码:

。

B:

经卷积编码、打孔、交织后的信息数据,共484位。

C:

帧数据补足位,共1位,固定为0。

4、卷积编码生成多项式

本实验采用〔2,1,4〕卷积编码,生成多项式为:

G0=x3+x2+1

G1=x3+x2+x+1

5、实验原理

卷积编码、译码及帧映射局部同实验十七。

块交织原理如下:

打孔后的484位信息数据组成一个22位×22位的数据块,从上至下、从左至右按列放置,取出时从左至右、从上至下按行取出,完成交织。

如下列图所示:

五、实验步骤

1、在实验箱上正确安装基带成形模块〔以下简称基带模块〕、信道编码及交织模块〔以下简称编码模块〕及信道译码及交织模块〔以下简称译码模块〕。

2、关闭实验箱电源,用台阶插座线完成如下连接:

源端口

目的端口

连线说明

基带模块:

BS

编码模块:

BSIN

提供时钟信号

编码模块:

NRZD

编码模块:

PN31

提供PN31信号

编码模块:

BSOUT

译码模块:

BSIN

提供时钟信号

编码模块:

编码OUT

译码模块:

编码IN

将已编码信号进展译码

编码模块:

原码OUT

译码模块:

原码IN

方便译码端信号的比照

*检查连线是否正确,检查无误后翻开电源。

3、用示波器探头分别接编码模块上“BSIN〞和“PN31〞端信号,观察“PN31〞端信号应为8K伪随机码。

4、编码模块上拨位开关“过失〞位拨向上,其它位向下。

5、示波器探头分别接译码模块上“译码OUT〞及“原码OUT〞测试点,比拟译码结果。

6、在上面拨码开关状态下,再将编码模块和译码模块上拨位开关“交织〞位拨向上,观察译码结果是否正确。

7、在上面拨码开关状态下,再将编码模块上拨位开关“错型〞位拨向上,观察在突发过失情况下的译码结果是否正确,可以看出,在交织的作用下,突发过失全部纠正。

8、在比拟译码结果是否正确时,可借助译码模块上的“ERROR〞测试点的信号确定错码位的位置。

该测试点的信号指示相对于输入的原码而言哪个位发生了错误,假设该点无信号表示没有发现错码。