交通灯的设计.docx

《交通灯的设计.docx》由会员分享,可在线阅读,更多相关《交通灯的设计.docx(20页珍藏版)》请在冰豆网上搜索。

交通灯的设计

交通灯的设计

一、设计要求

设计一个主干道和支干道十字路口的交通控制电路,要求如下:

(1)一般情况下,保持主干道畅通,主干道绿灯亮、支干道红灯亮,并且主干道绿灯亮的时间不得少于60秒。

(2)主干道无车,支干道有车,则主干道红灯亮、支干道绿灯亮,但支干道绿灯亮的时间不超过30秒。

(3)每次主干道或支干道绿灯变红灯时,黄灯先亮5秒。

二、所用设备

(1)PC机一台

(2)TR1开发系统1套,FPGA下载版1套

(3)QuartusII,Modelsim开发软件1套

三、设计思路

用VerilogHDL设计一个十字路口交通灯控制器,其示意图如下所示:

A方向和B方向各设红(R)、黄(Y)、绿(G)三盏灯,三种灯按照合理的顺序亮灭,并能将灯亮的时间已倒计时的形式显示出来。

(1)功能要求:

由设计要求可以知道,这个主干道和支干道的十字路口的交通等系统,支干道两边安装传感器,要求优先保证主干道通畅。

平时处于主干道绿灯、支干道红灯的状态。

当支干道有车时,则传感器发出信号SIGNAL=1,主干道绿灯先变成黄灯,再变成红灯。

支干道有红灯变成绿灯。

如果支干道继续有车通过时,则传感器继续有信号,使支干道保持绿灯亮,但支干道保持绿灯亮的时间不超过30秒,否则支干道绿灯先转化成黄灯再变成红灯,同时主干道红灯变成绿灯。

主干道每次通行时间不得少于60秒;在此期间,即使支干道有信号SIGNAL输出时,也不能中止主干道的绿灯亮。

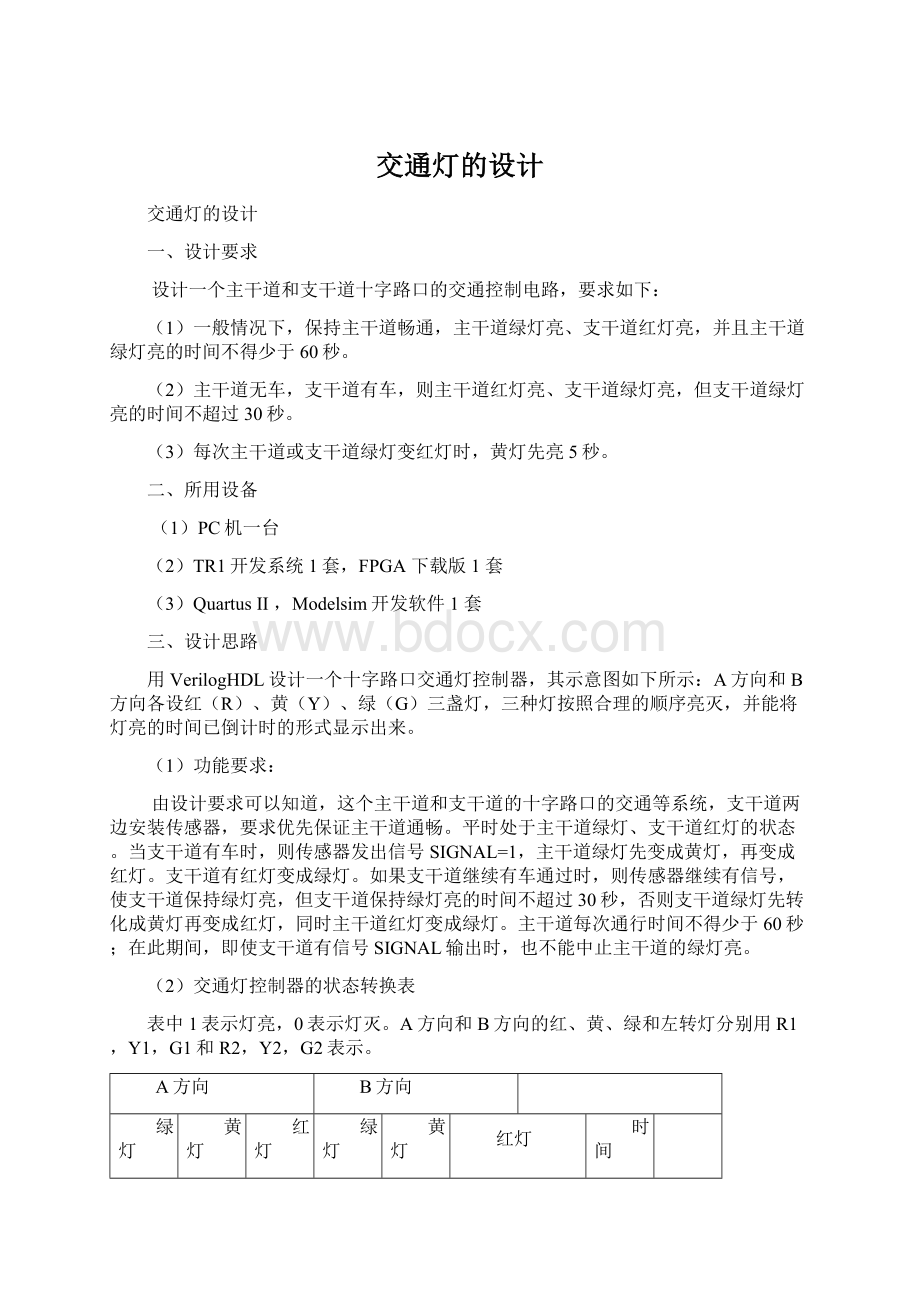

(2)交通灯控制器的状态转换表

表中1表示灯亮,0表示灯灭。

A方向和B方向的红、黄、绿和左转灯分别用R1,Y1,G1和R2,Y2,G2表示。

A方向

B方向

绿灯

(G1)

黄灯

(Y1)

红灯

(R1)

绿灯

(G2)

黄灯

(Y2)

红灯

(R2)

时间

1

0

0

0

0

1

不少于60秒

0

1

0

0

0

1

5秒

0

0

1

1

0

0

不大于30秒

0

0

1

0

1

0

5秒

表1状态表

交通灯系统工作主要有三个时间间隔,tl,ts,ty。

tl:

主干道绿灯亮时的最短时间间隔,不少于60秒。

ts:

主干道红灯亮时的最大时间间隔,不多于30秒。

ty:

主干道黄灯亮时的时间间隔,5秒。

(3)系统构架

从状态转换表中可以看出,该系统有控制器和处理器组成。

控制器接受外部系统时钟信号CLK、传感器信号SIGNAL、使能信号EN。

处理器有时钟产生器和译码显示器组成。

时钟产生器能够向控制器输入1HZ的时钟脉冲信号,而译码显示器则在控制器的控制下,改变交通灯信号。

(4)交通灯的状态转换图

图2支干道状态转换图

S0红灯

S3黄灯

S2绿灯

S1红灯

由上面的两个干道的状态转换图可知,两个方向的先设计成并列的,即都是按照倒计时信号进行状态跳转,然后再加入两者之间的限制关系和SIGNAL信号。

交通灯的控制过程可以分为四个阶段,对应的输出有四种状态,分别为S0,S1,S2,S3。

S0状态:

主干道绿灯亮,支干道红灯亮,此时支干道有车等待通过,而且主干道绿灯已亮,满足规定的时间间隔tl,控制器发出状态转换信号counta,countb。

输出从状态S0转换到S1状态。

S1状态:

主干道黄灯亮,支干道红灯亮,进入此状态,黄灯亮满足规定的时间间隔ty时,控制器发出状态转换信号counta,countb,输出从状态S1转换到S2状态。

S2状态:

主干道红灯亮,支干道绿灯亮,进入此状态,若此时支干道继续有车,则继续保持此状态,但支干道绿灯亮的时间不超过ts时间间隔,否则控制器发出状态转换信号counta,countb,输出从状态S2转换到S3状态。

S3状态:

主干道红灯亮,支干道黄灯亮,进入此状态,黄灯亮满足规定的时间间隔ty时,控制器发出状态转换信号counta,countb,输出从状态S3转换到S0状态。

对上述的S0,S1,S2,S3四种状态按照格雷码进行编码分别为00,01,11,10。

对于上述的S0和S2状态要加以说明:

首先,当主干道方向60秒计时结束时,若支干道方向无车(即SIGNAL=0)时,这时,控制器应继续运行在S0状态,再运行60秒,等到下一次计时结束时再行判断;当主干道60秒计时结束,若支干道方向有车,则按照状态转换图进行跳转。

同理,支干道也执行相同的处理。

其次,当支干道开始绿灯亮时,规定必须保持支干道方向一直有车(即SIGNAL=1)时,支干道方向的绿灯才能继续维持,否则,一旦在计数未结束但时SIGNAL=0时,执行从S2状态跳转到S3状态;若SIGNAL=1一直维持到30秒计数结束,那么也要执行状态转换。

(5)思路说明

根据交通灯控制器要实现的功能,考虑用两个并行执行的always模块(两个进程)来分别控制A(主干道)和B(支干道)两个方向的三盏灯。

这两个always模块控制一个方向的三种灯按照绿灯,黄灯,红灯点亮,并且循环往复。

每种灯亮的时间采用一个减法计数器进行计数,计数器用同步预置法设计,这样只需改变预置数据,就能改变计数器的模,因此,每个方向只要一个计数器即可。

为便于显示灯亮的时间,计数器输出均采用BCD码,显示由4个数码管来实现完成,A方向和B方向各用两个数码管。

四、详细设计

(1)1HZ时钟脉冲产生模块

1、原理说明:

采用计数方式,因为我们所用的实验开发板所提供我们的时钟频率有50Mhz和27MHz两种,实验中任选一个频率。

根据所选择的频率设计分频器。

输出为1Hz时钟频率。

2、代码

moduleclk_gen(iCLK,iRST_n,clk);

inputiCLK;//输入的50M晶振信号

inputiRST_n;//复位信号,低电平有效

outputclk;//输出1HZ的时钟信号

reg[31:

0]Cont_DIV;//ScanClockDIVCounter

regclk;

parameteriCLK_Freq=;//50MHz

//parameteriCLK_Freq=;//27MHz

//ScanClockGenerator

always@(posedgeiCLKornegedgeiRST_n)

begin

if(!

iRST_n)

Cont_DIV<=0;

else

begin

if(Cont_DIV<(iCLK_Freq>>1))

Cont_DIV<=Cont_DIV+1;

else

begin

Cont_DIV<=0;

clk<=~clk;

end

end

end

endmodule

3、说明

由于代码编写时频率过高,以致QuartusII软件无法进行仿真,只能的到编译通过的结果。

4、经过编译后得到的符号

(2)7段LED数码管显示译码模块

1、原理说明

在七段数码管显示部分,应该注意,在我们所用的实验开发板上我们的七段数码管的七段码的分布和顺序与平时所接触的不同。

图3所示为实验板上7_SEG结构,这一结构在我们进行七段译码的时候必须注意:

The4-digit7-SEGdisplaysaresharingthesamedatabus(oSEG7[7:

0]).Eachdigithasitsownenablepin(oCOM[3:

0]).Youcandisplayadesirednumberonanyoneofthedigitsbysendingthedisplaydatatotheshareddatabusandenablethedigit’scorrespondingoCOMpin(bydrivinglow).ThesegmentsilluminateiftheCyclonepintowhichtheyareconnecteddriveslow;theyappearunlitwhentheconnectedCyclonedevicepindriveshigh.

图3FPGA上的LED数码管

若在FPGA中实现4位数字的显示,采用动态扫描方式来实现,该数码管是共阳极的。

4位数字7段显示共用相同的数据总线oSEG7[7:

0],每一个数码管都有自己的使能引脚,即oCOM[3:

0]。

你可以让向oCOM[3:

0]中的对应位送低电平使数码管工作,实验用的FPGA开发板数码管的引脚时低电平驱动的。

而每一个数码管的的显示数字具体显示和上图的oSEG的具体位置有关,具体是:

4'h1:

oSEG<=8'b;//显示1

4'h2:

oSEG<=8'b;//显示2

4'h3:

oSEG<=8'b;//显示3

4'h4:

oSEG<=8'b;//显示4

4'h5:

oSEG<=8'b;//显示5

4'h6:

oSEG<=8'b;//显示6

4'h7:

oSEG<=8'b;//显示7

4'h8:

oSEG<=8'b;//显示8

4'h9:

oSEG<=8'b;//显示9

4'ha:

oSEG<=8'b;//显示a

4'hb:

oSEG<=8'b;//显示b

4'hc:

oSEG<=8'b;//显示c

4'hd:

oSEG<=8'b;//显示d

4'he:

oSEG<=8'b;//显示e

4'hf:

oSEG<=8'b;//显示f

4'h0:

oSEG<=8'b;//显示0

(2)SEG7_Driver.v代码

moduleSEG7_Driver(oSEG,oCOM,iDIG,iCLK,iRST_n);

input[15:

0]iDIG;//4DigitalHex

inputiCLK,iRST_n;

outputreg[7:

0]oSEG;//7-SEGLED段码输出

outputreg[3:

0]oCOM;//7-SEGCOM位码输出

reg[31:

0]Cont_DIV;//ScanClockDIVCounter时钟扫描计数器

reg[3:

0]mDEC_in;//HexTo7-SEGDecreg四位BCD码寄存器

reg[1:

0]mSCAN;//ScanOrderCounter

regmSCAN_CLK;//ScanClock译码器扫描时钟

parameteriCLK_Freq=;//50MHz

//parameteriCLK_Freq=;//27MHz

//ScanClockGenerator

always@(posedgeiCLKornegedgeiRST_n)

begin

if(!

iRST_n)

begin

Cont_DIV<=0;

mSCAN_CLK<=0;

end

else

begin

if(Cont_DIV<(iCLK_Freq>>10))

Cont_DIV<=Cont_DIV+1;//当计数未记50M/2^10时加1

else

begin

Cont_DIV<=0;//当计数未记50M/2^10时清零

mSCAN_CLK<=~mSCAN_CLK;//时钟反向,时钟的频率为512HZ

end

end

end

//ScanOrderGenerator

always@(posedgemSCAN_CLKornegedgeiRST_n)

begin

if(!

iRST_n)

begin

oCOM<=0;//复位信号到时,位码和扫描时钟都清零

mSCAN<=0;

end

else

begin

mSCAN<=mSCAN+1'b1;//mSCAN为2位,4个状态

case(mSCAN)

0:

oCOM<=4'b1110;//形成位码

1:

oCOM<=4'b1101;

2:

oCOM<=4'b1011;

3:

oCOM<=4'b0111;

endcase

end

end

//HexTo7-SEGDecoder

always@(posedgeiCLKornegedgeiRST_n)

begin

if(!

iRST_n)

begin

oSEG<=0;//复位信号到时,位码和扫描时钟都清零

mDEC_in<=0;//4位BCD码清零

end

else

begin

case(mSCAN)

0:

mDEC_in<=iDIG[3:

0];//对应最右边的数码管,故将iDIG的低四位传给mDEC_in,同理依次四位一组传给mDEC_in

1:

mDEC_in<=iDIG[7:

4];

2:

mDEC_in<=iDIG[11:

8];

3:

mDEC_in<=iDIG[15:

12];

endcase

case(mDEC_in)

4'h1:

oSEG<=8'b;//显示1

4'h2:

oSEG<=8'b;//显示2

4'h3:

oSEG<=8'b;//显示3

4'h4:

oSEG<=8'b;//显示4

4'h5:

oSEG<=8'b;//显示5

4'h6:

oSEG<=8'b;//显示6

4'h7:

oSEG<=8'b;//显示7

4'h8:

oSEG<=8'b;//显示8

4'h9:

oSEG<=8'b;//显示9

4'ha:

oSEG<=8'b;//显示a

4'hb:

oSEG<=8'b;//显示b

4'hc:

oSEG<=8'b;//显示c

4'hd:

oSEG<=8'b;//显示d

4'he:

oSEG<=8'b;//显示e

4'hf:

oSEG<=8'b;//显示f

4'h0:

oSEG<=8'b;//显示0

endcase

end

end

endmodule

(3)仿真波形

仿真前:

图4.1SEG7仿真前

仿真后:

图4.2SEG7仿真后1

图4.3SEG7仿真后2

图4.4SEG7仿真后3

图4.5SEG7仿真后4

从上面的几副图可以看到,依次动态扫描各个数码管oCOM的值依次时4’b0111,4’b1011,4’b1101,4’b1110,循环往复,实现数码管的动态扫描。

注意,人的眼睛适合观察频率在350-400HZ,此时人眼的有视觉暂留现象,可以让人觉得4个数码管在一直显示。

所以数码管的扫描频率也应在这个频率附近。

(4)利用Verilog产生的符号

(3)交通灯控制器模块

1、原理说明

利用有限状态机FSM定义主干道和支干道的灯的状态,采取两个独立的always模块并行执行,然后在两个模块中加入SIGNAL限制条件,同时输出两个3位的二进制数用于向实验板的LED形象表示两个方向的灯,共使用6个;输出两个8位的时间BCD码,接到SEG7_Driver模块的iDIG[15..0],用于显示时间。

2、traffic.v代码

/*信号定义与声明:

CLK:

同步时钟;

EN:

使能信号,为1上话,则控制器开始工作;

LAMPA:

控制A方向三盏灯的亮灭;(主方向)

LAMPB:

控制A方向三盏灯的亮灭;

ACOUNT:

用于A方向灯的时间显示,8位,可驱动两个数码管

BCOUNT:

用于B方向灯的时间显示,8位,可驱动两个数码管

SIGNAL:

用于提供AB方向的车辆信息,位;*/

moduletraffic(CLK,EN,SIGNAL,LAMPA,LAMPB,ACOUNT,BCOUNT);

output[7:

0]ACOUNT;

output[7:

0]BCOUNT;

output[2:

0]LAMPA;

output[2:

0]LAMPB;

inputCLK;

inputEN;

inputSIGNAL;//SIGNAL=1;B方向有车;SIGNAL=0B方向有车;

reg[2:

0]LAMPA,LAMPB;

reg[7:

0]numa,numb;//AB通道的时间寄存器

regtempa;//A通道时间倒计时为0置0

regtempb;//B通道时间倒计时为0置0

reg[1:

0]counta,countb;//AB方向的状态模式,2位

reg[7:

0]tl;//A方向绿灯亮时的最短时间间隔

reg[7:

0]ts;//A方向

reg[7:

0]ty;//A方向红灯的最大时间间隔

always@(EN)

if(!

EN)

begin

tl<=8'h60;

ts<=8'h30;

ty<=8'h5;

end

assignACOUNT=numa;

assignBCOUNT=numb;

always@(posedgeCLK)

begin

if(EN)

begin

if(!

tempa&&(counta==1)&&!

SIGNAL)//如果AB通道计时结束60秒并且处在0状态,若B方向此时没有车,此时继续维持0状态

begincounta<=0;end

if((counta==3)&&!

SIGNAL&&tempa)//若AB通道在状态2,且B方向绿灯状态未记完30秒,没有车,则跳转到状态3

begintempa=0;end

if(!

tempa)

begintempa<=1;

case(counta)//状态机

0:

//S0状态A方向为绿灯beginnuma<=tl;LAMPA<=3'd1;counta<=1;

end

1:

//S1状态A方向为黄灯beginnuma<=ty;LAMPA<=2;counta<=2;

end

2:

//S2状态A方向为红灯

beginnuma<=ts;

LAMPA<=4;counta<=3;

end

3:

//S3状态A方向为红灯beginnuma<=ty;

LAMPA<=4;counta<=0;

end

default:

LAMPA<=4;

endcase

end//if(!

tempa)

elsebegin//A方向的时间倒计时器

if(numa>1)

if(numa[3:

0]==0)

beginnuma[3:

0]<=4'b1001;

numa[7:

4]<=numa[7:

4]-1;

end

elsenuma[3:

0]<=numa[3:

0]-1;

if(numa==2)

tempa<=0;

end

end

else//(if!

EN)

beginLAMPA<=3'b100;

counta<=0;

tempa<=0;

end

end//always

always@(posedgeCLK)

begin

if(EN)

begin

if(!

tempb&&(countb==1)&&!

SIGNAL)//如果AB通道计时结束60秒并且处在0状态,若B方向此时没有车,此时继续维持0状态

begincountb<=0;end

if((countb==3)&&!

SIGNAL&&tempb)//若AB通道在状态2,且B方向绿灯状态未记完30秒,没有车,则跳转到状态3

begintempb=0;end

if(!

tempb)

begintempb<=1;

case(countb)//状态机

2'b00:

//S0状态B方向为红灯beginnumb<=tl;LAMPB<=3'b100;

countb<=2'b01;

end

2'b01:

//S1状态B方向为红灯beginnumb<=ty;

LAMPB<=3'b100;countb<=2'b10;

end

2'b10:

//S2状态B方向为绿灯

beginnumb<=ts;LAMPB<=3'b001;

countb<=2'b11;

end

2'b11:

//S3状态B方向为黄灯

beginnumb<=ty;LAMPB<=3'b010;

countb<=2'b00;

end

default:

LAMPB<=3'b100;

endcase

end//if(!

tempb)

elsebegin//A方向的时间倒计时器

if(numb>1)

if(numb[3:

0]==4'b0000)

beginnumb[3:

0]<=4'b1001;

numb[7:

4]<=numb[7:

4]-1;

end

elsenumb[3:

0]<=numb[3:

0]-1;

if(numb==2)tempb<=0;

end//else

end//if(EN)

else

beginLAMPB<=3'b100;

countb<=2'b00;

tempb<=0;

使能信号产生,从新计时

end

end//always

endmodule

3、仿真波形

图5.1traffic.v仿真波形1

图5.2traffic.v仿真波形2

图5.3traffic.v仿真波形3

主干道绿灯60秒计时结束,此时支干道SINGANAL=1,故跳到黄灯