单片机课程方案设计书数字频率计.docx

《单片机课程方案设计书数字频率计.docx》由会员分享,可在线阅读,更多相关《单片机课程方案设计书数字频率计.docx(19页珍藏版)》请在冰豆网上搜索。

单片机课程方案设计书数字频率计

根据单片机课程所学内容,结合其他相关课程知识,设计一个数字频率计,以加深对单片机知识的理解,本设计以MCS-51系列单片机为核心,采用常用电子器件设计。

利用单片机的定时器和计数器实现对方波信号的频率测量,闸门时间可选0.1秒、1秒、10秒,采用六位LED显示测量的频率。

二、总体设计思想

1、基本原理

基本设计原理是直接用十进制数字显示被测信号频率的一种测量装置。

它以测量周期的方法对正弦波、方波、三角波的频率进行自动的测量。

所谓“频率”,就是周期性信号在单位时间(1s)内变化的次数。

若在一定时间间隔T内测得这个周期性信号的重复变化次数N,则其频率可表示为f=N/T。

其中脉冲形成电路的作用是将被测信号变成脉冲信号,其重复频率等于被测频率fx。

时间基准信号发生器提供标准的时间脉冲信号,若其周期为1s,则门控电路的输出信号持续时间亦准确地等于1s。

闸门电路由标准秒信号进行控制,当秒信号来到时,闸门开通,被测脉冲信号通过闸门送到计数译码显示电路。

秒信号结束时闸门关闭,计数器停止计数。

由于计数器计得的脉冲数N是在1秒时间内的累计数,所以被测频率fx=NHz。

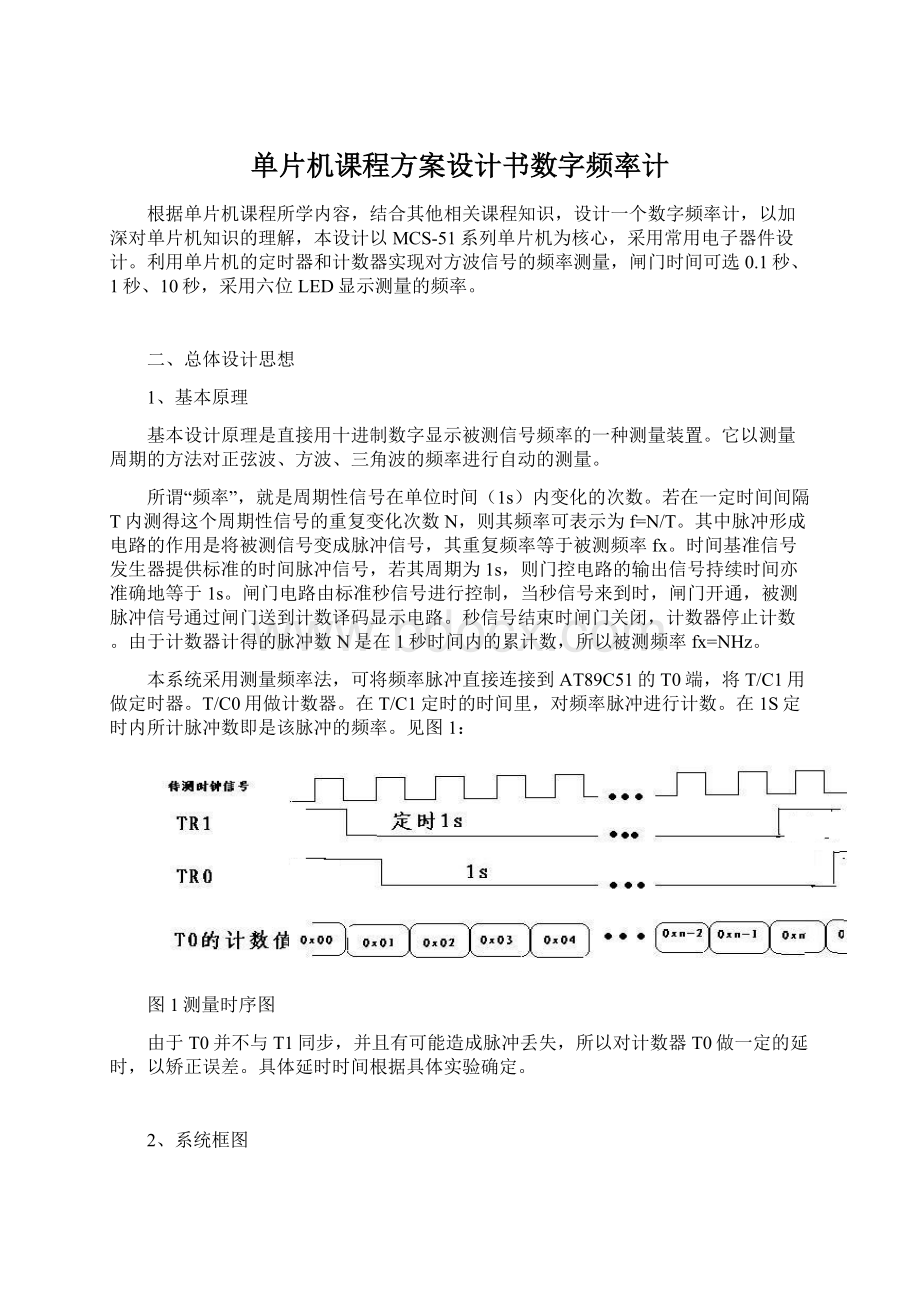

本系统采用测量频率法,可将频率脉冲直接连接到AT89C51的T0端,将T/C1用做定时器。

T/C0用做计数器。

在T/C1定时的时间里,对频率脉冲进行计数。

在1S定时内所计脉冲数即是该脉冲的频率。

见图1:

图1测量时序图

由于T0并不与T1同步,并且有可能造成脉冲丢失,所以对计数器T0做一定的延时,以矫正误差。

具体延时时间根据具体实验确定。

2、系统框图

本频率计的数据采集系统主要元器件是单片机AT89C51,由它完成对待测信号频率的计数和结果显示等功能,外部还要有分频器、显示器等器件。

可分为以下几个模块:

放大整形模块、秒脉冲产生模块、换档模拟转换模块、单片机系统、LCD显示模块。

图2系统框图

三、具体设计

1.总体设计电路

图3频率计原理图

2.模块设计

(1)、硬件系统构成:

本频率计的数据采集系统主要元器件是单片机AT89C51,由它完成对待测信号频率的计数和结果显示等功能,外部还要有分频器、显示器等器件。

可分为以下几个模块:

放大整形模块、秒脉冲产生模块、换档模拟转换模块、单片机系统、LCD显示模块。

系统框图如下图2:

图2系统框图

(2)、AT89C51单片机及其引脚说明:

89C51是一种高性能低功耗的采用CMOS工艺制造的8位微控制器,它提供下列标准特征:

4K字节的程序存储器,128字节的RAM,32条I/O线,2个16位定时器/计数器,一个5中断源两个优先级的中断结构,一个双工的串行口,片上震荡器和时钟电路。

引脚说明:

·VCC:

电源电压

·GND:

地

·P0口:

P0口是一组8位漏极开路型双向I/O口,作为输出口用时,每个引脚能驱动8个TTL逻辑门电路。

当对0端口写入1时,可以作为高阻抗输入端使用。

当P0口访问外部程序存储器或数据存储器时,它还可设定成地址数据总线复用的形式。

在这种模式下,P0口具有内部上拉电阻。

在EPROM编程时,P0口接收指令字节,同时输出指令字节在程序校验时。

程序校验时需要外接上拉电阻。

·P1口:

P1口是一带有内部上拉电阻的8位双向I/O口。

P1口的输出缓冲能接受或输出4个TTL逻辑门电路。

当对P1口写1时,它们被内部的上拉电阻拉升为高电平,此时可以作为输入端使用。

当作为输入端使用时,P1口因为内部存在上拉电阻,所以当外部被拉低时会输出一个低电流(IIL)。

·P2口:

P2是一带有内部上拉电阻的8位双向的I/O端口。

P2口的输出缓冲能驱动4个TTL逻辑门电路。

当向P2口写1时,通过内部上拉电阻把端口拉到高电平,此时可以用作输入口。

作为输入口,因为内部存在上拉电阻,某个引脚被外部信号拉低时会输出电流(IIL)。

P2口在访问外部程序存储器或16位地址的外部数据存储器(例如MOVX@DPTR)时,P2口送出高8位地址数据。

在这种情况下,P2口使用强大的内部上拉电阻功能当输出1时。

当利用8位地址线访问外部数据存储器时(例MOVX@R1),P2口输出特殊功能寄存器的内容。

当EPROM编程或校验时,P2口同时接收高8位地址和一些控制信号。

·P3口:

P3是一带有内部上拉电阻的8位双向的I/O端口。

P3口的输出缓冲能驱动4个TTL逻辑门电路。

当向P3口写1时,通过内部上拉电阻把端口拉到高电平,此时可以用作输入口。

作为输入口,因为内部存在上拉电阻,某个引脚被外部信号拉低时会输出电流(IIL)。

P3口同时具有AT89C51的多种特殊功能,具体如下表1所示:

端口引脚

第二功能

P3.0

RXD(串行输入口)

P3.1

TXD(串行输出口)

P3.2

(外部中断0)

P3.3

(外部中断1)

P3.4

T0(定时器0)

P3.5

T1(定时器1)

P3.6

(外部数据存储器写选通)

P3.7

(外部数据存储器都选通)

表1P3口的第二功能

·RST:

复位输入。

当振荡器工作时,RST引脚出现两个机器周期的高电平将使单片机复位。

·ALE/

:

当访问外部存储器时,地址锁存允许是一输出脉冲,用以锁存地址的低8位字节。

当在Flash编程时还可以作为编程脉冲输出(

)。

一般情况下,ALE是以晶振频率的1/6输出,可以用作外部时钟或定时目的。

但也要注意,每当访问外部数据存储器时将跳过一个ALE脉冲。

·

:

程序存储允许时外部程序存储器的读选通信号。

当AT89C52执行外部程序存储器的指令时,每个机器周期

两次有效,除了当访问外部数据存储器时,

将跳过两个信号。

·

/VPP:

外部访问允许。

为了使单片机能够有效的传送外部数据存储器从0000H到FFFH单元的指令,

必须同GND相连接。

需要主要的是,如果加密位1被编程,复位时EA端会自动内部锁存。

当执行内部编程指令时,

应该接到VCC端。

·XTAL1:

振荡器反相放大器以及内部时钟电路的输入端。

·XTAL2:

振荡器反相放大器的输出端。

在本次设计中,采用89C51作为CPU处理器,充分利用其硬件资源,结合D触发器CD4013,分频器CD4060,模拟转换开关CD4051,计数器74LS90等数字处理芯片,主要控制两大硬件模块,量程切换以及显示模块。

下面还将详细说明。

(3)、信号调理及放大整形模块:

放大整形系统包括衰减器、跟随器、放大器、施密特触发器。

它将正弦输入信号Vx整形成同频率方波Vo,幅值过大的被测信号经过分压器分压送入后级放大器,以避免波形失真。

由运算放大器构成的射级跟随器起阻抗变换作用,使输入阻抗提高。

同相输入的运算放大器的放大倍数为(R1+R2)/R1,改变R1的大小可以改变放大倍数。

系统的整形电路由施密特触发器组成,整形后的方波送到闸门以便计数。

由于输入的信号幅度是不确定、可能很大也有可能很小,这样对于输入信号的测量就不方便了,过大可能会把器件烧毁,过小可能器件检测不到,所以在设计中采用了这个信号调理电路对输入的波形进行阻抗变换、放大限幅和整形,信号调理部分电路具体实现电路原理图和参数如下图4:

图4信号放大模块电路图

(4)、时基信号产生电路:

CD4013------双上升沿D触发器,引脚及功能见如下图5:

图5D触发器引脚及功能图

CD4013由两个相同的、相互独立的数据型触发器构成。

每个触发器有独立的数据置位复位时钟输入和Q及Q非输出。

此器件可用作移位寄存器,且通过将Q非输出连接到数据输入,可用作计数器和触发器。

在时钟上升沿触发时,加在D输入端的逻辑电平传送到Q输出端。

置位和复位或复位线上的高电平完成。

CD4060------14位二进制串行计数器,引脚及功能见如下图6:

CD4060由一震荡器和14极二进制串行计数器位组成,震荡器的结构可以是RC或晶振电路。

CR为高电平时,计数器清零且振荡器使用无效,所有的计数器位均为主从触发器CP1非(和CP0)的下降沿计数器以二进制进行计数,在时钟脉冲线上使用施密特触发器对时钟上升和下降时间无限制。

图6进制串行计数器引脚及功能图

时基信号的产生原理:

本电路采用32768HZ晶体震荡器,利用CD4060芯片经过14级分频得到2HZ的信号(32768/214),在经过CD4013双D触发器经过二分频得到0.5HZ的方波,即输出秒脉冲信号使单片机进行计数。

(5)、显示模块

1602基本技术:

1)、主要功能

A、40通道点阵LCD驱动。

B、可选择当作行驱动或列驱动。

C、输入/输出信号:

输出,能产生20×2个LCD驱动波形。

输入,接受控制器送出的串行数据和控制信号,偏压(V1∽V6)。

D、通过单片机控制将所测的频率信号读数显示出来。

2)、技术参数

2.1)极限参数表2:

名称

符号

标准值

单位

MIN

TYPE

MAX

电路电源

VDD-VSS

-0.3

7.0

V

LCD驱动电压

VDD-VEE

VDD-13.5

VDD+0.3

V

输入电压

VIN

-0.3

VDD+0.3

V

静电电压

-

-

100

V

工作温度

-20

+70

°C

储存温度

-30

+80

°C

表2极限参数表

2.2)电参数表3:

名称

符号

测试条件

标准值

单位

MIN

TYPE

MAX

输入高电平

VIH

-

2.2

VDD

V

输入低电平

VIL

-

-0.3

0.6

V

输出高电平

VOH

IOH=0.2mA

2.4

-

V

输出低电平

VOL

IOL=1.2mA

-

0.4

V

工作电流

IDD

VDD=5.0V

2.0

mA

液晶驱动电压

VDD-VEE

Ta=0°C

4.9

V

Ta=25°C

4.7

Ta=50°C

4.5

表3电参数表

3)、时序特性表4:

项目

符号

测试条件

标准值

单位

MIN

TYPE

MAX

允许时间周期

TCYCE

5.1a5.1b

1000

ns

允许脉冲宽度,高电平

PWEH

450

--

--

ns

允许上升和下降时间

tErtEf

--

--

25

ns

地址建立时间

tAS

140

--

--

ns

数据延迟时间

tDDR

--

--

320

ns

数据建立时间

tDSW

195

--

--

ns

数据保持时间

tH

10

--

--

ns

DATAHOLDTIME

tDHR

20

--

--

ns

地址保持时间

tAH

10

--

--

ns

表4时序特性表

4)、引脚和指令功能

4.1)模块引脚功能表5:

引线号

符号

名称

功能

1

Vss

接地

0V

2

VDD

电路电源

5V±10%

3

VEE

液晶驱动电压

保证VDD-VEE=4.5∽5V电压差

4

RS

寄存器选择信号

H:

数据寄存器L:

指令寄存器

5

R/W

读/写信号

H:

读L:

写

6

E

片选信号

下降沿触发,锁存数据

7

|

14

DB0

|

DB7

数据线

数据传输

表5模块引脚功能表

4.2)寄存器选择功能表6:

RS

R/W

操作

0

0

指令寄存器(IR)写入

0

1

忙标志和地址计数器读出

1

0

数据寄存器(DR)写入

1

1

数据寄存器读出

表6寄存器功能选择表

4.3)指令功能

格式:

RSR/WDB7DB6DB5DB4DB3DB2DB1DB0

共11种指令:

清除,返回,输入方式设置,显示开关,控制,移位,功能设置,CGRAM地址设

置,DDRAM地址设置,读忙标志,写数据到CG/DDRAM,读数据由CG/DDRAM。

5)、显示位与DDRAM地址的对应关系表7:

显示位序号

12345………………40

DDRAM

地址(HEX)

第一行

0001020304..……………..27

第二行

4041424344…………….....67

表7显示位与DDRAM地址关系表

(6)、软件设计

1)、主程序main流程图

图7主程序流程图

(2)、程序

/*简易数字频率计:

T1定时计器,T0计数器,由P34(/T0)口输入待测频率*/

/*T1定时1S,在这1S内T1的计数值就是待测的频率值。

*/

#include//头文件

#include//头文件

#defineucharunsignedchar//宏定义

#defineuintunsignedint//宏定义

sfr16DPTR=0x82。

//定义DPTR

bitstatus_F=1。

//状态标志位

uintaa,qian,bai,shi,ge,bb,wan,shiwan。

//定义变量

ucharcout。

unsignedlongtemp。

//定义长整型变量

/*数码管显示0-9*/

ucharcode

table[]={0x3f,0x06,0x5b,0x4f,0x66,0x6d,0x7d,0x07,0x7f,0x6f,0x77,0x7c,0x39,0x5e,0x79,0x71}。

/*子函数声明*/

voiddelay(uintz)。

voidinit()。

voiddisplay(uintshiwan,uintwan,uintqian,uintbai,uintshi,uintge)。

voidxtimer0()。

voidxtimer1()。

/*主函数*/

voidmain()

{

P0=0XFF。

//初始化P0口

init()。

//调用定时器,计数器初始化

while

(1)

{

if(aa==19)//定时20*50MS=1S

{

aa=0。

//定时完成一次后清0

status_F=1。

//完成计数

TR1=0。

//关闭T1定时槛,定时1S完成

delay(46)。

//延时较正误差

TR0=0。

//关闭T0

DPL=TL0。

//计数量的低8位

DPH=TH0。

//计数量的高8位

temp=DPTR+cout*65535。

//计数值放入变量

shiwan=temp%1000000/100000。

wan=temp%100000/10000。

qian=temp%10000/1000。

//显示千位

bai=temp%1000/100。

//显示百位

shi=temp%100/10。

//显示十位

ge=temp%10。

//显示个位

}

display(shiwan,wan,qian,bai,shi,ge)。

//调用显示函数

}

}

/*定时器,计数器初始化*/

voidinit()

{

temp=0。

//变量赋初值

aa=0。

cout=0。

IE=0X8A。

//开中断,T0,T1中断

TMOD=0x15。

//T1为定时器工作于方式1,T0为计数器工作于方式1

TH1=0x3c。

//定时器赋高8初值,12M晶振

TL1=0xb0。

//定时器赋低8初值,12M晶振

TH0=0。

//计数器赋高8初值初值

TL0=0。

//计数器赋低8初值

TR1=1。

//开定时器1

TR0=1。

//开计数器0

}

/*显示子函数*/

voiddisplay(uintshiwan,uintwan,uintqian,uintbai,uintshi,uintge)

{

P0=0xdf。

//P0口是位选11011111改成11111101==0XDF

P2=table[shiwan]。

//显示shiwan位

delay(5)。

P0=0xef。

//P0口是位选11101111改成11111110==0XFE

P2=table[wan]。

//显示wan位

delay(3)。

P0=0xf7。

//P0口是位选111101111改成01111111==0X7F

P2=table[qian]。

//显示千位

delay(3)。

P0=0xfb。

//P0口是位选11111011改成10111111==0XBF

P2=table[bai]。

//显示百位

delay(3)。

P0=0xfd。

//P0口是位选11111101改成11011111==0XDF

P2=table[shi]。

//显示十位

delay(3)。

P0=0xfe。

//P0口是位选11111110改成11101111==0XEF

P2=table[ge]。

//显示个位

delay(3)。

}

/*定时中断子函数*/

voidxtimer1()interrupt3

{

TH1=0x3c。

//定时器赋高8初值

TL1=0xb0。

//定时器赋低8初值

aa++。

}

/*计数器中断子函数*/

voidxtimer0()interrupt1

{

cout++。

}

/*延时子函数。

延时1MS*/

voiddelay(uintz)

{

uinti,j。

for(i=0。

ii++)

for(j=0。

j<110。

j++)。

//j上限为125

}

3.仿真结果与分析

此间易频率计的特点是由于加入了延时补偿,对于低频率脉冲能够准确计数,对于较高频率,则频率越高,误差越大。

但总体来讲,误差相对较小。

(1).在1~3257HZ,测量结果是准确的,如图8所示1HZ,1KHZ,3257HZ的仿真图:

图81HZ,1KHZ,3257HZ的仿真图

(2).在3258HZ~9.5KHZ的时候测量有误差并且慢慢减少。

在3258HZ时候达到最大误差0.03069%,如图9。

9.5KHZ时候达到最小误差0.01368%。

如图10:

图9测量3258HZ的仿真结果

图10测量95013HZ的仿真结果

(3).从9.6KHZ~999.7629KHZ,测量误差越来越大,在9.6KHZ为0.01458%,在999.7629KHZ

时为0.0237%

图11测量9.6KHZ、999.7629KHZ的仿真结果

四、结论

在单片机应用系统设计时,必须先确定该系统的技术要求,这是系统设计的依据和出发点,整个设计过程都必须围绕这个技术要求来工作。

在设计时遵循从整体到局部也即自上而下的原则。

把复杂的问题分解为若干个比较简单的、容易处理的问题,分别单个的加以解决。

将总任务分解成可以独立表达的子任务,这些子任务再向下分,直到每个子任务足够简单,能够直接而容易的实现为止。

在程序调试时应按各个功能模块分别调试。

在程序设计时,正确合理的设计是非常重要的,正确的程序设计包括程序的结构是否合理,一些循环结构和循环指令的使用是否恰当,能否使用较少的循环次数或较快的指令,是否能把某些延迟等待的操作改为中断申请服务,能否把某些计算方法和查表技术适当简化等。

另外程序的设计要具有可扩展性,程序的结构要标准化,便于阅读、修改和扩充。

通过本次课程设计,我更加地了解和掌握单片机的基本知识和基本的编写程序,也更加深入地了解单片机这么课程,掌握汇编语言的设计和调试方法。

对于认识到自己在知识方面存在的不足,明确今后的学习方向是非常有益的。

在设计过程中,得到了我的指导老师的悉心指导与帮助,在此一并表示衷心的感谢。

参考资料

[1]张毅坤,陈善久.单片微型计算机原理及应用.西安电子科技大学出版社,2002.

[2]张友德,赵志英,徐时亮.单片微机原理应用与实验.复旦大学出版社,2000.

[3]张毅刚,彭善元,董继承.单片机原理及应用.高等教育出版社,2003.