出租车计费器VHDL语言课件.docx

《出租车计费器VHDL语言课件.docx》由会员分享,可在线阅读,更多相关《出租车计费器VHDL语言课件.docx(12页珍藏版)》请在冰豆网上搜索。

出租车计费器VHDL语言课件

《数字逻辑电路》课程设计

——出租车计费器的设计

计算机学院软件工程1401

赵雷3140608027

出租车计费器的设计

1、系统设计任务及要求

(1)能实现计费功能,计费标准为:

按行驶里程收费,起步价为7.00元,并在车行3千米后再按2元/千米,当总费用达到或超过40元时,每千米收费4元,客户端需要停车等待时按时间收费,计费单价每20秒1元。

(2)设计动态扫描电路:

以十进制显示出租车行驶的里程与车费,在数码管上显示(前四个显示里程,后三个显示车费)。

(3)用VHDL语言设计符合上述功能要求的出租车计费器,并用层次化设计方法设计该电路。

(4)完成电路全部设计后,通过系统试验箱下载验证设计的正确性。

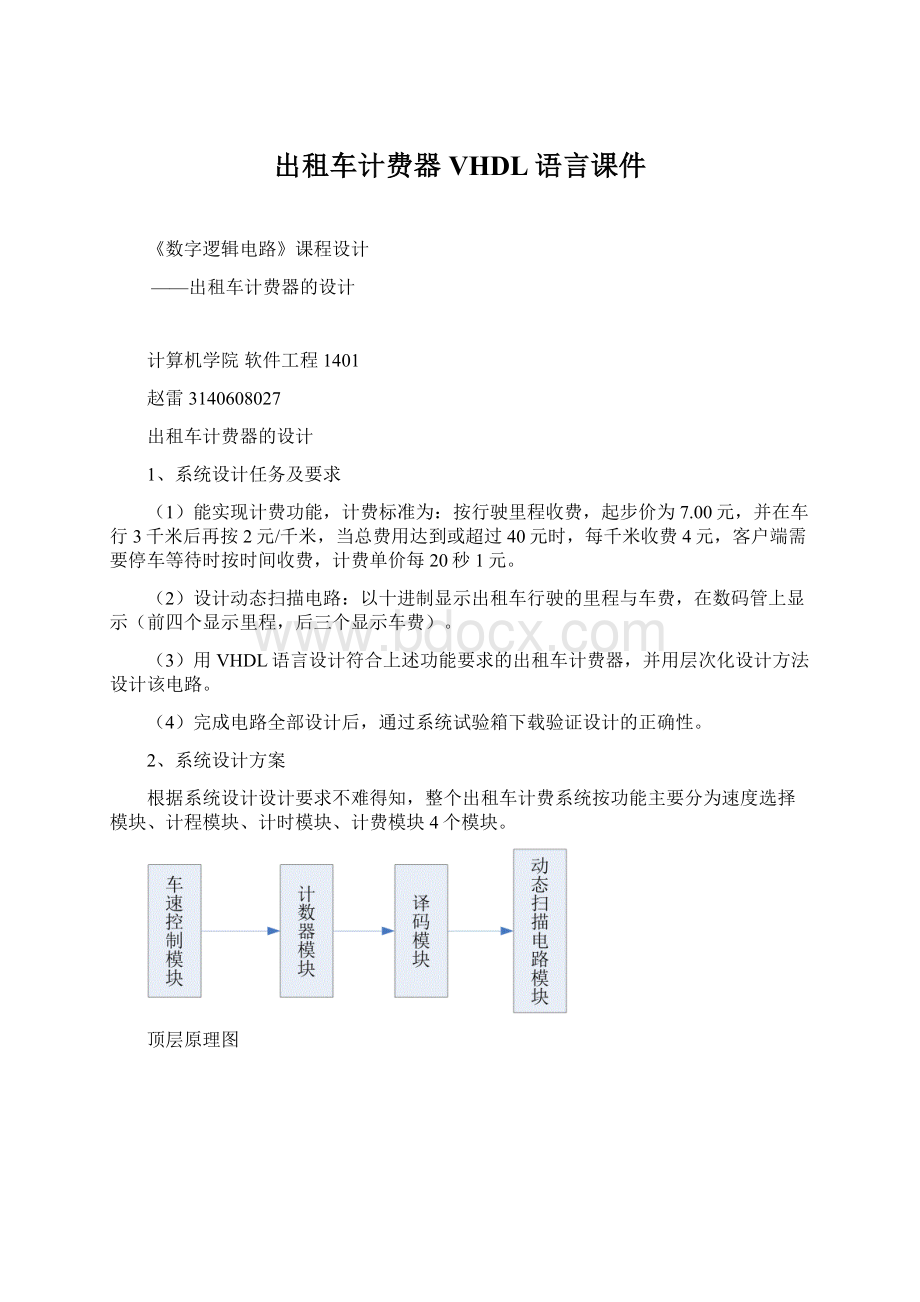

2、系统设计方案

根据系统设计设计要求不难得知,整个出租车计费系统按功能主要分为速度选择模块、计程模块、计时模块、计费模块4个模块。

顶层原理图

1.速度模块:

通过对速度信号sp的判断,决定行使的路程,这里是通过速度信号来模拟一个变量的取值。

如kinside变量,其含义是行进100m所需的时钟周期数,然后每行进100m,则产生一个脉冲clkout来驱动计费模块。

VHDL语言:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityTaxi_part1is

port(clk,reset,start,stop:

instd_logic;

sp:

instd_logic_vector(2downto0);

clkout:

outstd_logic);

endTaxi_part1;

architecturebehaviorofTaxi_part1is

begin

process(clk,reset,stop,start,sp)

typestate_typeis(s0,s1);

variables_state:

state_type;

variablecnt:

integerrange0to1400;

variablekinside:

integerrange0to1400;

begin

casespis

when"000"=>kinside:

=0;

when"001"=>kinside:

=1400;

when"010"=>kinside:

=1200;

when"011"=>kinside:

=1000;

when"100"=>kinside:

=800;

when"101"=>kinside:

=600;

when"110"=>kinside:

=400;

when"111"=>kinside:

=200;

endcase;

if(reset='1')thens_state:

=s0;

elsif(clk'eventandclk='1')then

cases_stateis

whens0=>

cnt:

=0;clkout<='0';

if(start='1')thens_state:

=s1;

elses_state:

=s0;

endif;

whens1=>

clkout<='0';

if(stop='1')thens_state:

=s0;--相当于无客户上车

elsif(sp="000")thens_state:

=s1;---有客户上车,但车速位0,即客户刚上车还未起步

elsif(cnt=kinside)thencnt:

=0;clkout<='1';s_state:

=s1;

elsecnt:

=cnt+1;s_state:

=s1;

endif;

endcase;

endif;

endprocess;

endbehavior;

2.计程模块:

由于一个clkout信号代表行进100m,故通过对clkout计数,可以获得共行进的距离kmcount。

VHDL语言:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityTaxi_part2is

port(clkout,reset:

instd_logic;

kmcnt1:

outstd_logic_vector(3downto0);

kmcnt2:

outstd_logic_vector(3downto0);

kmcnt3:

outstd_logic_vector(3downto0));

endTaxi_part2;

architecturebehaviorofTaxi_part2is

begin

process(clkout,reset)

variablekm_reg:

std_logic_vector(11downto0);

begin

if(reset='1')thenkm_reg:

="000000000000";

elsif(clkout'eventandclkout='1')then--km_reg(3downto0)对应里程十分位

if(km_reg(3downto0)="1001")then

km_reg:

=km_reg+"0111";--十分位向个位的进位处理

elsekm_reg(3downto0):

=km_reg(3downto0)+"0001";

endif;

if(km_reg(7downto4)="1010")then

km_reg:

=km_reg+"01100000";--个位向十位的进位处理

endif;

endif;

kmcnt1<=km_reg(3downto0);

kmcnt2<=km_reg(7downto4);

kmcnt3<=km_reg(11downto8);

endprocess;

endbehavior;

3.计时模块:

在汽车启动时,当遇到顾客等人时,出租车采用计时收费的方式。

通过对速度信号sp的判断决定是否开始记录时间。

当stop=1时,不计费,当stop=0,sp=0时,开始按时间计费,当时间达到足够长时则产生Timecount脉冲,并重新计时。

一个Timecount脉冲相当于等待的时间达到了时间计费的长度。

使用1kHz的系统时钟,计算20s计数值为20000。

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityTaxi_part3is

port(clk,reset,start,stop:

instd_logic;

sp:

instd_logic_vector(2downto0);

timecount:

outstd_logic);

endTaxi_part3;

architecturebehaviorofTaxi_part3is

begin

process(reset,clk,sp,stop,start)

typestate_typeis(t0,t1,t2);

variablet_state:

state_type;

variablewaittime:

integerrange0to1000;

begin

if(reset='1')thent_state:

=t0;

elsif(clk'eventandclk='1')then

caset_stateis

whent0=>

waittime:

=0;timecount<='0';

if(start='1')thent_state:

=t1;

elset_state:

=t0;

endif;

whent1=>

if(sp="000")thent_state:

=t2;

elsewaittime:

=0;t_state:

=t1;

endif;

whent2=>

waittime:

=waittime+1;

timecount<='0';

if(waittime=1000)then

timecount<='1';--20s,即1000个clk,产生一个时间计费脉冲

waittime:

=0;

elsif(stop='1')thent_state:

=t0;

elsif(sp="000")thent_state:

=t2;

elsetimecount<='0';t_state:

=t1;

endif;

endcase;

endif;

endprocess;

endbehavior;

4.计费模块:

计费模块由两个线程组成。

其中一个进程根据条件对Enable和Price赋值:

当记录的距离达到3千米后Enable变为1,开始进行每千米收费,当总费用大于40元后,则单价Price由原来的2元/千米变为4元/千米;第二个进程在每个时钟周期判断Timecount和Clkcount的值。

当其为1时,则在总费用上加上相应的费用。

VHDL语言:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityTaxi_part4is

port(clk,reset,timecount,clkout:

instd_logic;

kmcnt2:

instd_logic_vector(3downto0);

kmcnt3:

instd_logic_vector(3downto0);

count1:

outstd_logic_vector(3downto0);

count2:

outstd_logic_vector(3downto0);

count3:

outstd_logic_vector(3downto0));

endTaxi_part4;

architecturebehaviorofTaxi_part4is

signalcash:

std_logic_vector(11downto0);

signalPrice:

std_logic_vector(3downto0);

signalEnable:

std_logic;

begin

process(cash,kmcnt2)

begin

if(cash>="000001000000")thenprice<="0100";

elsePrice<="0010";

endif;

if((kmcnt2>="0011")or(kmcnt3>="0001"))thenEnable<='1';

elseEnable<='0';

endif;

endprocess;

kmmoney2:

process(reset,clkout,clk,Enable,Price,kmcnt2)

variablereg2:

std_logic_vector(11downto0);

variableclkout_cnt:

integerrange0to10;

begin

if(reset='1')thencash<="000000000111";--起步费用设为7元

elsif(clk'eventandclk='1')then

if(timecount='1')then--判断是否需要时间计费,每20s加一元

reg2:

=cash;

if(reg2(3downto0)+"0001">"1001")then

reg2(7downto0):

=reg2(7downto0)+"00000111";

if(reg2(7downto4)>"1001")then

cash<=reg2+"000001100000";

elsecash<=reg2;

endif;

elsecash<=reg2+"0001";

endif;

elsif(clkout='1'andEnable='1')then--里程计费

if(clkout_cnt=9)then

clkout_cnt:

=0;

reg2:

=cash;

if("0000"®2(3downto0)+price(3downto0)>"00001001")then

reg2(7downto0):

=reg2(7downto0)+"00000110"+price;

if(reg2(7downto4)>"1001")then

cash<=reg2+"000001100000";

elsecash<=reg2;

endif;

elsecash<=reg2+price;

endif;

elseclkout_cnt:

=clkout_cnt+1;

endif;

endif;

endif;

endprocess;

count1<=cash(3downto0);--总费用的个位

count2<=cash(7downto4);--总费用的十位

count3<=cash(11downto8);--总费用的百位

endbehavior;

5.显示模块:

时间的显示需要用到全部8个数码管,由于实验板上的所有数码管均对应同一组7段码,因此,需要采用动态扫描的方式实现时间显示。

VHDL语言:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entitydisplayis

port(clk:

instd_logic;

kmcount1:

instd_logic_vector(3downto0);

kmcount2:

instd_logic_vector(3downto0);

kmcount3:

instd_logic_vector(3downto0);

count1:

instd_logic_vector(3downto0);

count2:

instd_logic_vector(3downto0);

count3:

instd_logic_vector(3downto0);

clkout:

outstd_logic_vector(6downto0);

sel:

bufferstd_logic_vector(2downto0));

enddisplay;

architecturedtsmofdisplayis

signalkey:

std_logic_vector(3downto0);

begin

process(clk)

variabledount:

std_logic_vector(2downto0):

="000";

begin

ifrising_edge(clk)then

ifdount="111"then

dount:

="000";

else

dount:

=dount+1;

endif;

endif;

sel<=dount;

endprocess;

process(sel)

begin

caseselis

when"000"=>key<=kmcount3(3downto0);

when"001"=>key<=kmcount2(3downto0);

when"011"=>key<=kmcount1(3downto0);

when"010"=>key<="1011";

when"101"=>key<=count3(3downto0);

when"110"=>key<=count2(3downto0);

when"111"=>key<=count1(3downto0);

when"100"=>key<="1010";

whenothers=>null;

endcase;

endprocess;

process(key)

begin

casekeyis

when"0000"=>clkout<="0111111";

when"0001"=>clkout<="0000110";

when"0010"=>clkout<="1011011";

when"0011"=>clkout<="1001111";

when"0100"=>clkout<="1100110";

when"0101"=>clkout<="1101101";

when"0110"=>clkout<="1111101";

when"0111"=>clkout<="0000111";

when"1000"=>clkout<="1111111";

when"1001"=>clkout<="1101111";

when"1010"=>clkout<="1000000";

when"1011"=>clkout<="1000000";

whenothers=>clkout<="1111111";

endcase;

endprocess;

enddtsm;