集成电压比较器.docx

《集成电压比较器.docx》由会员分享,可在线阅读,更多相关《集成电压比较器.docx(16页珍藏版)》请在冰豆网上搜索。

集成电压比较器

集成电压比较器

本章主要介绍集成电压比较器的基本概念及各种集成电压比器的结构及工作原理,以及各种集成电压比较器的特点。

概述

基本概念

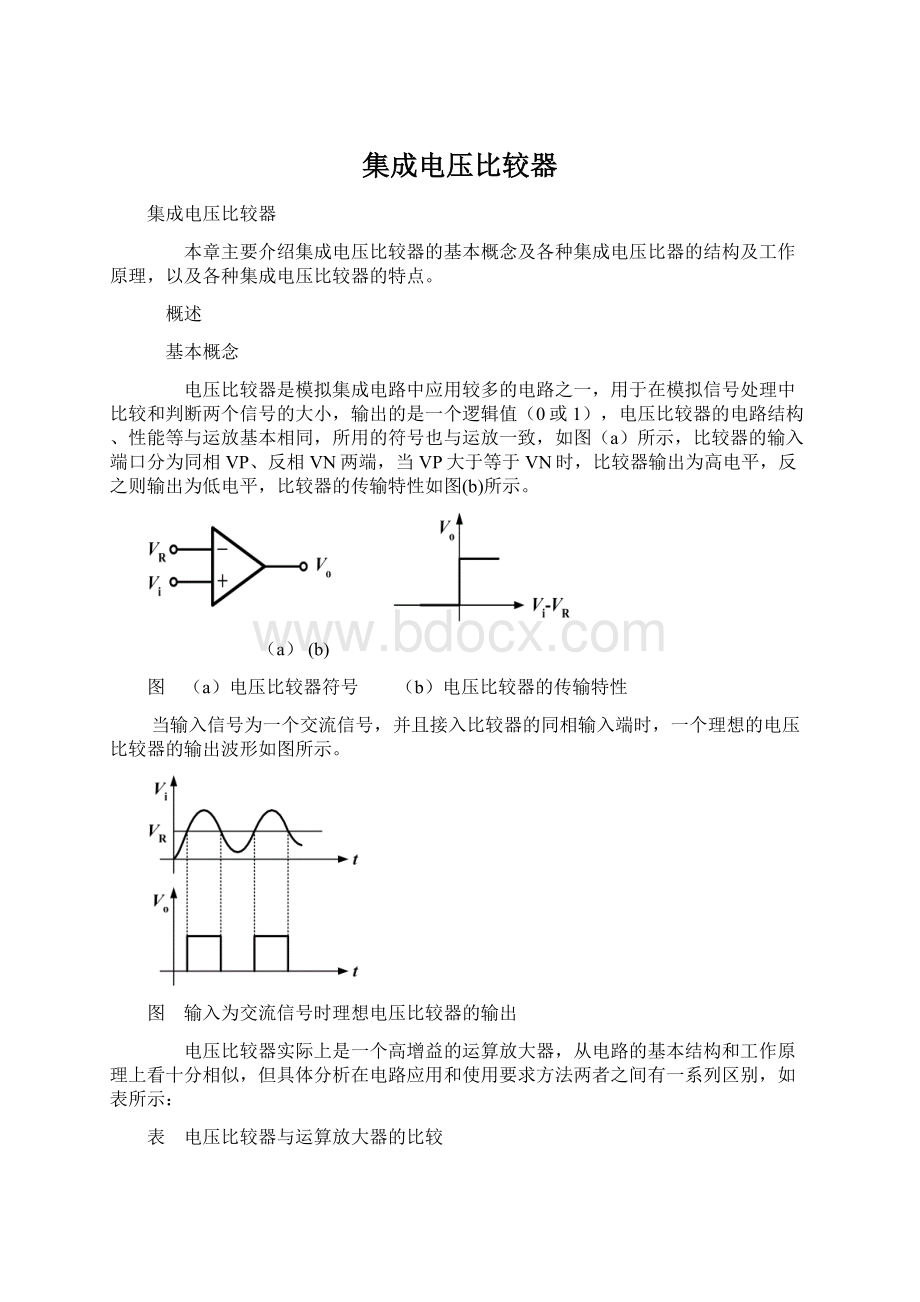

电压比较器是模拟集成电路中应用较多的电路之一,用于在模拟信号处理中比较和判断两个信号的大小,输出的是一个逻辑值(0或1),电压比较器的电路结构、性能等与运放基本相同,所用的符号也与运放一致,如图(a)所示,比较器的输入端口分为同相VP、反相VN两端,当VP大于等于VN时,比较器输出为高电平,反之则输出为低电平,比较器的传输特性如图(b)所示。

(a)(b)

图 (a)电压比较器符号 (b)电压比较器的传输特性

当输入信号为一个交流信号,并且接入比较器的同相输入端时,一个理想的电压比较器的输出波形如图所示。

图 输入为交流信号时理想电压比较器的输出

电压比较器实际上是一个高增益的运算放大器,从电路的基本结构和工作原理上看十分相似,但具体分析在电路应用和使用要求方法两者之间有一系列区别,如表所示:

表 电压比较器与运算放大器的比较

电压比较器

运算放大器

工作状态

过驱动状态

小信号状态

应用状态

开环状态

一般为闭环状态

输出状态

单端输出逻辑电平

双端或单端输出模拟量,一般要求输出摆幅大

静态输出电平

零输入时,输出为后一级逻辑电路的阈值电平

零输入时零输出

由表可以看出,在进行比较器设计时要注意以下几点:

1)直流特性的设计与运放基本相同;

2)频率特性的设计与运放大不相同,因为电压比较器一般工作于开环状态,所以不需考虑放大器闭环工作所需的频率补偿;

3)在比较器中的放大器重点要考虑的是转换速率、增益与输入失调电压。

一个高性能的电压比较器必须具有高的增益、低失调电压与高的转换速率。

电压比较器的主要参数及设计要求

1 电压比较器的主要参数如下:

1)开环电压增益AV:

直接决定了电压判别的灵敏度,增益越高,则灵敏度越高。

2)输入失调电压VOS:

也直接影响电压判别的灵敏度,失调越小,则灵敏度越高。

3)输出高电平VOH、低电平VOL:

按后级逻辑电路的要求而定。

4)瞬态响应:

决定了电压比较器的输出电压的高低压之间的转换时间,包括响应时间tR(一般分为上升时间tR1与下降时间tR2)与选通脉冲释放时间tSr。

2 电压比较器的设计考虑

电压比较器设计时,主要考虑如何提高电压比较器的灵敏度和响应时间,而电压比较器的灵敏度主要决定于电压增益和输入失调电压,其关系曲线分别如图(a)与图(b)所示。

(a)(b)

图(a)电压比较器的灵敏度与电压增益之间的关系(b)与输入失调之间的关系

上图中的△V指的是比较器的不确定区,也称为比较器的比较窗口,即为比较器的灵敏度,输入信号在此区域时输出不会发生逻辑电平变化:

1)Av增大,则△V减小,如图(a)中的虚线(代表的是Av较小)的△V2大于实线(代表的是Av较大)的△V1,若为理想的电压比较器,即Av为无穷大时,则△V趋于0,此时比较器最灵敏。

2)由于输入失调电压可为正值,也可为负值,电压比较器的比较窗口随输入失调电压的上升而增大,从图(b)中可清楚地看出减小比较器输入失调电压对提高比较器灵敏度特别重要。

设计电压比较器时,其直流特性设计分析与运放类似,但它在大信号下工作,所以电路中管子可用导通与截止进行分析。

而由于电压比较器无需考虑放大器的闭环稳定的问题,因此在设计电压比较器的频率特性时,应尽量提高比较器的响应速度。

比较器的响应时间主要与比较器的压摆率、带宽和过驱动大小有关,并且与定义的△ε大小有关,即有压摆率增大、带宽增大以及过驱动电压增大时,电压比较器的响应时间下降。

还需注意的是电压比较器的正、负输入端的响应时间 可能不同。

14.1.3电压比较器的结构

以下两种CMOS电压比较器结构的使用比较广泛:

1)级联倒相器结构

图是其基本的原理框图。

图 级联倒相器结构

这种结构大多用于静态工作模式。

2)差分放大结构

图是其基本的原理框图。

图 差分放大结构的电压比较器

每个放大器都需连接一个锁存器,锁存器的作用是快速提供一个大的输出电压,其幅度与波形与输入信号无关。

若无锁存器,则要保证电压比较器有很高的比较灵敏度时应要求差分放大器有很高的增益.

例如若比较器的灵敏度为1mV,输出电压为时,则放大器的增益必须大于3300(即70dB),而假如接上了一个锁存器,则只需考虑放大器的输出大于失调电压与锁存器的阈值电压,一般大约为或更小,此时在同样的灵敏度下,放大器的增益只需满足大于200倍即可。

这种结构有两种工作形式:

一种是静态结构,另一种是动态结构。

级联倒相器结构

基本倒相器结构

图(a)所示的是采用自偏置结构倒相器作为电压比较器原理结构,图中的M3作为开关管,时钟信号

1用于控制倒相器的自偏置,M3导通时,使得Vo=Vi,从而实现了自偏置。

由图(b)中可以看出通过改变倒相器的中MOS管的阈值电压即可改变倒相器的转换电平。

而当M3截止时,输入电压与倒相器的转换电压进行比较,如果输入信号大于倒相器的转换电压时,比较器输出为“1”,而如果输入信号小于倒相器的转换电压时,比较输出结果为“0”。

这种电压比较器由于结构简单、功耗低等特点,在快闪(FLASH)模数转换器中有应用。

(a)(b)

图(a)倒相器工作原理图(b)自偏置原理图

典型级联倒相结构比较器

图(a)所示的电路即为一个常用的CMOS比较器。

(a)(b)

图 (a)典型的级联倒相电压比较器(b)时钟控制时序及输入电压VA

在上图中,如果

2一直为低电平,则要求CA<该电路正常工作时的时序要求如图(b)所示。

工作原理及过程如下:

1)当t=0~t1期间,由于

2=

3=1,则电路如下图所示,倒相器形成一个自偏置电压寄存在C上,对不同门限电压的输入输出直流特性如下:

VC=VAB

2)当t=t1~t2时,

2=1,

3=0,由于

3的馈通效应及寄生电容CA的存在,VA的电压稍有变化,

,VA与VB不可能浮置。

3)当t=t2~t3时,

2=0,由于

2的馈通效应,C中电荷稍有变化。

4)当t≥t3,

1=1,

,

,Vi>0与Vi<0输出完全不同。

由以上的讨论可以看出,输入信号的电压通过合理安排其时钟控制,根据电荷守恒定理,通过电容而传送到倒相器的输入端VA,进而与倒相器的转换电压进行比较,实现电压比较功能。

一个完整的CMOS级联比较器如图(a)所示。

(a)

(b)

图(a)CMOS级联电压比较器(b)时钟控制信号

在图(a)中,开关管S5则用于平衡锁存器的输出。

时钟

6为锁存器的时钟。

在设计时要注意:

1)为了图(a)中的比较器能很好工作,要求M1与M3完全相同,而M2与M4完全一致,使前两个倒相器具有相同的偏置点。

2)为了减小穿通效应对波形的影响,开关管S3、S4上可加虚拟管或采用CMOS开关。

该电路的基本工作原理:

当t从0→t3为整个比较器系统予充电,当t=t5时,φ1=1,输入,当t=t6时,φ6=1,Vi进入锁存器,电路加偏置和自动归零都将由预充电过程完成(建立偏置点)。

级联比较器最大缺点是速度较慢,它受各级输出电阻和下一级输入电容的RC时间常数限制(输入电容为密勒电容,输出电阻为倒相器输出电阻)。

对于如图所示的电路,Av约为10,电阻R约为100KΩ,而输入电容Ci约为,因此,其时间常数较大,限制比较器的速度。

快速的级联结构比较器

由于典型的级联倒相器结构的最大缺点就是其速度较慢,因此为了克服这处缺点,采用了一种并行的结构,若把两组相同的级联结构比较器相并联,合理控制其时钟信号,可以使比较器的速度提高一倍以上。

如图所示的为其电路结构。

图 两组级联倒相结构的比较器相并联

在图中二路级联倒相比较器共用一个锁存器,它们在一个周期内相互交替进行放大和自动偏置归零,并且在放大期间必须要求占空比大于50%,便于使锁存器的输入能接收一个连续时间的输入信号。

并且由于锁存器的速度比倒相器的速度要快得多。

所以该结构的速度可以提高一倍。

为了保证锁存器的输入为一个连续信号,要求

A、

B的打开时间比

1、

2的接通时间早,这样可把放大器接入锁存器的时间间隔相重叠,而锁存器的时钟频率(它是比较器实际的总时钟频率)能够与放大器时钟速率不同,其时钟控制如图所示。

当然,还可以多组级联倒相结构的比较器相并联以达到更高的速度,而且其速度主要受限于锁存器的速度,因为现在的速度限制因素已为锁存器的速度,不再是放大器的速度。

图 两组级联倒相结构比较器并联的时钟控制

差分输入运算放大器结构

静态模式

作为静态模式工作的差分输入运算放大器结构的比较器一般不需要锁存器。

常规的CMOS差分放大器均可作为比较器使用,但通常由于比较器为开环工作模式,为了提高差分放大器电压增益、减小输入失调,即提高比较灵敏度,一般采用二级放大器,而且第一级为基本差分放大器,如图所示。

图中的电路为单电源工作,所以在设计时,当Vi=VR时,输出电平Vo应设计在倒相器F的转换电平上。

图 静态模式的差分放大器结构的电压比较器

工作原理:

当Vi该电压比较器的性能指标:

1)该放大器的总的电压增益为:

()

2)比较灵敏度为:

()

3)压摆率Sr

假定差分放大器的尾电流为IS,则有:

()

4)建立时间ts为:

()

在CMOS电压比较器中可充分和MOS输入的高输入阻抗,利用电容的存贮效应和电容上电压不能突变的特性,实现电压比较,电路可大大简化、性能良好。

当然,对于静态模式的差分输入运算放大器结构的电压比较器还有很多结构,如带有电平移位功能的电压比较器等。

动态工作模式

动态工作模式的差分输入运算放大器结构的比较器还可细分为不带锁存器的电压比较器与带锁存器的电压比较器两类。

1、不带锁存器的结构

1)单端输入的差分运算放大器结构的比较器

不带锁存器的差分输入运算放大器结构的电压比较器如图所示。

在图中,电容C2为频率补偿电容。

为了避免M8的时钟馈通效应(即时钟

1),要求M10的时钟

3要先于时钟

1变低。

该电路的特点工作原理及工作过程为:

1)当

1=1,

2=0时,比较器处于缓冲(全反馈)状态,为防止二级放大器自激,采用M11,C2频率补偿,这时电路实现予充电。

2)

2=1,

1=0时比较器处于开环工作,增益很高,由于补偿电路开路(不用)大大提高了电路工作速度(由于补偿电路大大增加了第一级RC常数、降低了电路速度)。

假定输入失调为VOS(包括偏置电压),当

1=1时,VA=Vi-VOS,则当

2=1时,VA=VR-Vi+VOS的阶跃信号。

图 不带锁存器的单端输入的差分运放结构电压比较器

2) 全差分比较器

一个全差分比较器如图所示。

图. 全差分比较器

在上图中,电容C1、C2是自动调零用的电容。

并且开关管M1与M2会在节点A与节点B处产生时钟馈通,引起比较器的比较失误,所以在实际应用中应该接入一个共模负反馈网络,以提高电路的共模抑制比。

在全差分比较器中,由于时钟馈入,电源噪声和1/f噪声等都是共模信号,而根据全差分放大器的特点可以知道,在理想情况下其共模抑制比为无穷大,所以这些共模信号都被对消和抑制。

这是全差分比较器的一个明显的优点。

假定放大器的自偏输入电压为VS,则有:

(1)当φ1=1,φ2=0时,VA=Vi-VS,VB=Vi-VS;

(2)当φ2=0,φ1=1时,在节点上产生的阶跃电压为:

VA=Vi+-Vi-,VB=Vi--Vi+,

同时在输出产生Vo+与Vo-。

(3)为了进一步改善共模抑制比,VB2偏压可以从输出Vo+-Vo-反馈获得。

2 带锁存器的结构

1) 典型的锁存电路

典型的带锁存器的差分输入运算放大器结构的电压比较器电路一般都采用直接耦合的差分放大器,如图所示。

图 差分输入的直接耦合锁存电路

在图中,当时钟φ1=1时为预充电过程,而当时钟φ2=1则为选通过程。

该电路实际上是一个交叉耦合的双稳态多谐振荡器,电路的工作过程如下:

(1)当φ1=1(φ2=0)时,C1,C2被预充电至输入电压;

(2)当φ2=1(φ1=0)时,选通使锁存器状态输出,其状态决定Vi+-Vi-的符号。

在以上的电路中,如果要求采用单端输入时,则Vi+或Vi-可用门限电压代替或用自偏置来产生。

2) 带锁存器的电压比较器

带锁存器的电压比较器也称为带有自动调零的电容耦合锁存器的电压比较器,其电路如图所示。

图中的比较器的工作过程如下:

(1)当φ2=1时,倒相器M2、M5和M9、M12加上耦合电容C4、C3组成一个双稳态多谐振荡器,并且偏置在线性区(给电容C3、C4预充电)通过C3、C4可提供稍微不同的偏压补偿了两个倒相器之间任何不对称性,此时多谐振荡器的环路增益小于1,因此它不能转换到它任一个稳定状态。

(2)当φ1=1,φ3=1时(φ2仍为高电平)则C1予充电至Vi+-VB;

(3)当φ1=0时,M1和M8解除自偏状态,使C1、C2浮置。

(4)当φ3=0时,VA、VB的电压由自偏置分别改为Vi+-Vi-,Vi--Vi+,这就引起多谐振荡器内部VC、VD电压相应变化;

(5)当φ2=0时,起动多谐振荡器进入相应稳定状态。

(6)如果Vi+Vi-,则VC为低电平而VD为高电平。

图 带锁存器的电压比较器

图是图所示的电路正常工作所需的时序控制。

图 图的工作时序

3) 前置放大器与锁存器组合而成的电压比较器

图 前置放大器与锁存器组合成的电压比较器

前置放大器与锁存器组合而成的电压比较器的电路如图所示。

而图则为其工作所需的时钟控制信号。

图中的电路的工作过程:

(1)当φ2=1时,M5、M1、M2、M3、M4组成一个前置放大器;

(2)当φ2=0时,M14、M13、M12、M3、M4组成一个双稳态多谐振荡器,其工作过程如下:

a)当φ1=φ2=φ3=1时,前置放大器自给偏置电压,即C1、C2预充电,VC1的电平为Vi+-VA,VC2电平为Vi+-VB

b)当φ1=0时,前置放大器执行放大功能,这时C1、C2的节点A、B浮置,接着φ3=0,这时VA、VB电压由自偏置改变为Vi+-Vi-及Vi--Vi+,使得节点C、D之间产生一个被放大的电压差。

c)当φ2=0时,M5截止,M6导通,使多谐振荡器工作,呈现某一稳定状态,状态的选择由VC-VD决定。

图 图中的电路的工作时序

从以上分析可以看出放大器和锁存器采用相同类型的倒相器组成,但放大器的上升、下降时间远比锁存器翻转时间长。

采用如图(a)所示的电路结构来分析,其等效电路如图(b)所示。

(a)(b)

图(a)锁存器的电路 (b)(a)的交流小信号等效电路

图(a)中,对于交流小信号而言VDD相当于接地,则有:

()

()

在图(b)中电容C代表加在节点V1、V2端的电容,从等效电路可以看出当组成直接耦合双稳态多谐振荡器后,由于具有完全正反馈,其时间常数为

()

当组成放大器的简单级联时,由于不存在正反馈,所以其时间常数为

由式()与式()可以得到:

()

上式中A为倒相器的增益,由式()可以看出锁存器比驱动放大器快一个数量级以上,即放大器的上升、下降时间远比锁存器翻转时间长。