电子时钟Multisim仿真设计.docx

《电子时钟Multisim仿真设计.docx》由会员分享,可在线阅读,更多相关《电子时钟Multisim仿真设计.docx(11页珍藏版)》请在冰豆网上搜索。

电子时钟Multisim仿真设计

一、设计指标

1.时间以24小时为一个周期;

2.显示时、分、秒;

3.有校时功能,可以分别对时及分进行单独校时,使其校正到标准时间;

4.保证计时的稳定及准确须由晶体振荡器提供表针时间基准信号。

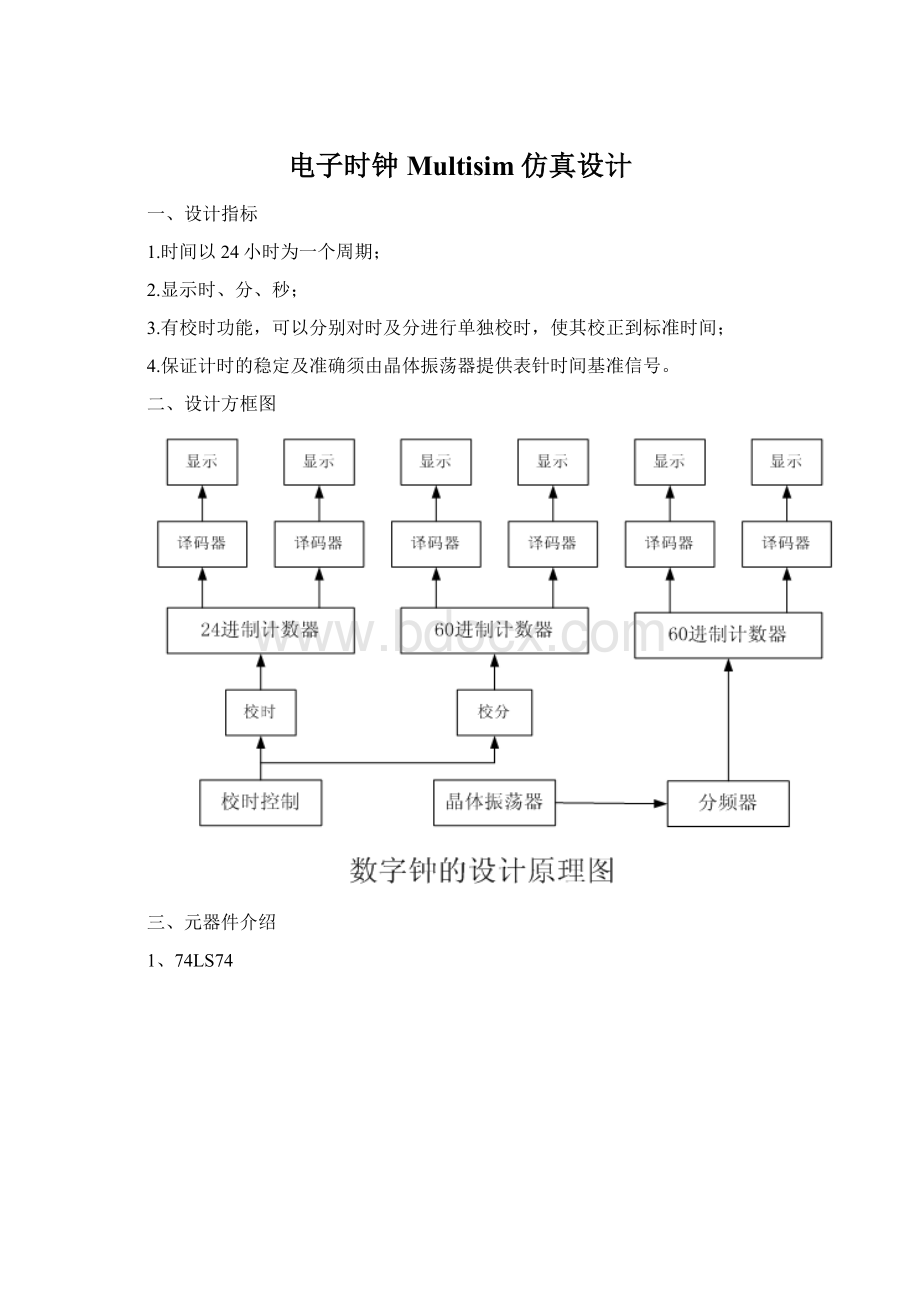

二、设计方框图

三、元器件介绍

1、74LS74

74LS74部结构图74LS74管脚图

2、74LS47译码器

74LS47是输出低电平有效的七段字形译码器,该电路是由与非门、输入缓冲器和7个与或非门组成的BCD-7段译码器/驱动器。

通常是低电平有效,高的灌入电流的输出可直接驱动显示器。

7个与非门和一个驱动器成对连接,以产生可用的BCD数据及其补码至7个与或非译码门。

剩下的与非门和3个输入缓冲器作为试灯输入(LT)端、灭灯输入/动态灭灯输出(BI/RBO)端及动态灭灯输入(RBI)端。

74LS47译码器

LT

L

×

××××

H

LLLLLLL

(5)

74LS47译码器真值表

注:

1、当需要0到15的输出功能时,灭灯输入(BI)必须为开路或保持在高逻辑电平,若不要灭掉十进制零,则动态灭灯输入(RBI)必须开路或处于高逻辑电平。

2、当低逻辑电平直接加到灭灯输入(BI)时,不管其它任何输入端的电平如何,所有段的输出端都关死。

(H=高电平L=低电平×=不定)3、当动态灭灯输入(RBI)和输入端A、B、C、D都处于低电平而试灯输入(LT)为高时,则所有段的输出端进入关闭且动态灭灯输出(RBO)处于低电平(响应条件)。

4、当灭灯输入/动态灭灯输出(BI/RBO)开路或保持在高电平,且将低电平加到试灯输入(LT)时,所有段的输出端都得打开。

*BI/RBO是用作灭灯输入(BI)与/或动态灭灯输出(RBO)的线与逻辑。

3、74LS390

74LS390管脚图双十进制计数器

4、74LS082输入端四AND

74LS08管脚图74LS08真值表

5、74LS00管脚图6、74HC51D

774LS51与或非门管脚图

7、4060BP-5V

4060BP管脚图

4060BP结构图

8、七段显示数码管

数码显示器有多种,按显示方式可分为分段式、点阵式和重叠式;按发光材料可分为辉光显示器、荧光显示器、发光二极管显示器和液晶显示器等。

目前普遍使用的七段式数字显示器主要有发光二极管和液晶显示器两种。

这里主要介绍七段发光二极管组成的数码管原理。

数码管按照其发光二极管的连接方式不同,可分为共阳极和共阴极两种。

共阴极是指数码管中所有发光二极管的阴极连在一起接低电平,而阳极分别由a、b、c、d、e、f、g输入信号驱动,当某个输入为高电平时,相应的发光二极管点亮;共阳极数码管则相反,它的所有发光二极管的阳极连在一起接高电平,而阴极分别由a、b、c、d、e、f、g输入信号驱动,当某个输入为低电平时,相应的发光二极管点亮。

三、设计原理

1、各功能模块电路的设计(用Multisim仿真)

4060构成脉冲发生及分频电路

74LS47构成译码驱动电路

校时电路(分校时时,不会进位到小时)

2、整体电路图(用Multisim仿真)

四、电路安装与调试过程

根据原理和芯片引脚图,分功能设计原理图,并根据接线顺序分步骤验证。

按照原理图接线时首先确保可靠的电源和接地。

注意芯片的控制引脚必须正确。

容易出现故障为接触不良。

集成块引脚方向预先弯好对准面包板的金属孔,再小心插入。

导线的剥线长度与面包板的厚度相适应(比板的厚度稍短)。

导线的裸线部分不要露在板的上面,以防短路。

导线要插入金属孔中央。

五、电路测试与使用说明

检查故障时除测试输入、输出信号外,要注意电源、接地和控制引脚。

要注意芯片引脚上的信号与面包板上插座上信号是否一致(集成块引脚与面包板常接触不良)。

为了便于测试,可将2Hz信号直接输入到各级计数器。

接校时电路时可接模拟信号输入(如1Hz和2Hz)测试输出信号的切换正确后,再将秒进位和分进位信号接到校时电路,再接校时电路输出到分计数器和时计数器。

从较时电路接入信号时,必须将原进位信号拔掉。

六、训练总结

本次实训相比较之前的两次对理论和实践的要求能力相对提高,要求我们在了解线路以及各器件部分功能的基础上,先进行仿真设计。

然后在进行实体操作。

对于我们的细心,耐心是很大的考验。

由于器件较多,线路错综,很容易在连线过程中出现错接,漏接的情况。

即使连接错误,也不一定会实现最初目标,达到功能。

还要针对错误现象,排查原因,在连线正确的基础上,可能是元器件的故障,采用示波器进行观察,然后进行更换,逐步调整,最终实现校时,计时功能,完成实训目标。