四输入与非门电路版图设计.docx

《四输入与非门电路版图设计.docx》由会员分享,可在线阅读,更多相关《四输入与非门电路版图设计.docx(11页珍藏版)》请在冰豆网上搜索。

四输入与非门电路版图设计

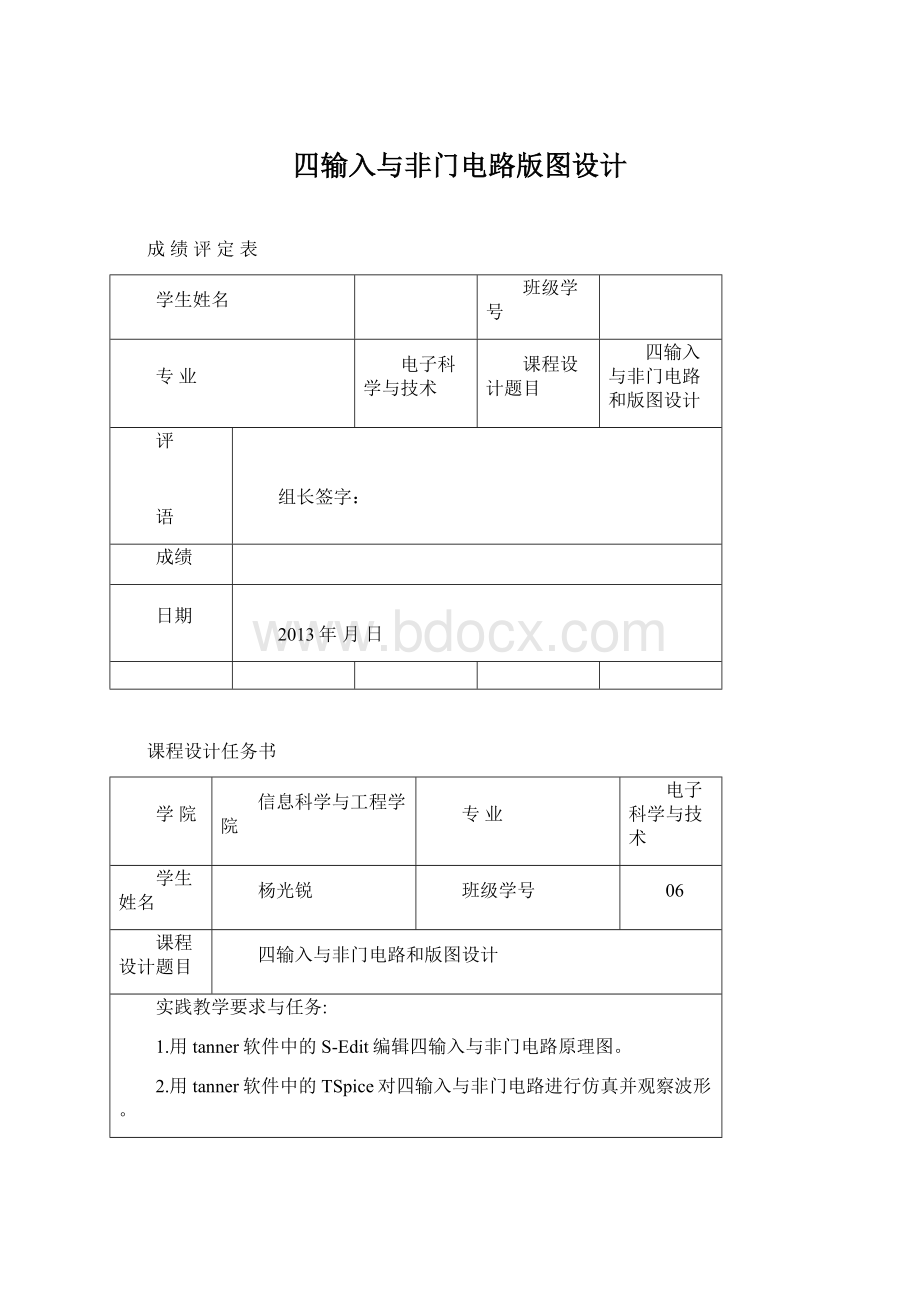

成绩评定表

学生姓名

班级学号

专业

电子科学与技术

课程设计题目

四输入与非门电路和版图设计

评

语

组长签字:

成绩

日期

2013年月日

课程设计任务书

学院

信息科学与工程学院

专业

电子科学与技术

学生姓名

杨光锐

班级学号

06

课程设计题目

四输入与非门电路和版图设计

实践教学要求与任务:

1.用tanner软件中的S-Edit编辑四输入与非门电路原理图。

2.用tanner软件中的TSpice对四输入与非门电路进行仿真并观察波形。

3.用tanner软件中的L-Edit绘制四输入与非门版图,并进行DRC验证。

4.用tanner软件中的TSpice对版图电路进行仿真并观察波形。

5.用tanner软件中的layout-Edit对电路网表进行LVS检验观察原理图与版图的匹配程度。

工作计划与进度安排:

第一周

周一:

教师布置课设任务,学生收集资料,做方案设计。

周二:

熟悉软件操作方法。

周三~四:

画电路图

周五:

电路仿真。

第二周

周一~二:

画版图。

周三:

版图仿真。

周四:

验证。

周五:

写报告书,验收。

指导教师:

2012年月日

专业负责人:

2013年月日

学院教学副院长:

2013年月日

1绪论

设计背景

tanner是用来IC版图绘制软件,许多EDA系统软件的电路模拟部分是应用Spice程序来完成的,而tanner软件是一款学习阶段应用的版图绘制软件,对于初学者是一个上手快,操作简单的EDA软件。

Tanner集成电路设计软件是由TannerResearch公司开发的基于Windows平台的用于集成电路设计的工具软件。

该软件功能十分强大,易学易用,包括S-Edit,T-Spice,W-Edit,L-Edit与LVS,从电路设计、分析模拟到电路布局一应俱全。

其中的L-Edit版图编辑器在国内应用广泛,具有很高知名度。

L-EditPro是TannerEDA软件公司所出品的一个IC设计和验证的高性能软件系统模块,具有高效率,交互式等特点,强大而且完善的功能包括从IC设计到输出,以及最后的加工服务,完全可以媲美百万美元级的IC设计软件。

L-EditPro包含IC设计编辑器(LayoutEditor)、自动布线系统(StandardCellPlace&Route)、线上设计规则检查器(DRC)、组件特性提取器(DeviceExtractor)、设计布局与电路netlist的比较器(LVS)、CMOSLibrary、MarcoLibrary,这些模块组成了一个完整的IC设计与验证解决方案。

L-EditPro丰富完善的功能为每个IC设计者和生产商提供了快速、易用、精确的设计系统。

设计目标

1.用tanner软件中的原理图编辑器S-Edit编辑四输入与非门电路原理图。

2.用tanner软件中的W-Edit对四输入与非门电路进行仿真,并观察波形。

3.用tanner软件中的L-Edit绘制四输入与非门版图,并进行DRC验证。

4.用W-Edit对四输入与非门的版图电路进行仿真并观察波形。

5.用tanner软件中的layout-Edit对四输入与非门进行LVS检验观察原理图与版图的匹配程度。

2四输入与非门电路

电路原理图

用CMOS实现四输入与非门电路,PMOS和NMOS管进行全互补连接方式,栅极相连作为输入,电路上面是四个PMOS并联,PMOS的漏极与下面NMOS的漏极相连作为输出,POMS管的源极和衬底相连接高电平,NMOS管的源极与衬底相连接低电平;原理图如图所示。

图四输入与非门电路原理图

与非门电路仿真观察波形

给四输入与非门的输入加激励,高电平为Vdd=5V,低电平为Gnd,并添加输入输出延迟时间,进行仿真,并输出波形;波形图如下图所示。

图四输入与非门电路输入输出波形图

由波形可以看出,当输入A,B,C,D都为高电平时,输出低电平;其它情况,也就是只要有一个零输出就为高电平。

与非门电路的版图绘制

用L-Edit版图绘制软件对电路进行四输入与非门电路版图绘制,同时进行DRC验证,查看输出结果,检查有无错误;版图和输出结果如下图所示。

图四输入与非门电路版图

四输入与非门版图仿真观察波形

同四输入与非门电路原理图仿真相同,添加激励、电源和地,同时观察输入输出波形;波形如下图所示。

图四输入与非门电路版图输入输出波形图

由波形可以看出,输入A,B,C,D都为高电平时,输出低电平;其它情况,也就是只要有一个零输出就为高电平。

四输入与非门电路的版图仿真波形与原理图的仿真输出波形基本一致,并且符合输入输出的逻辑关系,电路的设计正确无误。

LVS检查匹配

用layout-Edit对反相器进行LVS检查验证,首先添加输入输出文件,选择要查看的输出,观察输出结果检查反相器电路原理图与版图的匹配程度;输出结果如下图所示。

图四输入与非门电路LVS检查匹配图

总结

通过本次模拟电路版图课程设计,我受益匪浅。

不仅巩固我们已学的版图工艺的理论知识,提高我们电子电路的设计水品,而且加强我们综合分析问题和解决问题的能力,进一步培养我们的实验技能和动手能力,启发我们创新意识及创新思维。

在设计过程中我们将理论联系实际,在不断的改进设计中提高自己,完善自己的技能,达到了理论与实际的真正结合......

在版图设计的后期,模拟出波形时,还是遇到了一些困难,可能是因为移动文件改变了路径而出不了波形,但是在老师悉心的指导及同学的热情帮助下,我最终找出了问题的根源并顺利完成设计......

参考文献

[1]钟文耀,郑美珠.CMOS电路模拟与设计—基于tanner.全华科技图书股份有限公司印行,2006.

[2]刘刚等著.微电子器件与IC设计基础.第二版.科学出版社,2009.

[3]AlanArtofAnalogEdition.电子工业出版社.2013

附录一:

电路原理图网表

*SPICEnetlistwrittenbyS-EditWin32

*WrittenonJul5,2013at08:

54:

09

*Waveformprobingcommands

.probe

.optionsprobefilename="D:

\study\tanner\S-Edit\tutorial\Q\"

+probesdbfile="D:

\study\tanner\S-Edit\tutorial\Q\"

+probetopmodule="Module0"

*Maincircuit:

Module0

M1YDN16GndNMOSL=2uW=22uAD=66pPD=24uAS=66pPS=24u

M2N16CN19GndNMOSL=2uW=22uAD=66pPD=24uAS=66pPS=24u

M3N19BN22GndNMOSL=2uW=22uAD=66pPD=24uAS=66pPS=24u

M4N22AGndGndNMOSL=2uW=22uAD=66pPD=24uAS=66pPS=24u

M5YCVddVddPMOSL=2uW=22uAD=66pPD=24uAS=66pPS=24u

M6YDVddVddPMOSL=2uW=22uAD=66pPD=24uAS=66pPS=24u

M7YBVddVddPMOSL=2uW=22uAD=66pPD=24uAS=66pPS=24u

M8YAVddVddPMOSL=2uW=22uAD=66pPD=24uAS=66pPS=24u

.include"D:

\study\tanner\TSpice70\models\"

.tran/op2n500nmethod=bdf

.printtranv(Y)v(A)v(B)v(C)v(D)

VsoueVddGnd5

VsssAAGndPULSE(052n2n2n50n100n)

VsssBBGndPULSE(052n2n2n60n120n)

VsssCCGndPULSE(052n2n2n80n150n)

VsssDDGndPULSE(052n2n2n110n160n)

*Endofmaincircuit:

Module0

附录二:

版图网表

*CircuitExtractedbyTannerResearch'sL-EditVersion/ExtractVersion;

*TDBFile:

D:

\study\tanner\S-Edit\tutorial\Q\

*Cell:

Cell0Version

*ExtractDefinitionFile:

D:

\study\tanner\LEdit90\Samples\SPR\example1\

*ExtractDateandTime:

07/05/2013-08:

53

.includeD:

\study\tanner\TSpice70\models\

*Warning:

LayerswithUnassignedAREACapacitance.

*

*

*

*

*

*

*Warning:

LayerswithUnassignedFRINGECapacitance.

*

*

*

*

*

*

*

*

*Warning:

LayerswithZeroResistance.

*

*

*

*

M811031PMOSL=2uW=7u

*M8DRAINGATESOURCEBULK(6264

M73911PMOSL=2uW=7u

*M7DRAINGATESOURCEBULK(5456

M61831PMOSL=2uW=7u

*M6DRAINGATESOURCEBULK(4648

M53711PMOSL=2uW=7u

*M5DRAINGATESOURCEBULK(3840

M431062NMOSL=2uW=7u

*M4DRAINGATESOURCEBULK(6264

M36952NMOSL=2uW=7u

*M3DRAINGATESOURCEBULK(5456

M25842NMOSL=2uW=7u

*M2DRAINGATESOURCEBULK(4648

M14722NMOSL=2uW=7u

*M1DRAINGATESOURCEBULK(3840

*TotalNodes:

10

*TotalElements:

8

*TotalNumberofShortedElementsnotwrittentotheSPICEfile:

0

*ExtractElapsedTime:

0seconds

.include"D:

\study\tanner\TSpice70\models\"

.tran/op2n500nmethod=bdf

.printtranv(Y)v(A)v(B)v(C)v(D)

VsoueVddGnd5

VsssAAGndPULSE(052n2n2n50n100n)

VsssBBGndPULSE(052n2n2n60n120n)

VsssCCGndPULSE(052n2n2n80n150n)

VsssDDGndPULSE(052n2n2n110n160n)

.END