基于verilog数字钟设计报告.docx

《基于verilog数字钟设计报告.docx》由会员分享,可在线阅读,更多相关《基于verilog数字钟设计报告.docx(27页珍藏版)》请在冰豆网上搜索。

基于verilog数字钟设计报告

一、课程设计目标

1.熟悉并掌握verilog硬件描述语言

2.熟悉quartus软件开发环境

3.学会设计大中规模的数字电路,并领会其中的设计思想

二、课程设计实现的功能

(1)设计一个数码管实时显示时、分、秒的数字时钟(24小时显示模式);

(2)可以调节小时,分钟。

(3)能够进行24小时和12小时的显示切换。

(4)可以设置任意时刻闹钟,并且有开关闹钟功能。

(5)有整点报时功能,几点钟LED灯闪亮几下。

(6)有复位按键,复位后时间从零开始计时,但闹钟设置时间不变。

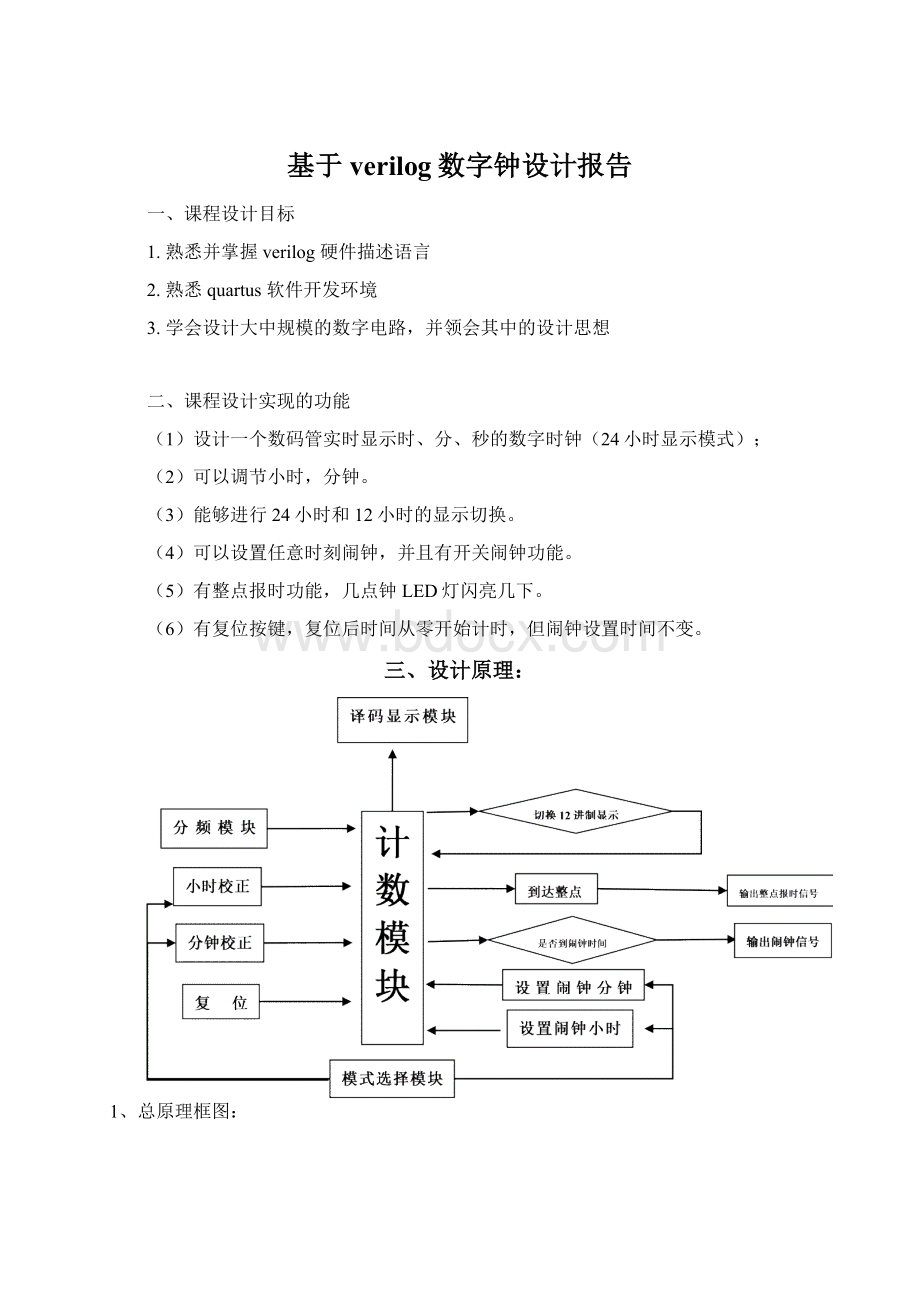

三、设计原理:

1、总原理框图:

是

是

2、各个子模块设计:

(1)、分频模块:

分频模块的作用主要是要获得各种频率的时钟信号。

输入信号为50MHZ的信号,要想获得1HZ的信号作为秒脉冲计时,则要对50MHZ信号分频。

通过计数的方式,当计数从0开始到24999999时,1HZ信号取反一次,计数又从0开始,如此循环,就可以得到1HZ脉冲信号。

对于其他信号也是如此,只是计数值不一样,得到的分频信号不同。

部分代码如下:

always@(posedge_50MHZornegedgenCR)begin

if(~nCR)

begin

Q1<=32'd0;

end

elseif(Q1>=32'd24999999)

begin

Q1<=32'd0;

_1HZ=~_1HZ;

end

elsebegin

Q1<=Q1+1'd1;

end

(2)、计数模块:

秒计数:

在1HZ脉冲下进行秒计时,当计时达到59秒后,在下一个脉冲来临变0,并发出一个脉冲信号,可供下面分钟计数作为输入脉冲信号计时。

分钟计数:

在输入脉冲下,分钟开始计时,当计时达到59后,在下一个脉冲来临变0,并发出一个脉冲,供小时计数的输入脉冲新号。

小时计数:

脉冲信号来临时,计数加1,达到23后在下一个脉冲的作用下清零,从新计时。

如果有复位信号,则时分秒全部清零。

部分代码如下:

modulesecond(cp,reset,mode_flag,BT2,SH,SL,co);

inputcp,reset,BT2;

input[3:

0]mode_flag;

outputco=1'b0;//输出脉冲信号

regco;

output[3:

0]SL,SH;//输出秒计时的十位、各位

reg[3:

0]SH,SL;

reg[7:

0]cnt;

always@(posedgecpornegedgereset)

begin

if(!

reset)begin//有复位,清零

cnt<=8'd0;

SH<=4'd0;

SL<=4'd0;end

elseif((mode_flag==4'b0010)&&(!

BT2))begin//如果分钟调节,秒清零

cnt<=8'd0;

SH<=4'd0;

SL<=4'd0;end

if(cnt==8'd59)//计时达到59,下一个脉冲下从新计时

begin

cnt<=8'd0;

SH<=4'd0;

SL<=4'd0;

co<=1'b1;

end

else

begin

co=1'b0;

cnt=cnt+8'd1;

SL<=cnt%10;//秒十位

SH<=cnt/10;//秒各位

end

end

end

endmodule

分计时和小时计时代码和上述类似,不再举出。

secondu4(_1HZ,reset,mode_flag,Keydone2,SH24,SL24,co1);

minuteu5(co11,reset,MH24,ML24,co2);

houru6(co22,reset,HH24,HL24);

(2)、模式选择模块:

同过一个模式档按键MODE,按一下产生对应一种模式mode_flag,并且可以循环。

在不同的模式下可以进行不同的操作。

其中mode_flag=4'0000为正常显示计时,mode_flag=4'0001为小时调钟模式,mode_flag=4'00010为分钟调钟模,mode_flag=4'0011为闹钟小时设置模式,mode_flag=4'0100为闹钟分钟设置模式。

模式产生:

modulemode(MODE,mode_flag);

inputMODE;

output[3:

0]mode_flag;

reg[3:

0]mode_flag;

always@(negedgeMODE)begin//如果检测到有按键按下

mode_flag=mode_flag+4'b1;//模式值加1

if(mode_flag==4'b0101)//到最后一个模式后返回第一的模式

mode_flag=2'b0;nd

Endmodule

模式选择:

modulemode_choose(mode_flag,BT2,_250ms,co1,co2,set_co2,co11,co22,co111,co222);

input[3:

0]mode_flag;//输入模式方式,响应对应操作

inputBT2,_250ms,co1,co2,set_co2;//调节按钮,时钟信号,正常计时分钟脉冲信号,正常计时小时脉冲信号,闹钟设置分钟进位信号。

outputco11,co22,co111,co222;//分钟脉冲信号,小时脉冲信号,闹钟设置分钟脉冲信号,闹钟设置小时脉冲信号;

supply1Vdd;

regco11,co22,co111,co222;

always@(mode_flag)begin

case(mode_flag)

4'b0001:

begin

if(~BT2)co22<=_250ms;//小时调钟模式,有按键,则脉冲为250ms

elsebeginco22<=co2;//没有按键,正常计时

co11<=co1;end

end

4'b0010:

begin

if(~BT2)beginco11<=_250ms;//小时调钟模式,有按键,则脉冲为250ms

co22<=co2;end

elsebeginco11<=co1;//没有按键,正常计时

co22<=co2;end

end

4'b0011:

beginco22<=co2;

co11<=co1;

if(~BT2)co222<=_250ms;//闹钟小时设置信号

elseco222<=set_co2;end

4'b0100:

beginco22<=co2;

co11<=co1;

if(~BT2)co111<=_250ms;//闹钟分钟设置信号

elseco111<=Vdd;end

default:

begin

co11<=co1;

co22<=co2;end

endcase

end

endmodule

(2)、任意闹钟模块:

一、设置闹钟:

当对应于闹钟设置模式mode_flag=4'0011和4'b0100时,有设置信号输入时,则开始设置。

对应代码:

moduleset_naozhong(co111,co222,set_HH,set_HL,set_MH,set_ML,co2);

inputco111,co222;//闹钟分钟,小时设置信号

output[3:

0]set_HH,set_HL,set_MH,set_ML;//输出相应的闹钟设置时间

supply1Vdd;

outputco2;

minute(co111,Vdd,set_MH,set_ML,co2);

hour(co222,Vdd,set_HH,set_HL);

endmodule

二、闹钟响应:

当正常计时达到闹钟设置得时间后,通过比较二者之间的时间,相等,则产生一个闹钟允许响应信号,在闹钟开关打开和闹钟允许响应信号同时满足的情况下,则产生闹钟响应信号,并送到相应的闹钟设备LED灯。

如果闹钟档处于关闭状态,则不会产生闹钟响应信号。

响应代码如下:

modulenaozhong(Alarm_ctr,_1HZ,set_HH,set_HL,set_MH,set_ML,HH24,HL24,MH24,ML24,nao_signal);

inputAlarm_ctr,_1HZ;

input[3:

0]set_HH,set_HL,set_MH,set_ML;

input[3:

0]HH24,HL24,MH24,ML24;

outputnao_signal;

regsignal;

regnao_signal;

reg[16:

0]Q;//计数,调节闹钟响应时间长度

always@(posedge_1HZ)begin

if((~signal)&&(Alarm_ctr))beginif((set_HH==HH24)&&(set_HL==HL24)&&(set_MH==MH24)&&(set_ML==ML24))signal<=1'b1//达到闹钟设置时间,产生闹钟允许响应信号

elsesignal<=1'b0;end//未达到,不产生

elseif((signal)&&(Alarm_ctr))begin//闹钟开关打开和闹钟允许响应信号同时满足

nao_signal<=~nao_signal;//产生闹钟响应信号

Q=Q+nao_signal;

if(Q>=8'd720)begin//响应时间完毕,关闭闹钟允许响应信号

Q<=16'b0;

signal<=1'b0;end

end

elsebegin

signal<=1'b0;

nao_signal<=1'b0;end

end

endmodule

(2)、整点报时模块:

检测分钟和秒钟计数是否都达到了59,然后再下一个秒脉冲的作用下发出整点报时信号,送到LED。

并开始计数,计数达到报时信号响应次数后,终止报时信号。

部分代码如下:

always@(posedge_500ms)begin

if(((SH*10+SL)==8'd59)&&((MH*10+ML)==8'd59))begin

Q1<=7'b0;

bao<=1'b1;end//允许报时

elseif((Q1<10*HH+HL)&&(bao))begin

bao_signal<=~bao_signal;//产生报时信号

Q1<=Q1+bao_signal;//响一次计数加一

end

elseif(Q1==(10*HH+HL))//报时次数达到整点时数,终止信号

bao<=1'b0;

else

begin

bao_signal<=1'b0;

end

End

(2)、12—24小时切换模块:

将24小时切换成12小时,并存入相应的寄存器。

如果拨上切换显示档,则切换显示。

相应代码如下:

modulehour12_24(HH24,HL24,HH12,HL12);

input[3:

0]HH24,HL24;

output[3:

0]HH12,HL12;

reg[3:

0]HH12,HL12;

always@(HH24orHL24)begin