昆工计科组成原理实验の计算机组成原理各部件实验.docx

《昆工计科组成原理实验の计算机组成原理各部件实验.docx》由会员分享,可在线阅读,更多相关《昆工计科组成原理实验の计算机组成原理各部件实验.docx(35页珍藏版)》请在冰豆网上搜索。

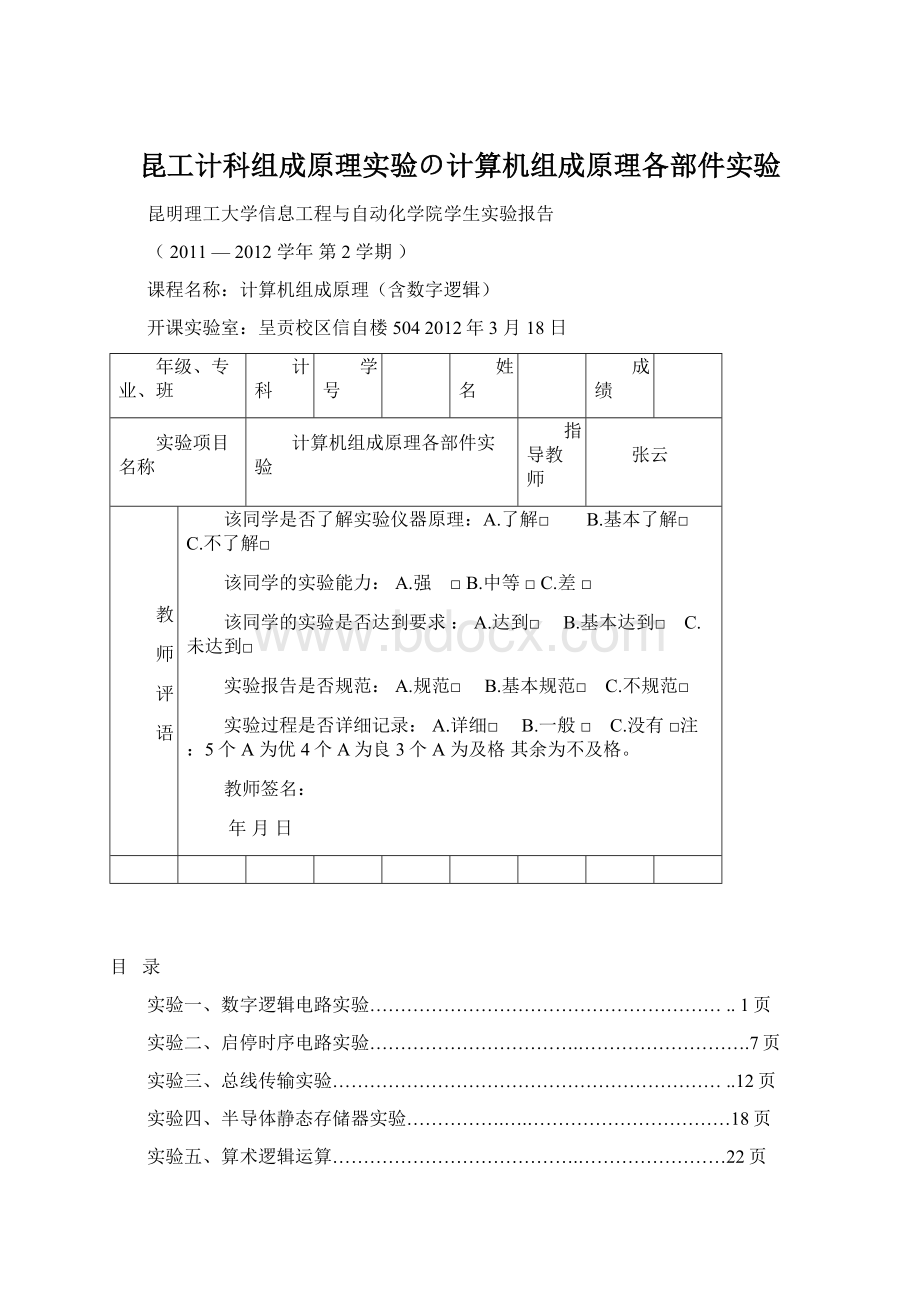

昆工计科组成原理实验の计算机组成原理各部件实验

昆明理工大学信息工程与自动化学院学生实验报告

(2011—2012学年第2学期)

课程名称:

计算机组成原理(含数字逻辑)

开课实验室:

呈贡校区信自楼5042012年3月18日

年级、专业、班

计科

学号

姓名

成绩

实验项目名称

计算机组成原理各部件实验

指导教师

张云

教

师

评

语

该同学是否了解实验仪器原理:

A.了解□ B.基本了解□ C.不了解□

该同学的实验能力:

A.强 □B.中等□C.差□

该同学的实验是否达到要求:

A.达到□ B.基本达到□ C.未达到□

实验报告是否规范:

A.规范□ B.基本规范□ C.不规范□

实验过程是否详细记录:

A.详细□ B.一般□ C.没有□注:

5个A为优4个A为良3个A为及格其余为不及格。

教师签名:

年月日

目录

实验一、数字逻辑电路实验…………………………………………………..1页

实验二、启停时序电路实验…………………………….……………………….7页

实验三、总线传输实验………………………………………………………..12页

实验四、半导体静态存储器实验…………….….……………………………18页

实验五、算术逻辑运算………………………………….……………………22页

实验六、控制器电路实验……….…………….………………………………27页

实验一、数字逻辑电路实验

一、实验目的

1.了解数据输入输出

2.理解数码显示译码器的作用

3.学会使用数码管的检测极限是一码器的使用

4.掌握七段显示译码器的设计

二、实验原理及基本技术路线图(方框原理图)

(1)输入输出的基本原理及结构

实验中所用的输入输出数据通路如图1.1所示。

图中左部是由数据开关和三态门245构成的二进制数据输入单元;图中右部则是由七段显示译码器和SM420501K数码管构成的数据输出单元。

1.1输入输出通路图

数据输入单元(实验板上印有INPUTDEVICE)用以提供数据。

其中,输入

开经过一个三态门(74LS245),该三态门的控制信号SW-B取低电平时,开关上的数据就通过三态门而送入。

数据输出单元(实验板上印有OUTPUTDEVICE)用以显示数据。

其中,输出开经过一个七段显示译码器,该译码器的控制信号LED-B为电平信号,W/R(LED)为脉冲信号,并且当LED-B取低电平,W/R(LED)为一个下降沿脉冲时可将输出数据打入到译码器。

该译码器的输出再用于驱动一个共阴极的七段LED数码管(SM420501K)来显示信息。

SM420501K数码管的外形图如图1.2所示。

图1.2SM420501K数码管的外形图

(2)七段显示译码器的设计步骤

显示译码器是组合逻辑电路的一个重要的器件,它主要解决二进制数转换成数码管所需的驱动信号,以便使数码管用十或十六进制数字显示出对应的二进制代码所表示的数值。

显示译码器有4个输入端7个输出端。

输入为二进制代码,输出为七段显示码,即根据需要7根输出线中有些是有效电平,而其它则不是。

设计步骤如下:

a.根据要求,列出真值表。

b.画出卡诺图,并按多输出逻辑函数化简,得到最简输出逻辑表达式。

c.画出译码器逻辑图。

三、所用仪器、材料(设备名称、型号、规格等)

TDN-CM或TDN-CM++教学实验设备一套

四、实验方法、步骤

实验步骤

(1)按图

1.3所示的实验接线图进行接线。

图1.3实验接线图

(2)打开电源开关。

(3)查看数码管的好坏。

(4)按如下步骤进行操作:

d.首先关闭所有的三态门(SW-B=1,LED-B=1),并将脉冲信号置为W/B(LED)=1。

e.用数据开关D3…D0置数,并观察相应数据显示灯变化

f.打开数据三态门(SW-B=0)。

g.打开LED片选(LED-B=0),拨动W/B(LED)做1→0→1动作,产

生一个下降沿脉冲将数据打入LED中,并观察七段LED数码管各段的变化。

h.对输入进行足够多的改变,并观察相应的输出变化,同时填写表1.1。

i.数码管在作几进制数的显示?

j.试用与非门自行设计一个能驱动该七段数码管的显示译码器(显示器为共阴极),给出设计步骤,画出逻辑图,并列出所用元器件清单。

五、实验过程原始记录(数据、图表、计算等)

六、实验结果、分析和结论

本次实验很成功,让我了解到数字逻辑电路的实际应用,了解数据输入输出。

理解数码显示译码器的作用。

学会使用数码管的检测极限是一码器的使用。

掌握七段显示译码器的设计。

会设置16进制译码器。

实验二、启停时序电路实验

一、实验目的

(1)加深理解启停电路的使用对脉冲信号进行有效的控制,以保证计算机可靠地启动和停机

(2)按对启停电路的要求,实现电路并通过分频组合所需的时标信号

二、实验原理及基本技术路线图(方框原理图)

时序电路单元(STATEUNIT)时序电路单元位于实验板的左上部,其电路分为四个部分:

消抖电路(KK1)、时序控制(TS1、TS2、TS3、TS4)、时钟信号源(Φ)和拨动二进制开关组(STOP、STEP),框图如图2.1所示。

图2.1时序电路单元

用户只需将信号单元(SIGNALUNIT)的输出端(H23)与Φ相连,然后按

动START(KK1)微动开关,根据STOP与STEP的状态,TS1-TS4将输出有规则的方波信号。

下面分别介绍各部分电路:

(1)单拍脉冲与消抖电路(图2.2所示)

在实验中,KK2一般用来作为单拍脉冲信号发生器。

START已将其输出接入

时序电路中的START处,作为时序电路的启动开关,因此,START一般作为启动时序电路的目的用。

图2.2单拍脉冲与消抖电路

(2)时序控制电路与拨动开关组

时序控制电路如图2.3所示,可产生四个等间隔的时序信号TS1-TS4。

图2.3时序控制电路

STEP(单步)与STOP(停机)分别来自实验板上部的两个二进制开关STEP与STOP的模拟信号。

启动时来自实验板“STATUNIT”单元的微动开关START的按键信号。

当STOP开关置为RUN状态时,STEP开关置为EXEC时,按下START微动开关后,时序信号TS1-TS4将周而复始地发送出去,产生的时序状态图如图2.4所示。

当STOP开关置为RUN状态时,而STEP开关置为STEP时,按下START微动开关后,机器处于单步运行状态,即此时在发送一个CPU周期的时序信后就停机。

利用单步方式,每次只产生一条微指令,因而可以观察微指令的代码与当前微指令的执行结果。

另外,当机器连续运行时,如果使STOP开关置为STOP时,会使机器停机,或将CLR开关执行1→0→1操作,也可以使时序清零。

时序电路的CLR已接至实验板右下方的CLR模拟开关上。

此时序控制电路是用一片复杂可编程逻辑器件(CPLD)芯片来实现。

该单元左侧的信号源可产生频率及脉宽可调的方波信号。

可根据实验需要自行选择方波信号的频率与脉宽。

经启停控制电路控制,产生受控的全机所需的节拍脉冲信号TS1-TS4。

图2.4时序状态图

(3)信号源

信号单元(SIGNALUNIT)位于“STATEUNIT”的左侧,其电路图如图2.5所示。

图中左侧为一个用555定时器构成的多谐振动器,它可自行产生有一定频率和脉宽的方波;图中右侧为一个属于TTL系列的74123可重复触发单稳态触发器,它可产生一定脉宽的方波。

可先调节电位器W1,使H23端输出用户期望频率的波形信号,频率的可调范围在30Hz-300Hz之间;然后,再调节电位器W2使H23端输出特定占空比的信号,共实验选择使用。

占空比为脉冲宽度与脉冲周期的比值。

图2.5信号源电路图

三、所用仪器、材料(设备名称、型号、规格等)

TDN-CM+或TDN-CM++教学实验设备一套

四、实验方法、步骤

实验步骤

(1)打开电源开关:

a.给出调节H23端方波信号频率的步骤,并观察记录结果。

b.给出调节H23端方波信号占空比的步骤,并观察记录结果。

(2)断开电源,将H23与Φ相连接,再重新打开电源:

a.给出产生启动信号的步骤,并观察记录结果。

b.给出产生停止信号的步骤,并观察记录结果。

c.给出产生单步运行的步骤,并观察记录结果。

d.给出产生连续运行的步骤,并观察记录结果。

e.在上述情形下,分别对TS1、TS2、TS3和TS4信号进行观测。

(3)分析讨论

五、实验过程原始记录(数据、图表、计算等)

(1)打开电源开关:

a.调节H23端方波信号频率的步骤是:

H23连LEDUNIT(C6,C7),观察记录结果是:

调节W1,W2保持;W1顺时针旋钮时,L6、L7渐暗,说明是低频。

W1逆时针旋钮时,L6、L7渐亮,说明是高频。

b.调节H23端方波信号占空比的步骤是:

同a。

观察记录结果是:

调节W2,W1保持;W2顺时针旋钮时,L6、L7闪动快,W2逆时针旋钮时,闪动慢。

(2)断开电源,将H23与Φ相连接,再重新打开电源:

a.产生启动信号的步骤是:

H23连φ,LEDUNIT(L6,L7)连TS1、TS2,STOP→RUN。

观察记录结果是:

灯亮,有信号。

b.产生停止信号的步骤是:

H23连φ,LEDUNIT(L6,L7)连TS1、TS2,STOP→STOP。

观察记录结果是:

灯灭,无信号。

c.产生单步运行的步骤是:

H23连φ,LEDUNIT(L6,L7)连TS1、TS2,STOP→RUN,STEP→STEP。

观察记录结果是:

亮一下。

d.产生连续运行的步骤是:

H23连φ,LEDUNIT(L6,L7)连TS1、TS2,STOP→RUN,STEP→EXEC。

观察记录结果是:

连续闪亮。

e.在上述情形下,对TS1、TS2信号进行了观测。

六、实验结果、分析和结论

通过本次实验,我加深理解启停电路的使用对脉冲信号进行有效的制,信号的启动和停止,实现电路并通过分频组合所需的时标信号。

实验三、总线传输实验

一、实验目的

(1)理解总线的概念及其特性。

(2)掌握总线传输控制特性。

二、实验原理及基本技术路线图(方框原理图)

总线传输实验框图如图5.4-1所示,它将几种不同的设备挂至总线上,有存储器、输入设备、输出设备、寄存器:

这些设备都需要有三态输出控制,按照传输要求恰当有序地控制它们,就可以实现总线信息传输。

图5.4-1总线传输实验框图

总线基本实验要求如下:

根据挂在总线上的几个基本部件,设计一个简单的流程:

(1)输入设备将一个数打入RO寄存器。

(2)输入设备将另一个数打入地址寄存器。

(3)将RO寄存器中的数写入到当前地址的存储器中。

(4)将当前地址的存储器中的数用LED数码管显示。

三、所用仪器、材料(设备名称、型号、规格等)

TDN-CM++教学实验系统一台

四、实验方法、步骤

(1)按照图5.4-2实验接线图进行连线。

(2)实验的具体操作步骤图如图5.4-3所示。

首先应关闭所有三态门(SW-B=1,CS=1,RO-B=1,LED-B=1),并将关联的信号置为LDAR=0,LDRO=0,WIR(RAM)=1,WIR(LED)=1。

然后参照如下操作流程,先给数据开关置数,打开数据输出三态门,拨动LDRO控制信号做0-1-0动作,产生一个上升沿将数据打入到RO中;然后继续给数据开关置数,拨动LDAR控制信号做0-1-0动作,产生一个上升沿将数据打入到AR中;关闭数据开关三态门,打开RO寄存器输出控关闭存储器片选,关闭RO寄存制,使存储器处于写状态(wlR=0、CS=0),将RO中的数写到存储器中;器输出,使存储器处于读状态(wlR士1CS),打开LED片选,拨动LED的控制信号做1-0-1动作,产生一个上升沿将数据打入到LED中。

五、实验过程原始记录(数据、图表、计算等)

实验步骤

INPUTDEVICE

上的指示灯

BUSUNIT

上的指示灯

EXTBUS

上的指示灯

OUTPUTUNIT

上的LED显示

注意其中‘0’代表灯亮,‘1’代表灯灭

灯号数

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

0

0

数据开关

0

1

1

0

0

0

1

1

1

1

1

1

1

1

1

1

0

1

0

0

0

0

0

0

0

0

三态门

0

1

1

0

0

0

1

1

0

1

1

0

0

1

1

0

1

0

0

0

0

0

0

0

0

打入寄存器

0

1

1

0

0

0

1

1

0

1

1

0

0

0

1

1

0

0

1

0

0

0

0

0

0

0

数据开关

0

0

1

0

0

0

0

0

0

0

1

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

打入寄存器

0

0

1

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

存储器打入到LED

0

0

1

0

0

0

0

0

1

1

0

0

0

0

1

1

0

0

1

0

0

0

0

0

0

0

三态门

0

0

1

0

0

0

0

0

0

1

1

0

0

0

1

1

0

0

1

0

0

0

0

0

0

0

写入存储器

0

0

1

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

1

0

0

0

0

0

0

0

三态门

0

1

1

0

0

0

1

1

1

1

1

1

1

1

1

1

0

1

0

0

0

0

0

0

6

3

六、实验结果、分析和结论

通过实验,明白多个功能部件共享的信息传输线称为总线。

掌握总线传输控制特性。

总线(Bus)是计算机各种功能部件之间传送信息的公共通信干线,它是由导线组成的传输线束,按照计算机所传输的信息种类,计算机的总线可以划分为数据总线、地址总线和控制总线,分别用来传输数据、数据地址和控制信号。

总线是一种内部结构,它是cpu、内存、输入、输出设备传递信息的公用通道,主机的各个部件通过总线相连接,外部设备通过相应的接口电路再与总线相连接,从而形成了计算机硬件系统。

在计算机系统中,各个部件之间传送信息的公共通路叫总线,微型计算机是以总线结构来连接各个功能部件的。

实验四、半导体静态存储器实验

一、实验目的

掌握静态随机存储器RAM工作特性及数据的读/写方法

二、实验原理及基本技术路线图(方框原理图)

实验所用的半导体静态存储器电路原理如图1所示,实验中的静态存储器由一片6116(2K×8)芯片构成,其数据线接至数据总线,地址线由地址锁存器(74LS273)给出。

地址灯AD0-AD7与地址线相连,显示地址状况。

数据开关经一个三态门(74LS245)连至数据总线,分时给出地址和数据。

因地址寄存器为8位,所以接入6116芯片的地址为A7-A0,而高3位A8-A10接地,所以其实际容量只有256字节,6116芯片有三个控制线:

CE(片选线)、OE(读线)、WE(写线)。

当片选有效时进行读操作,WE=0时进行写操作。

本实验中将OE常接地,在此情况下,当CE=0,OE=0时进行写操作。

本实验中将OE常接地,在此情况下,当CE=0,WE=0时进行读操作,CE=0,WE=1时进行写操作,其写时间与T3脉冲宽度一致。

实验时将T3脉冲接至实验板上时序电路模块的TS3相应插孔中,其脉冲宽度可调,其他电平控制信号由“SWITCHUNIT”单元的二进制开关模拟,其中SW-B为低位电平有效,LDAR为高电平有效。

三、所用仪器、材料(设备名称、型号、规格等)

TDN-CM++教学实验系统一台

四、实验方法、步骤

(1)形成时钟脉冲信号T3。

具体接线方法和操作步骤如下:

①接通电源,用示波器接到方波信号源的输出插孔H23调节电位器W1及W2,使H23端输出实验所期望的频率和占空比的方波。

②将时序电路模块(SuNTr)单元中的Φ和信号源单元(SIGNALuNIT)中H23

排针相连。

③在时序电路模块中有两个二进制开关“STOP”和“STEP”将“STOP”开关置为“RUN”状态、“STEP”开关置为“EXEC”状态时按动微动开关S则TS3端输出连续的方波信号,此时调节电位器W1,用示波器观察,使T3输出实验要求的脉冲信号。

当“STOP”开关置为“RUN”状态、“STBP”开关置为“STEP”状态时每按动一次微动开关ST.ART,则T3输出一个单脉冲,其脉冲宽度与连续方式相同。

用PC联机软件中的示波器功能也能看到波形。

这样可以代替真实示波器。

(2)按图3.6-2连接实验线路,仔细查线无误后接通电源。

图3.6-2静态随机存储器实验接线图

(3)写存储器。

给存储器的00、01、02、03、04地址单元中分别写入数据IIH、l2H、13H、14H、15H.由上面的存储器实验原理图(图3.6-2)看出,由于数据和地址全由一个数据开关给出,因此要分时地给出。

下面的写存储器要分两个步骤:

第一步写地址,先关掉存储器的片选(CE=1),打开地址锁存器门控信号(LDAR=1),打开数据开关三态门(SW-B=0),由开关给出要写入的存储单元的地址,按动START产生T3脉冲将地址打入到地址锁存器:

第二步写数据,关掉地址锁存器门控信号(LDAR=0),打开存储器片选,使之处于写状态(CE=0,WE=1),由开关给出此单元要写入的数据,按动START产生T3脉冲将数据写入到当前的地址单元中。

写其他单元依次循环上述步骤。

写存储器流程如图3.6-3所示(以向00号单元写入11H为例)。

(4)读存储器。

依次读出第00、01、02、03、04号单元中的内容,观察上述各单元中的内容是否与前面写入的一致。

同写操作类似,读每个单元也需要两步;第一步写地址,先关掉存储器的片选(CE=1),打开地址锁存器门控信号(LDAR=1),打开数据开关三态门(SW-B),由开关给出要写存储单元的地址,按动START产生T3脉冲将地址打入到地址锁存器;第二步读存储器,关掉地址锁存器门控信号(LDAR=0),关掉数据开关三态门(SW-B=1),片选存储器,使它处于读状态(CE=0,WE=0),此时数据总线上显示的数据即为从存储器当前地址中读出的数据内容。

读其他单元依次循环上述步骤。

读存储器操作流程如下图3.6-4所示(以从00号单元读出11H数据为例)。

五、实验过程原始记录(数据、图表、计算等)

单元号

单元灯信号显示(0表示灯亮,1表示灯灭)

1

2

3

4

5

6

7

8

00

0

0

0

1

0

0

0

1

01

0

0

0

1

0

0

1

0

02

0

0

0

1

0

0

1

1

03

0

0

0

1

0

1

0

0

04

0

0

0

1

0

1

0

1

写入第一个地址时,在输入单元给出二进制地址00000000,打开地址锁存器,便可把地址打入地址锁存器,地址灯显示为00000000,然后输入该单元存入的数据00010001(11H),总线数据显示灯应显示为00010001,打开存储器片选,使之处于写操作,这样11H便存入00号单元,依此类推,可将12H、13H、14H、15H分别存入01、02、03、04地址单元,地址灯和总线数据显示灯都分别显示出结果。

读存储器时,当用开关给出存储单元地址时,地址灯会显示,这时,打开存储器片选,使之处于读状态,此时数据总线上显示的数据即为从存储器当前地址中读出的数据内容。

六、实验结果、分析和结论

储器中最小的存储单位就是一个双稳态半导体电路或一个CMOS晶体管或磁性材料的存储元,它可存储一个二进制代码。

由若干个存储元组成一个存储单元,然后再由许多存储单元组成一个存储器。

一个存储器包含许多存储单元,每个存储单元可存放一个字节,每个存储单元的位置都有一个编号,即地址,一般用十六进制表示。

一个存储器中所有存储单元可存放数据的总和称为它的存储容量,给出地址指令,就可以将数据存入指定的地址单元。

实验五、算术逻辑运算

一、实验目的

(1)了解运算器的组成结构。

(2)掌握运算器的工作原理。

(3)学习运算器的设计方法。

(4)掌握简单运算器的数据传输通路。

(5)验证运算功能发生器74LSl8l的组合功能。

二、实验原理及基本技术路线图(方框原理图)

实验中所用的运算器数据通路图如图2.6-1所示。

图中所示的是由两片74LSl8l芯片以并/串形式构成的8位字长的运算器。

右方为低4位运算芯片,左方为高4位运算芯片低位芯片的进位输出端C(n+4)与高位芯片的进位输入端Cn相连,使低4位运算产生的进位送

进高4位运算中。

低位芯片的进位输入端Cn可与外来进位相连,高位芯片的进位输出引至外部。

两个芯片的控制端SO~S3和M各自相连,其控制电平由表2.6-1给出。

图2.6-1!

运算器通路图

并/串形式构成的8位字长的运算器。

右方为低4位运算芯片,左方为高4位运算芯片低

位芯片的进位输出端C(n+4)与高位芯片的进位输入端Cn相连,使低4位运算产生的进位送

进高4位运算中。

低位芯片的进位输入端Cn可与外来进位相连,高位芯片的进位输出引至

外部。

两个芯片的控制端SO~S3和M各自相连,其控制电平由表2.6-1给出。

表2.6-1

DR1

DR2

5352SlS0

M工0(算术运算)

M=1

(逻辑运算)

cn=1

无进位

cn=0

有进位

65

65

65

A7

A7

A7

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

F=(65)

F=(E7)

F=(7D)

F=()

F=()

F=()

F=()

F=()

F=()

F=()

F=()

F=()

F=()

F=()

F=()

F=()

F=(66)

F=(E8)

F=(7E)

F=()

F=()

F=()

F=()

F=()

F=()

F=()

F=()

F=()

F