数管板实施方案.docx

《数管板实施方案.docx》由会员分享,可在线阅读,更多相关《数管板实施方案.docx(15页珍藏版)》请在冰豆网上搜索。

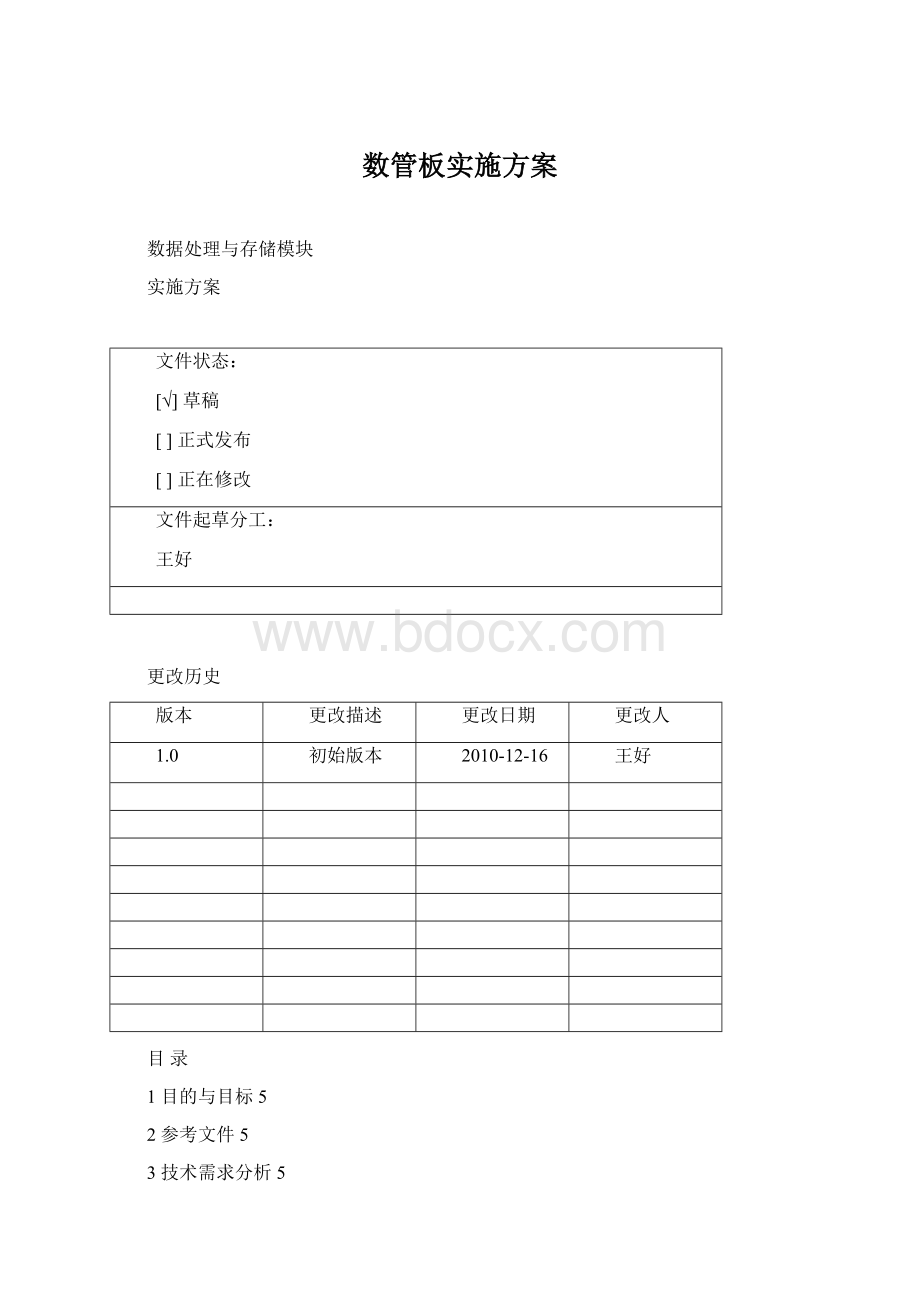

数管板实施方案

数据处理与存储模块

实施方案

文件状态:

[√]草稿

[]正式发布

[]正在修改

文件起草分工:

王好

更改历史

版本

更改描述

更改日期

更改人

1.0

初始版本

2010-12-16

王好

目录

1目的与目标5

2参考文件5

3技术需求分析5

4实现原理6

5工作流程6

6分模块实现说明6

6.1PCIe协议分析7

6.2RAID-SATA协议分析7

6.3RAID-SATA协议实现11

6.4PPC软件设计12

7系统性能评估12

7.1PCIe接口模块性能评估12

7.2RAID-SATA模块性能评估12

7.2.1DMAREAD状态机12

7.2.2性能计算14

7.3PPC软件性能评估16

1目的与目标

本文档用于描述数管板的需求、工作原理、工作流程及逻辑实施方案,供项目开发人员和软件开发人员参考。

2参考文件

a、SerialATAAHCI1.3Specification

b、SerialATASpecificationRev.3.0GoldRevision

c、Virtex-5FPGAUserGuide

d、Virtex-5FPGARocketIOGTXTransceiverUserGuide

e、EmbeddedProcessorBlockinVirtex-5FPGAsReferenceGuide

f、Virtex-5FPGAIntegratedEndpointBlockforPCIExpressDesignsUserGuide

3技术需求分析

数据处理与管理模块负责以下工作:

●通过两路PCIe×4接口,获取数据压缩板的数据;

●通过1394等主控接口,与主控模块进行控制命令及状态信息交互;

●通过1路PCIe×4接口,将实时回放数据传输至主控模块;

●完成对来自PCIe数据的缓存、打包、对回放数据的缓存、解包及合成等功能

●通过8路SATA与存储模块进行数据传输;

●负责建立存储数据的文件系统;

●完成其他主机对存储模块的指令操作。

主要的技术指标如下:

●两路PCIe×4接口,每路协议原始传输速率10Gbps,实际传输速率>500MB/s

●8路SATA3.0接口,每路协议原始传输速率3.0Gbps,需支持最大800MB/s传输速率;

●接收到主控模块的回放命令后,对存储模块中的数据进行检索、读取并传输至主控模块;

●实现RAID0、并以FAT32文件系统对数据进行存储管理,以保证存储模块可配合标准的商用RAID卡在地面工作环境中独立工作。

4实现概述

数据处理与管理模块的逻辑框图如图1所示。

图1逻辑框图

PCIE0为数据接收路径,与数据压缩板相连,PCIE1为数据回放路径,与主控板相连。

PCIE与用户应用层的接口,采用用Virtex5内部嵌入的Powerpc硬核提供的DMA通道,每通道为150MHz、32b的传输接口。

四通道SATA经RAID模块后,与SPLB0总线相连,SPLB总线可以提供100MHz、128b传输能力,并由RAID作为主控直接对内存进行操作,在数据传输过程中无需主机参与。

DDRSDRAM做为系统内存直接与嵌入式硬核的MCI接口相连,MCI接口提供高速的存储器接口。

当系统工作时,将数据从数据压缩板接收进来,并通过DMA通道放入内存中,传输达到一定数据量时,通知PPC440对数据进行操作:

即按AHCI协议进行构建FIS。

构建完FIS后,通知RAID模块由命令待执行。

RAID模块获取命令并分发至SATAHOSTIPCORE,由SATAHOSTIPCORE发送至SATA固态硬盘,随后收到SATA固态硬盘响应后,建立数据传输通道,进行数据传输。

当传输完成后,SATA固态硬盘上报状态信息,供PPC440处理。

RAID模块可在任务结束时提供一个中断信号,触发PPC440进行其他操作。

回放时,首先进行数据检索,并通过RAID模块启动数据读取操作,RAID模块分多次突发将数据存入内存,当任务结束,RAID模块触发PPC440进行回放数据操作,PPC440通知PCIE1将数据读走。

5分模块实现说明

5.1PCIe协议分析与实现

PCIE的协议包括为事务处理层、数据链路层和物理层。

PCIE以包(Packet)方式传输数据,事务处理层将事务包从用户逻辑(应用层)接收并传输至数据链路层,同时事务处理层进行流量控制,保证直到接收端准备好才会发起传输。

PCIE协议支持四种类型的传输Memory、I/O,Configuration,Message。

一个PCIE的Packet的定义如图2所示。

图2Packet定义

数据链路层负责链路管理、数据误码检测及纠正。

同时,也产生一些特殊的Packets,如响应包(ACK/NAK)、流量控制和功耗管理等。

物理层包括包(Packet)组帧与解帧、通道映射、通道间去偏移、数据包加解扰、检查特殊数据包序列,

数据处理与管理板的Virtex5FX70T内部嵌入了多路PCIE硬核,可以方便地实现PCIE接口。

其框图如图3所示。

图3Virtex5PCIE框图

5.2RAID-SATA协议分析

SATA协议基于ATA协议,以一种串行的传输接口替代PATA传输接口,来达到高速数据传输。

SATA协议包括四层结构:

即应用层、传输层、链路层和物理层。

图4SATA协议结构

应用层负责整个ATA命令的执行及控制命令寄存器获取。

传输层负责:

●根据FIS类型及格式,构造FIS,在接收时解析并得到有用信息,将其传输到指定位置;

●通知链路层传输一帧,获取链路层传来的接收一帧确认信息;

●对FIFO进行流量管理,通知链路层进行流量控制;

●将链路层传输的接收状态信息传输至应用层;

链路层负责:

●与对等链路层协商传输一帧信息,对出现的主设备与从设备的请求冲突进行判决;

●响应对等链路层并接收数据;

●对传输层送来的数据进行封装,如加入SOF、CRC、EOF等原语;

●以Dwords形式读接收传输层送来的数据,并计算CRC,对收到的FIS进行CRC校验;

●传输帧至物理层;

●响应传输层的FIFO或对等链路层的请求并提供控制原语;

●接收对等链路层送来的响应信息;

●向传输层提供传输状态;

●8b/10b的编码解码,同时提供加扰与解扰功能;

物理层负责将链路层送来的数据以串行数据形式送至对等物理层,以及将收到的数据送至链路层。

对于FIS,SATA协议中有如表1定义:

表1FIS类型

对于每一种FIS的格式,在SATA3.0协议中格式都有详细的定义。

在数据处理与管理板中,我们采用了具有更高性能的AHCI模式来完成主机软件与SATA设备之间的通信。

AHCI(AdvancedHostControllerInterface)接口协议由Intel等公司共同制定的一种软件与SATA设备之间通信的硬件机制,其本质是一类PCI设备,负责在系统内存总线与SATA设备之间扮演一种通用接口,保证了在不同操作系统和硬件平台中都能通用。

AHCI协议定义了一个包含控制及状态区域、命令序列入口表的通用系统内存结构,每个命令表入口包括了SATA设备的编程信息和一个指向描述表的指针。

采用AHCI接口协议,HBA(HostBusAdapter)将相当于一个数据传输者,不需要去解析任何ATA命令,当SATA设备与系统内存需要数据交换时,HBA成为系统内存的主控单元,通过DMA进行传输。

AHCI协议为HBA定义了如下地址映射结构:

图5AHCI寄存器与地址映射关系表

AHCI基本的工作流程,以DMAREAD为例描述如下:

1)主机根据HBA状态,将数据构建为DATAFIS,且构建CommandFIS;

2)主机通知HBA有可执行的CommandFIS;

3)HBA成为系统内存主控,并读取Command0,并以Command0所定义的地址信息到内存中获取CommandFIS;

4)HBA将CommandFIS送至链路层,并由链路层组织发送出去;

5)如果是DMAREAD命令时,SATA设备将响应此命令,将数据发送至HBA的端口上,由HBA链路层接收并缓存至内部FIFO中;

6)HBA传输层请求HBA对数据进行操作,HBA申请对系统内存的控制权;

7)HBA到内存的地址中读取PRD,建立DMA通道,并开始数据传输,将DATAFIS送至系统内存中,当一个DATAFIS结束时,如果没有满足该PRD的定义长度,则继续传输下一个DATAFIS,直至满足PRD;

8)当前PRD传输结束,SATA设备则传输D2HRegisterFIS,链路层接收到后,HBA请求总线,将D2HRegisterFIS写入系统内存,地址由HBA的寄存PxFB、PxFBU定义

9)如果有多个PRD,则重复进行7)操作;

10)如果有多个Command要执行,则主机可以多次触发HBA;

另外,AHCI还定义了对SATA3.0的PortMultiplier以及NCQ的功能的支持。

NCQ在机械硬盘中的工作原理是:

机械硬盘的随机读写时,磁头需要频繁的换磁道,对于系统存取性能影响很大。

NCQ功能可以对命令进行排序,将相邻的磁道操作排在一起。

而对于固态硬盘由于不存储机械部件,因此不需要考虑此问题,在固态硬盘的存储系统中,NCQ可以在固态硬盘控制器支持的情况下,对命令进行排队,类似于流水操作。

因此,在数据处理与管理板的设计中,将考虑支持此项功能。

数据处理与管理板实现RAID0工作模式。

RAID0工作原理可以用如图4所示来描述。

图6RAID工作原理

RAID0通过多路并行实现高速数据传输与存储。

5.3RAID-SATA协议实现

在数据处理与管理板上,共有8路SATA接口,对应8路SATA固态硬盘。

板上的两片Virtex5FX70T芯片嵌入了PPC440CPU,提供基于Vxworks的软件环境,与之对应的SATA主接口,采用AHCI接口协议,其相关协议及功能的实现由FPGA硬件及逻辑资源来实现。

数据处理与管理板的RAID-SATA协议实现的基本框架如下所示。

SATAIP需要与主机内存进行数据交互。

RAID模块需要完成总线协议的转换、RAID协议、同样要实现对SATA协议的解析、FIS的分解与构建等功能。

由于SATAAHCIIP的独立性,RAID与IP的接口需要完全遵守AHCI协议,并且不同IP与同一IP的不同端口之间的操作存在先后关系,RAID模块需要保证数据的顺序不能混乱。

RAID模块应包括以下模块:

1)PLBMASTER

与PLB总线的接口。

负责到主机内存获取DATAFIS、CommandFIS及写DATAFIS。

2)Regs

实现AHCI协议的必需的寄存器组,PPC440通过DCR接口来设置和读取。

3)RAIDDMA

启动DMA操作,控制数据传输。

4)RAIDPACK/DISPACK

对从主机方向获取的FIS进行解包,并重新组包,写入DUALRAM中。

对从SATA设备而来的FIS,进行解析,如果是DATAFIS则重新组包,如果是其他FIS,根据主机是否需要此信息决定是否传输至主机及传输的格式(传给主机的FIS格式怎么定义能反应四通道的SATA状态?

)

5)Buffer0/Buffer1

缓存FIS,跨时钟域的交换。

6)AHBBUSARBITER

对AHB设备进行判决。

需要考虑如何保证数据以RAID0格式进行存取。

7)AHBMASTER

对SATAAHCIIP进行寄存器操作。

8)AHBSLAVE

响应SATAAHCIIP的Master接口,从Buffer中读取FIS或FIS写入Buffer。

5.4PPC软件设计

6系统性能评估

6.1PCIe接口模块性能评估

6.2RAID-SATA模块性能评估

下面以DMARead作为例子,分析RAID-SATA模块的工作状态图并评估其性能。

6.2.1DMAREAD状态机

t1:

PCIEDMA结束

t2:

CPU构建CommandFIS

t3:

CPU设置寄存器通知HBA:

t4:

HBA读取CommandHeader,然后读取CommandHeader所映射的CommandFIS,在HBA内部,由PackDispack模块解析CommandFIS,并构建新的CommandFIS,即建立4个CommandFIS对应4个SATADevice。

至少需20*4Bytes。

并将其写入Buffer。

HBA内部Manager逻辑,将按IP0_port0、IP1_port0、IP0_port1、IP1_port1顺序通知IP,有Command可执行,分别对应SATADevice0、SATADevice2、SATADevice1、SATADevice3。

t5:

IP0_port0、IP0_port1、IP1_port0、IP1_port1分别提出DMA请求,希望读取各自的CommandHeader,IP0_port0、IP1_port0被赋予总线使用权。

IP0_port0、IP1_port0读取CommandHeader,按照CommandHeader中定义的地址去读取CommandFIS。

同时将CommandFIS写入IP内部的TxBuffer中,并由IP的LINK层发送至SataDevice。

t6:

当IP0、IP1收到SataDevice0、SataDevice2的响应(R_OK )后,随后接收到SataDevice0、SataDevice2的数据,并将数据缓存至RxBuffer中。

在将CommandFIS发送至IP0_port0/IP1_port0的过程中,由于其已经释放AHB总线,则总线赋予IP0_port1/IP1_port1。

IP0_port1/IP1_port1开始读取CommandHeader、CommandFIS。

同时将CommandFIS写入IP0_port1/IP1_port1的TxBuffer中,由IP的LINK层负责将其发送至SataDevice。

而IP0_port0/IP1_port0此时的DMA请求将等到AHB总线释放后才能赋予。

t7:

IP0_port1/IP1_port1释放AHB总线后,AHB总线赋予IP0_port0/IP1_port0,IP0_port0/IP1_port0读取第一个PRD,并将RxBuffer中的数据经一次突发操作传输至Buffer0/Buffer1中。

由PRD最大为4MB。

如果PRD定义的数据量很大,则数据只缓存在FPGA内部的Buffer0/Buffer1中,显然是不可能的。

存入Buffer0/Buffer1的同时,由RAID/DMA模块将数据传输内存指定位置。

只要PLB总线速率远大于AHB总线速率,Buffer0、Buffer1就不会出现溢出的情况。

在此过程中,IP0_port1、IP1_port1收到SataDevice1、SataDevice3的响应(R_OK )后,随后接收到SataDevice1、SataDevice3的数据,,IP0_port1、IP1_port1的PDMA将数据缓存至RxBuffer中。

t8:

当IP0_port0/IP1_port0的一次数据传输结束后,释放AHB总线,判决器将其赋予IP0_port1/IP1_port1。

IP0_port1/IP1_port1读取第一个PRD,并将RxBuffer中的数据经一次突发操作传输至Buffer0/Buffer1中。

IP0_port1/IP1_port1释放AHB总线后,AHB总线赋予IP0_port0/IP1_port0,继续进行新的一次传输,将DATAFIS传输至Buffer0/Buffer1中。

在存入Buffer0/Buffer1的同时,由RAID/DMA模块将数据传输内存指定位置。

直到满足IP0_port0/IP1_port0、IP0_port1/IP1_port1的PRD的所定义的字节数,t8才退出。

因为读取的是RAID数据,因此设计时PRD定义的完全一样。

如果有多个PRD则回到t7,进行同样的数据传输操作。

如果IP0_port0/IP1_port0已经传输结束,则在IP0_port1/IP1_port1传输最后一个DATAFIS的过程中,SataDevice0、SataDevice2传输D2HRegisterFIS至IP0_port0/IP1_port0,暂存Rxbuffer中。

t9:

当IP0_port1/IP1_port1传输结束,AHB总线判决,并赋予IP0_port0/IP1_port0,用于传输D2HRegisterFIS。

由于IP0_port1/IP1_port1已经传输完毕,SataDevice1、SataDevice3传输D2HRegisterFIS至IP0_port1/IP1_port1,暂存Rxbuffer中。

t10:

AHB总线判决,并赋予IP0_port1/IP1_port1,用于传输D2HRegisterFIS。

t11:

如果需要中断,则HBA&RAID输出一个中断至CPU,HBA&RAID模块通过请求PLB总线将组合后的D2HRegisterFIS送至内存指定位置。

6.2.2性能计算

在传输状态机一节中所描述的t2、t3均为CPU软件指令,可以不计算在其中。

在设计时,PLB总线的工作时钟为100MHz,位宽128b,AHB总线的工作时钟定为150MHz,位宽32b。

PLB总线的峰值传输速率为1600MB/S,单路AHB总线的峰值传输速率为:

600MB/s,1600MB/s>1200MB/s,可以保证Buffer的数据不溢出。

t4:

PLB主控直接通过Crossbar的MCI来读取数据,以PLB总线时钟周期为单位,

t5:

包括tarb总线判决时间、IP到Buffer中读CommandFIS并写入Txbuffer的时间tcmd,AHB总线时钟周期为单位,以及Link层发送至Device的时间。

t6:

接收数据的时间或是t5,如果Rxbuffer足够大,则为接收数据的时间。

t7:

tarb总线判决时间、数据送至内存的时间tdata。

t8:

如果只有一个PRD,则t7工作一次,t8多次循环。

多个PRD,则t7、t8多次循环。

t9:

传输D2HRegisterFIS、tarb总线判决时间或接收D2HRegister时间。

t10:

tarb总线判决时间、传输D2HRegisterFIS时间

t11:

将D2HRegisterFIS传输至内存。

另外还有:

tIP:

IP内部的DMA控制器的本次突发结束到下一次突发开始的时间间隔,大概为15个AHB时钟周期。

平均传输速率:

传输数据量/传输时间

假设只有1个PRD,由于AHB总线限定突发数据量为1KB,对应1个DATAFIS为1KB。

在上述时间端中,主要的参数为t7、t8,会发生多次,而其他的则只发生一次。

在一次传输任务中,如果传输的数据量相对较大,则其它耗时参数对传输速率的影响可以暂时不考虑在内。

因此,对于1个64KB的传输任务,实际对每个通道是16KB。

其平均传输速率计算如下:

当tIP=15*TAHB、TARB=100*TAHB时,取fAHB=100MHz,tother忽略不计,则平均速率为:

=559MB/S

而实际上由于AHB总线的判决由硬件逻辑来做,可以做到20个AHB时钟周期,同时,AHB总线的时钟可以设置为200MHz或150MHz,则可以达到700MB/S以上。

以上推论,可能会因IP工作原理与上述假设不同而不成立。

因此需要对IP进行仿真和验证。

另外如果考虑系统构建FIS、到内存获取的时间等因素,当一次任务的传输数据量即PRD所定义的字节数足够大时,则性能会降低(数量级10MB/s),而如果PRD定义的字节数比较小,则其他耗时的影响会比较突出。

6.3PPC软件性能评估