数字电路实验报告资料.docx

《数字电路实验报告资料.docx》由会员分享,可在线阅读,更多相关《数字电路实验报告资料.docx(23页珍藏版)》请在冰豆网上搜索。

数字电路实验报告资料

数字电路实验报告

实验一组合逻辑电路分析

实验目的

1.熟悉基本逻辑电路的特点。

2.熟悉各类门的实物元件以及元件的使用和线路连接

3.学会分析电路功能。

实验原理

1.利用单刀双掷开关的双接点,分别连接高电平和低电平,开关的掷点不同,门电路输入的电平也不同。

2.门电路的输出端连接逻辑指示灯,灯亮则输出为高电平,灯灭则输出低电平

3.依次通过门电路的输入电平与输出电平,分析门电路的逻辑关系和实现的逻辑功能。

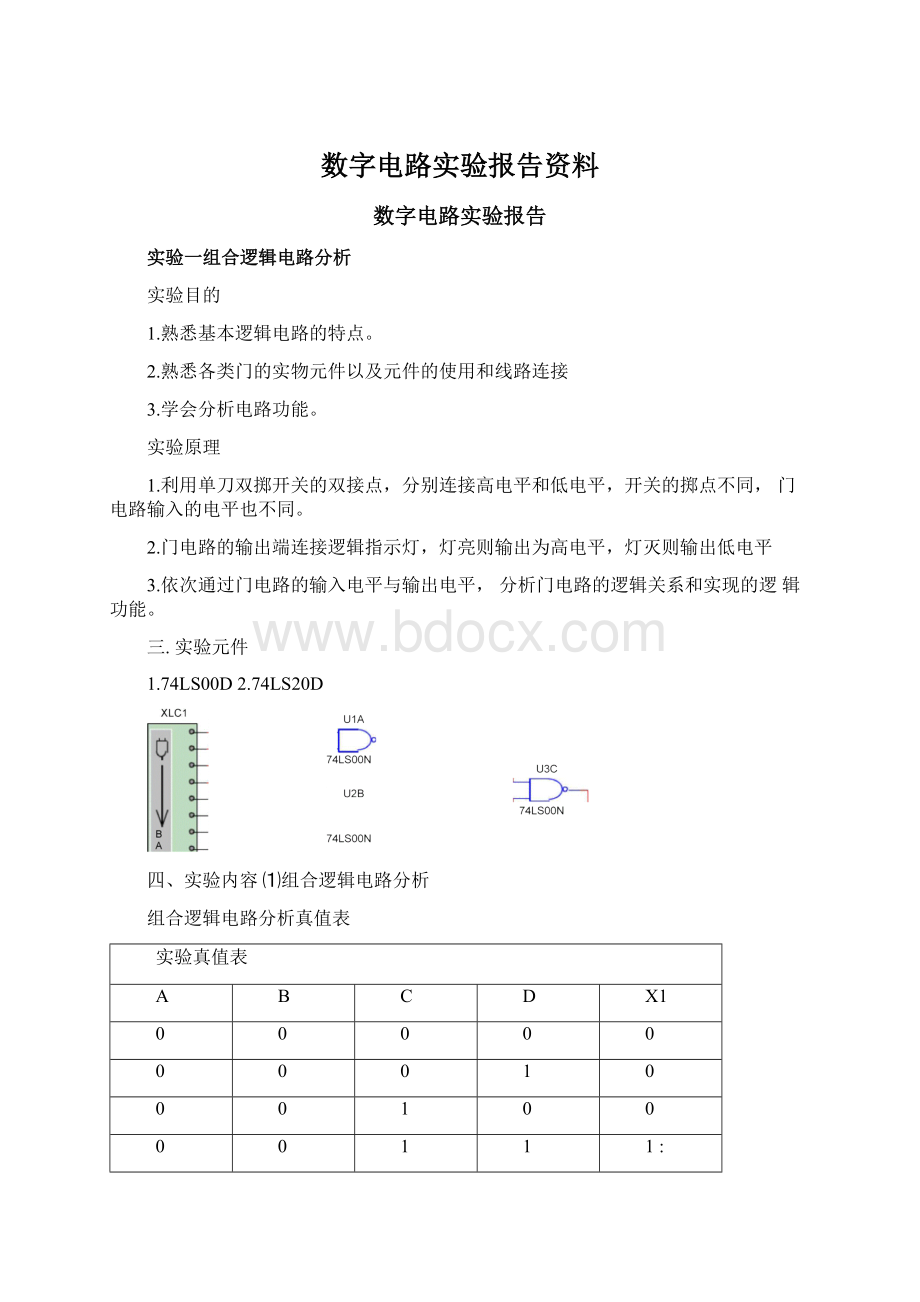

三.实验元件

1.74LS00D2.74LS20D

四、实验内容⑴组合逻辑电路分析

组合逻辑电路分析真值表

实验真值表

A

B

C

D

X1

0

0

0

0

0

0

0

0

1

0

0

0

1

0

0

0

0

1

1

1:

0

1

0

0

0

0

1

0

1

0

0

1

1

0

0

0

1

1

1

1

1

0

0

0

0

1

0

0

1

0

1

0

1

0

0「

1

0

1

1

1

1

1

0

0

1

1

1

0

1

1「

1

1

1

0

1

1

1

1

1

1

由实验逻辑电路图可知:

输出X1AB?

CDABCD,同样,由真值表也能推出此方程,说明此逻辑电路具有与或功能。

⑵密码锁问题

密码锁的开锁条件是:

拨对密码,钥匙插入锁眼将电源接通,当两个条件同时满足时,开锁信号为“1”,将锁打开。

否则,报警信号为“1”,则接通警铃。

试分析密码锁的密码ABCD是什么?

密码锁实验真值表

实验真值表

A

B

C

D

X1

X2

0

0

0

0

0

1

0

0

0

1

0

1

0

0

1

0

0

1

0

0

1

1

0

1

0

1

0

0

0

1

0

1

0

1

0

1

0

1

1

0

0

1

0

1

1

1

0

1

1

0

0

0

0

1

1

0

0

1

1

0

1

0

1

0

0

1

1

0

1

1

0

1

1

1

0

0

0

1

1

1

0

1

0

1

1

1

1

0

0

1

1

1

1

1

0

1

实验结果分析:

由真值表可知:

当ABCD为1001时,灯X1亮,灯X2灭;其他情况下,灯X1灭,灯X2亮。

由此可见,该密码锁的密码ABCD为1001。

因而,可以得到:

X1ABCD,X2X1。

实验二组合逻辑实验

(一)

半加器和全加器

一、实验目的

1.熟悉用门电路设计组合电路的原理和方法步骤。

二、预习内容

1.复习用门电路设计组合逻辑电路的原理和方法步骤。

2.复习二进制数的运算。

(1)用“与非”门设计半加器的逻辑图。

(2)完成用“异或”门、“与或非”门、“与非”门设计全加器的逻辑图。

(3)完成用“异或”门设计的3变量判奇电路的原理图。

二、参考兀件

1.74LS283(集成超前4位进位加法器)2.74LS00(四2输入与非门)

3.74LS51(双与或非门)4.74LS136(四2输入异或门)四、实验内容

ABj?

A?

Ab?

Bj

⑴用与非门组成半加器由理论课知识可知:

SiAiBiAjBiAiBi

CjAjBjAjBj

根据上式,设计如下电路图:

得到实验数据表格所得如下:

被加数A

0

1

0

1

加数Bi

0

0

1

1

和Si

0

1

1

0

新进位Ci

0

0

0

1

⑵用异或门、与或非门、与非门组成全加器由理论课知识可知:

S=ABiCi1

G=ABj(ABi)Cii

根据上式,设计如下电路:

实验数据表格所得如下:

⑶用异或门设计3变量判奇电路,要求变量中1的个数为奇数时,输出为1,否

则为0。

根据题目要求可知:

输出LABCABCABCABCABC,则

可以设计出如下电路:

U1A

VCC

VCC

5V

5V

R1

VCC

VCC

5V

5V

R1

1kQ

]R2

1kQ

R2

XLC1

U1A

74LS136D

r>

74LS136D

U2B

U2B

±E>

74LS136D

rr>

74LS136D

根据上图,可以得到如下实验数据表格:

输入A

0

0

0

0

1

1

1

1

输入B

c

1

1

0

1

r1

0

0

0

输入C

0

1

0

1

0

1

0

11

输出L

0

1

1

0

1

0

0

1

⑷“74LS283'全加器逻辑功能测试

当加数和被加数分别为0111和0001时

当加数和被加数分别为1001和0111时

利用74LS283进行如下表格中的测试:

被加数A4A3A2A1

0111

1001

加数B4B3B2B1

0001

0111

前级进位C

;0

0或1

0或1

和S4QS2S1

1000或1001

0000或0001

新进位C4

0或0

1或1

实验三组合逻辑实验

(二)

数据选择器和译码器的应用

一、实验目的

熟悉数据选择器和数据分配器的逻辑功能和掌握其使用方法。

预习内容

1.了解所用元器件的逻辑功能和管脚排列

2.复习有关数据选择器和译码器的内容

3.用八选一数据选择器产生逻辑函数LABCABCABCABC和

LABC

4.用3线-8线译码器和与非门构成一个全加器

二、参考兀件

四、实验内容

1.数据选择器的使用:

当使能端EN=O时,丫是A2、A、A和输入数据Do〜D7的与或函数,其表

7

达式为:

Ymj?

Dj。

式中mi是A?

、A、A构成的最小项,显然当Di=1时,

i0

其对应的最小项mi在与或表达式中出现。

当Di=0时,对应的最小项就不出现。

利用这一点,不难实现组合逻辑电路。

将数据选择器的地址信号A、A、Ao作为函数的输入变量,数据输入Do-D7作为控制信号,控制各个最小项在输出逻辑函数中是否出现,使能端EN始终保持低电平,这样,八选一的数据选择器就成为一个三变量的函数产生器。

①用八选一的数据选择器74LS151产生逻辑函数LABCABCABCABC

将上式写成如下形式:

L叶。

!

m3D3m6D6m7D7。

该式符合表达式1的标准

形式,显然D1、D3、D6、D7都应该等于1,而式中没有出现的最小项mo、m?

、m4、m5,它们的控制信号Do、D2、D4、D5都应该等于0,由此可画出该逻辑函数产生器的逻辑图:

VCC

5V

U1

经过实验验证,得到如下真值表:

A

B

C

L

0

0

0

0:

0

0

1

1

0

1

0

0

0

1

1

1

1

0

0

0

1

0

1

0

1

1

0

1

1

1

1

1

由实验所得真值表可知:

此逻辑电路能实现逻辑表达式

LABCABCABCABC的功能。

②用八选一的数据选择器74LS151产生逻辑函数LABC,根据上述原理自

行设计逻辑图,并验证实际结果。

LABC=m(1,2,4,7)

由以上最小项形式可以设计如下逻辑电路图:

VCC

5VU1

74LS151D

气了GND

实验测的真值表如下:

A

B

C

L

0

0

0

0

1

0

0

1

0

1

0

2

0

1

1

0

1

0

0

1

1

0

1

0

1

0

1

0

1

1

1

1

由真值表可看出,当A、B、C3个输入变量中1的个数为奇数时,输出为1,否则输出为0。

2.3线-8线译码器的应用

用3-8线译码器74LS138和与非门构成一个全加器,写出逻辑表达式并设计逻辑电路图。

验证实际结果。

全加器的和Si与新进位Ci的表达式如下:

S=ABiG1=ABCi1AjBiCi1ABiG1ABCi1=m(1,2,4,7)

Ci=AjBi(ABi)Ci1=ABCi1ABQi1ABiCi1ABCi1=m(3,5,6,7)

做出如下逻辑电路图:

5V

CO

XLC1

B

A

a

ABCG1

o1234567丫丫丫丫丫丫丫丫

21

Jgnd74LS138D

2.5V

U2A

n

74LS20D

U3B

74LS20D

通过实验得到如下真值表:

Ai

Ci-1

Si

Ci

DI

o:

0

0

0

0「

0

0

1

1

0

0

1

0

1

0

o:

1

r1

0

1「

1

1

0

0

0

1

0

1

0

1

1

1

0

0

1

1

1

1

1

1

通过真值表中的数据可以看出,按照上图的逻辑电路可以做成全加器。

3.扩展内容用一片74LS151构成四变量的判奇电路。

lABCdABcdAbCdAbcdabcdabcdabCdabcd

m0DgDm2Dm3DmuDm^Dm6Dm7D

画出如下电路图:

L

通过实验得到如下真值表:

A

B

C

D

L

0

0

:

0

0

0

0

0

0

1

1

0

0

1

0

1

0

0

1

1

0

0

1

P0

0

1

0

1

0

1

0

0

1

1

0

0

0

1

P1

1

r1:

1

0

0

0

1

1

0

0

1

0

1

0

P1

0

「0:

1

0

1

1

1

1

1

0

0

0

1

1

:

0

1

:

1

1

1

1

0

1

1

1

1

1

0

实验四触发器和计数器

1、实验目的

1.熟悉触发器的基本逻辑功能和原理

2.了解二进制计数器的工作原理

3.设计并验证十进制、六进制计数器

二、预习内容

1.复习有关R-S触发器,J-K触发器,D触发器的内容。

2.预习有关计数器的工作原理。

3.用J-K触发器组成三进制计数器,设计电路图。

4.

用74LS163和与非门组成四位二进制计数器,十进制计数器,六进制计数器设计电路图。

4.74LS63可预置四位二进制计数器(同步清零)四、实验内容

1.

RS触发器逻辑功能测试

用一块74LS00与非门构成R-S触发器,用万用表测量Q及Q的电位,并记

录于下表中:

R

S

Q

Q'

触发器电位

0

1

0

1

低电位

1

0

1

0

高电位

1

1

Q

Q'

保持

0

0

1

1

不确定

2.六进制计数器

U3

VCC

5V

U1

V1

A

QA

B

QB

C

QC

D

QD

ENP

RCO

ENT

LOADCLR

》CLK

15

3

4

5

6

7

10

14

13

12

11

―C

2

3.十进制计数器

VCC

5V

\^GND

74LS163D

DCD_HEX

U3

20H

5V

U1

QAQBQC

QD

3

4

5

6

14

13

12

11

DCDHEX

V1

◊gn

10

^^GND

4.六十进制计数器

ENP

ENT

RCO

15

LOADCLR

浄CLK

D74LS163D

U2A74LS00D

V1

50Hz

5V

VCC

DCD_HEX

5V

u

U1

DCDHEX

3

4

■6—

14

13

12

11

A

QA

B

QB

C

QC

D

QD

ENP

RCO

ENT

LOAD

CLR

》CLK

U3

15

2

呻74LS163D

9

1

7

10

U5A74LS00D

VCC

LOAD

CLR

CLK

74LS163D

U4

GND

5V3

5

7

ABCDO

QQQQC

R

P

NNABcDIEE

IU6B

74LS00D

U2

实验五数字电路综合实验

1、实验目的

1.学会计数器、译码器、显示器等器件的使用方法。

2.学会用它们组成具有计数、译码、显示等功能的综合电路,并了解它们的工作原理。

二、预习内容

1.复习有关计数器、译码器、寄存器、显示器的内容

2.熟悉有关元器件的管脚排列。

3.设计十进制计数译码显示电路。

画出电路器。

二、参考元件

译码器74LS248计数器74LS169共阴极七段显示器各一片

四、实验内容

1.

按自行设计电路图接线

2.合上电源。

当计数器预置初始状态“0000”后,将“置数”改为“1”态,由CP输入1HZ的连续方波。

检查输入脉冲与显示器上显示的十进制数字是否相符。

五、分析实验结果并讨论利用上述方法,能否扩大成0-99的计数、译码、显示电路?

计数器的进位如何实现?

答:

可以扩大成100进制的计数、译码显示电路,利用两块计数器、两块译码器和两个显示器,组合后就能有以上功能。

可以设计成如下电路:

期末考试数字秒表

一、实验目的

1.了解数字计时装置的基本工作原理和简单设计方法。

2.熟悉中规模集成器件和半导体显示器的使用。

3.了解简单数字装置的调试方法,验证所设计的数字秒表的功能。

二、预习内容

1.N进制计数器、一码显示电路的工作原理和设计方法。

2.所用器件的功能和外部引线排列。

二、参考兀件

集成元件:

555定时器一片,74LS248两片,74LS163两片,LED两片,74LS00两片。

二极管1N4148一个;电位器100k—个;电阻、电容若干。

四、设计内容及要求

1.

00~59

设计一个数字秒表电路,电路包含秒脉冲发生器、计数、译码,显示秒。

2.具有清零、停止、启动功能。

五、原理框图

数码显示电路

译码电路

秒计数器

控制电路

秒信号发生器

ENPENT

LOAD

CLR

RCO

六、实验原理图

U5

VCC

5V

5V

S1A

Key=Space

6

3A

9

Io

0

2

7

10

U4B74LS00D

S2B

Key

p?

GN

DCD_HEX

9

1

14

13

|!

―U9B

74LS00D

VCC

GND

A

QA

B

QB

C

QC

D

QD

ENP

RCO

ENT

LOAD

CLR

》CLK

74LS163D

74LS00D

7

10

U2

ABeD

ABCD

QQQQ

CLK

74LS163D

D

74LS00D

8B

U7A

74LS00D

U6

DCD_HEX