RS触发器的设计1.docx

《RS触发器的设计1.docx》由会员分享,可在线阅读,更多相关《RS触发器的设计1.docx(13页珍藏版)》请在冰豆网上搜索。

RS触发器的设计1

一、功能描述

1.RS触发器有两个稳定状态,Qn为触发器的原状态,Qn+1为触发器的次态,R为置0端,S为置1端.

2.基本RS触发器具有置位、复位和保持(记忆)的功能;

3.基本RS触发器的触发信号是低电平有效,属于电平触发方式;

4.基本RS触发器存在约束条件(R+S=1),由于两个与非门的延迟时间无法确定;当R=S=0时,将导致下一状态的不确定。

5.当输入信号发生变化时,输出即刻就会发生相应的变化,即抗干扰性能较差。

同步RS触发器(时钟脉冲控制的RS触发器)

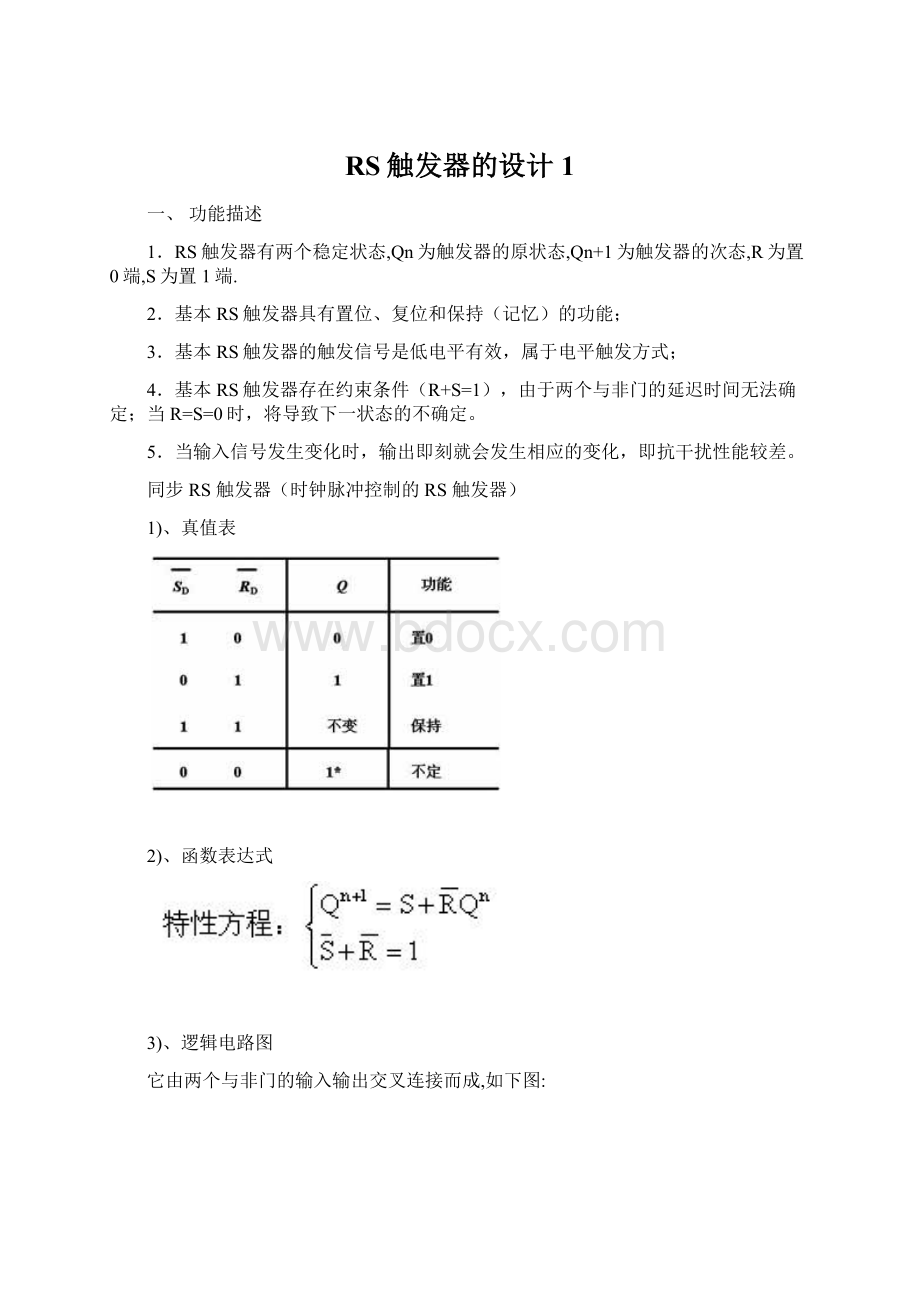

1)、真值表

2)、函数表达式

3)、逻辑电路图

它由两个与非门的输入输出交叉连接而成,如下图:

二、详细设计

1、打开QuartusⅡ软件,建立一个新的工程:

1)单击菜单File\NewProjectWizard..

2)输入工程的路径、工程名以及顶层实体名。

3)单击Next>按钮,本实验没有包含已有文件,单击Next>按钮。

4)设置我们的器件信息。

5)单击Next>

2、建立VHDL文件:

1)单击File\New菜单项,选择弹出窗口中的VHDLFile项,单击OK按钮以建立打开空的VHDL文件。

2)在编辑窗口输入VHDL源文件并保存实体名,文件名必须和保存的顶层实体名必须一致。

3)编译工程单击Processing/StartCompliation开始编译,编译过程可能出现若干错误信息,参考提示原因改正程序直到完全正确能够进行编译为止。

3、建立矢量波形文件

1)单击File/New命令,在弹出的窗口中找到otherfile中的VactoeWaveformFile项打开矢量波形窗口。

2)双击窗口左边的空白区域,单击Edit/EndTime设置时钟频率,单击Edit/InsertNodeandBus对话框。

3)单击NodeFinder按钮,打开以下对话框,选择Filter下列表中的Pins:

all,并点击List按照以下列出的所有端口,通过>>按钮把这些端口加入到右面的窗口中,单击OK完成端口的添加

4)回到波形编辑窗口,对所有输入端口设置输入波形,具体可以通过左边的工具栏,

或通过对信号的单击鼠标哟见的弹出式菜单中完成操作,最后保存次波形文件。

4、进行功能仿真

1)单击Assignments\Settings..,在弹出对话框将Simiulationmode设置为Functional,即功能仿真。

指定仿真波形文件后单击OK完成设置。

2)单击Processing\GenetateFunctionalSimulationNetlist以获得功能仿真网络表。

3)单击Processing\StartSimulation进入仿真页面。

5、进入时序仿真

如果功能仿真无误,可以进入时序仿真,时序仿真是增加了相关延迟的仿真,是最接近实际情况的仿真。

1)单击Assignments\Settings,在弹出对话框中将Simulationmode设置为Timeing即时仿真。

指定仿真波形文件后单击OK完成设置。

2)单击Processing\StartSimulation进入到仿真界面。

6、器件的下载

指定器件引脚:

1)单击Assignments\AssingnmentsPlns为每一个引脚赋值。

2)赋值后,重新编绎,形成编程文件。

3)编程器件通过电缆与电脑相连,进行下载到芯片。

按照VHDL语言开发流程写出整个开发过程,可以根据如下步骤适当导出程序,程序界面截图到课程设计报告对应模块。

1新建工程,工程管理:

2.源文件输入--------VHDL程序或原理图的设计,Alter内嵌模块的调用(对CPLD而言,只有MAXII还有内嵌模块可以调用)

3.综合,编译------检查语法错误,连接错误,生成综合后网表:

4.功能仿真----综合后的功能仿真,简单的管脚分配,I/O特性约束,简单的时序约束。

三、调试分析以及设计体会

1)仿真

1.准备网表文件及测试向量文件

2.指定模拟终止时间:

3.引入欲观察的结点:

4.在结点查找器中寻找结点:

5.编辑输入激励波形信号:

6.执行模拟:

2)设计过程中遇到的问题以及解决问题的方法。

在设计过程中,出现的问题有:

1.对VHDL编程语言不熟及quartusII软件不熟,对编程下载到芯片感到陌生。

经过老师的指教,及同学的帮助,渐渐地能够运用起来了

2.那个源程序出了出现了三个错误及15个警告,从头来过后,发现是顶层文件名与编程名不同,

3)课程设计过程经验教训、心得体会。

数电课程设计是培养学生综合运用所学知识,发现,提出,分析和解决实际问题,锻炼实践能力的重要环节,是对学生实际工作能力的具体训练和考察过程.回顾起此次课程设计,至今我仍感慨颇多,的确,在短短的一个星期的日子里,可以说得是苦多于甜,但是可以学到很多很多的的东西,同时不仅可以巩固了以前所学过的知识,而且学到了很多在书本上所没有学到过的知识。

通过这次数电课程设计使我懂得了理论与实际相结合是很重要的,只有理论知识是远远不够的,只有把所学的理论知识与实践相结合起来,从理论中得出结论,从而提高自己的实际动手能力和独立思考的能力。

在设计的过程中遇到问题,可以说得是困难重重,这毕竟第一次做数电课程设计,难免会遇到过各种各样的问题,同时在设计的过程中发现了自己的不足之处,对以前所学过的知识理解得不够深刻,掌握得不够牢固。

这次数电课程设计终于顺利完成了,在设计中遇到了很多问题,最后在老师的辛勤指导下,终于游逆而解。

同时,在刘老师的身上我学得到很多实用的知识。

总体来说,这次实习我受益匪浅.在摸索该如何设计程序使之实现所需功能的过程中,特别有趣,培养了我的设计思维,增加了实际操作能力.在让我体会到了设计的艰辛的同时,更让我体会到成功的喜悦和快乐.这次数电课程设计,虽然短暂但是让我得到多方面的提高:

提高了我们的逻辑思维能力,使我们在逻辑电路的分析与设计上有了很大的进步。

加深了我们对组合逻辑电路与时序逻辑电路的认识,进一步增进了对一些常见逻辑器件的了解。

另外,我们还更加充分的认识到,数字电路这门课程在科学发展中的至关重要性;查阅参考书的独立思考的能力以及培养非常重要,我们在设计电路时,遇到很多不理解的东西,有的我们通过查阅参考书弄明白,有的通过网络查到;相互讨论共同研究也是很重要的。