单晶片微处理机系统.docx

《单晶片微处理机系统.docx》由会员分享,可在线阅读,更多相关《单晶片微处理机系统.docx(16页珍藏版)》请在冰豆网上搜索。

单晶片微处理机系统

第十一章單晶片微處理器

什麼是單晶片微處理器主要義涵?

將微處理機系統搭配簡單周邊模組與輸出入介面以單晶片型態完成。

也就是說,單晶片微處理器中包含系統運作所需之周邊模組與模組驅動程式、系統程式與應用程式。

國內外有許多晶片公司,分別針對不同應用,設計有許多種單晶片微處理機系列,如:

8051、PIC、ARM、…等等。

因此本單元並不打算針對某系列之單晶片說明,而是希望以概念性之架構,由單晶模組之組成架構、模組應用與控制概念、單晶片系統設計發展切入說明,並提供一系統學習之流程,使入門者對單晶片系統有一全面性瞭解。

本章首先介紹單晶系統之應用與功能需求。

進一步說明常見之單晶片系統周邊模組功能與控制方式介紹,最後簡介單晶系統設計流程與單晶片系統學習方案建議。

11.1.單晶片微處理器之應用與功能需求

單晶片微處理機系統之應用與功能需求為何?

目前各類之電子與家電產品,皆可看到單晶片微處理機之蹤跡。

如:

電子表、微電腦控制洗衣機、防盜器、溫度控制器、電子耳溫槍、….等等。

舉凡對現實環境之量測、監控與互動裝置皆可看到單晶片系統之蹤影。

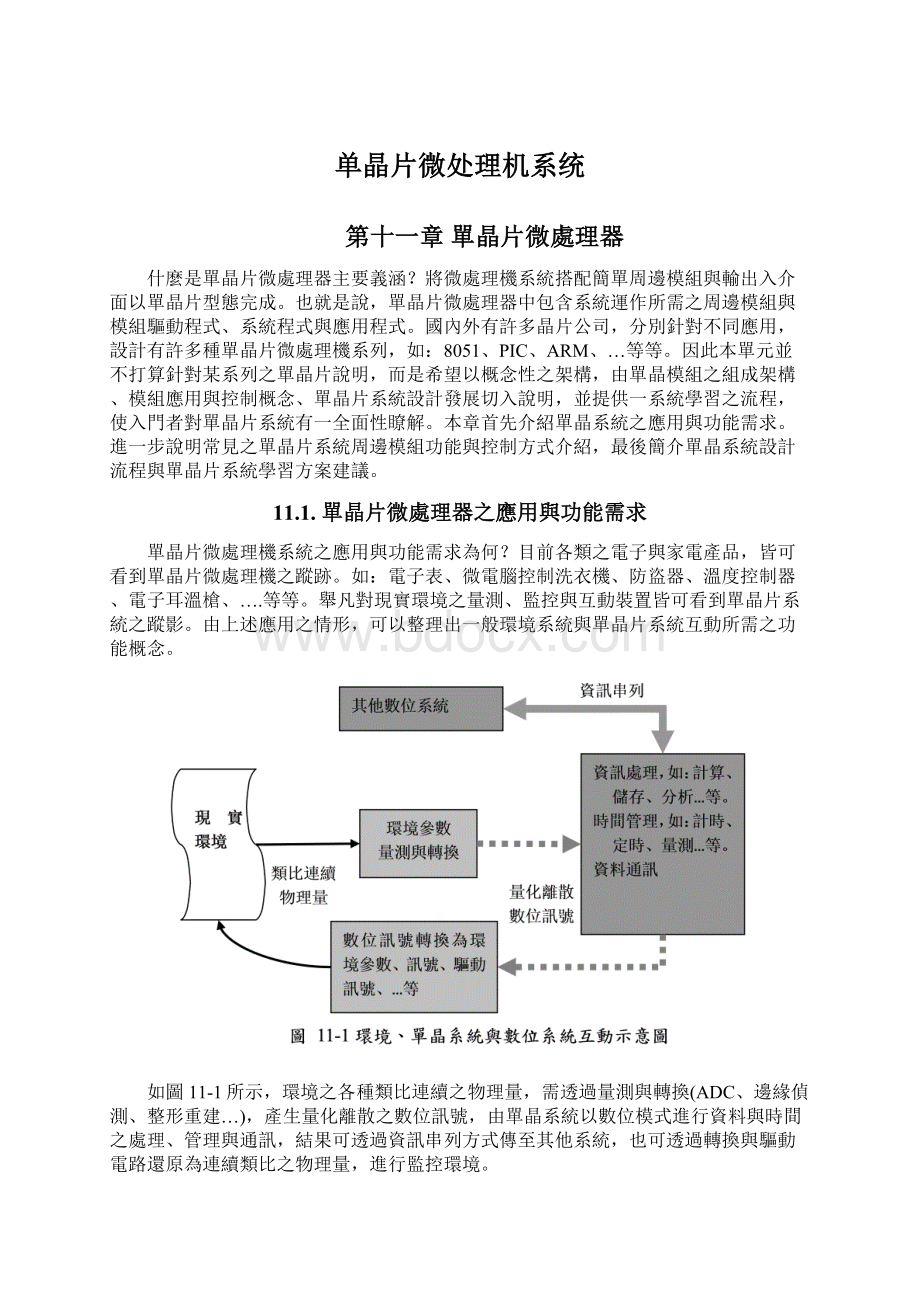

由上述應用之情形,可以整理出一般環境系統與單晶片系統互動所需之功能概念。

如圖11-1所示,環境之各種類比連續之物理量,需透過量測與轉換(ADC、邊緣偵測、整形重建…),產生量化離散之數位訊號,由單晶系統以數位模式進行資料與時間之處理、管理與通訊,結果可透過資訊串列方式傳至其他系統,也可透過轉換與驅動電路還原為連續類比之物理量,進行監控環境。

11.2.單晶片微處理機之功能模組

單晶片微處理機常見之功能模組有:

CPU核心、RAM與EEPROM/FlashROM、監督單元、時脈產生器等組成單晶系統之控制中樞,及因應不同之使用與設計目的,搭配各種周邊應用模組,如:

計時/計數器、基本I/O埠、串列傳輸、ADC/DAC、PWM、audio、RF….等等。

一般單晶片微處理機之架構如圖11-2;

以MICROCHIP公司所設計之PIC16F877為例,包含8資料位元之CPU核心、4KbyteEEPROM與8Kword(14bit)FlashROM、Monitor、三組獨立運作之計時器(timer0,timer1,timer2)、捕抓比較脈波寬調變模組(CCP)、10-bit數位類比轉換器ADC、五組基本輸出入埠(可提供並列I/O埠功能)、串列傳輸埠(SeriesI/O),幾乎所有模組功能皆具備。

11.2.1.中央處理單元(CPU)核心:

單晶片微處理機系統具備一運算與控制單元稱中央處理單元(CPU),一般依運算處理位元數,區分為8-位元、16-位元、32-位元之CPU核心。

常見之CPU核心為8-位元,如:

8051、PIC16系列、…等等。

CPU核心由暫存器、算數與邏輯運算單元與控制單元、指令解碼器與指令集所組成。

根據指令集之設計技術,可分為複雜指令集(CISC)與精簡指令集(RISC)核心。

複雜指令集(CISC):

指令之機械碼特徵有,指令數目多(數百個以上)、多字元組指令、指令週期長、指令功能強、運算元定址模模式多。

精簡指令集(RISC):

指令之機械碼特徵有,指令數目少(數十,一般約50個指令左右)、以單字元組指令為主(一個指令只需一字元,適合使用管線化pipeline加速技術)、指令週期短,但指令功能較弱(僅基本之運算與控制功能)、運算元定址模模式少。

然因核心架構簡單,為目前單晶微處理機CPU核心之設計主流。

11.2.2.隨機記憶體與可讀寫式唯讀記憶體

隨機存取記憶體(RAM)供CPU核心儲存各類資料,可讀寫式唯讀記憶體。

(EEPROM/FlashROM)供存放程式或永久性資料,一般可透過線上寫入之動作做修改。

由於單晶系統之指令位元數有限,一般記憶體系統可能採用分頁技巧或暫存器定址模式,以便節省運算元之定址位元。

11.2.3.監督單元(monitorunit):

由於對系統穩定性與多元應用之需求,單晶片微處理器皆設計監督單元,負責執行監督與管理系統,如:

系統重置(Reset)、電源啟動(Powerup)、電源耗弱(Brownout)、睡眠模式(Sleepmode)、看門狗(Watchdogs)、中斷控制器(Interruptcontrol)等功能。

系統重置(Reset):

系統重置狀態,可分成熱機重置(hotreset)與冷機重置(coldreset)。

冷機重置(coldreset)指的是電源剛啟動之重置動作,此時單晶系統內之記憶體與暫存器皆處於未使用狀態,其內容為隨機之數值(不可預測),此時需要設定適當之初值,給所有可能使用到之記憶體與周邊模組暫存器,避免不正常之誤動作產生。

熱機重置(hotreset)指的是正常使用中,因各種異常訊號或使用者設定,產生系統重置情況,此時單晶片系統內之記憶體與暫存器皆已設定資料,因此需根據重置之情形,設定相關記憶體與暫存器之初值,避免遺失已處理過之資料。

電源啟動(Powerup):

由於電源啟動需要一段時間,系統中各模組電路開始工作之電壓不同。

因此,在啟動時期電路會產生不同步運作。

然而,模組間訊號不同步,常會造成系統誤動作。

因此,單晶系統使用電源啟動(Powerup)控制程序或POWERONreset,使CPU核心於電源穩定後,同步重置後才開始運作。

其監督電源之概念如圖11-3。

電源耗弱(Brownout):

系統運作時電源也可能受各種因素干擾,如:

電源耗盡、脈衝式負載、電源接地干擾造成電源品質不佳(如圖11-4),導致系統誤動作或當機。

若可提早偵測出電源耗弱之狀況,並加以適當處理,可提高系統穩定度。

處理偵測電源耗弱現象之技術,常使用門限電壓偵測法。

當監控到電源低於設定之門限電壓,並超過設定之容許時間,監督單元會產生電源耗弱訊號,如圖11-5。

CPU將根據目前設定判斷是否產生電源耗弱之重置。

睡眠模式(Sleepmode):

一般系統使用時,並非以持續使用模式運作,因此為了節能與效率,單晶系統設計睡眠模式或省電模式。

如此,便可在非使用時期停止系統運作或降低運作之功率,達成節能與延長操作時間的目的。

因此,設計有睡眠模式之控制,包含設定與喚醒之機制。

看門狗計時器(Watchdogstimer):

單晶系統之運作環境,較一般電腦設備惡劣。

外界之雜訊干擾或環境變化,可能導致系統當機。

為預防長時間當機之事件發生,單晶片微處理機提供看門狗計時器(Watchdogstimer),定時檢視系統是否正常,或將系統由睡眠模式喚醒。

因此,即使系統發生當機問題,也可於一段時間後自動重置系統。

看門狗計時器之基本操作模式,啟動看門狗計時器後,固定時間內需重置看門狗計時器,否則在產生計時器溢位後,系統將自動重置。

此機制也用於喚醒睡眠中之系統,當系統進入睡眠模式,計時器溢位後,喚醒系統。

中斷控制器(Interruptcontrol):

由於各類周邊模組資料處理速率不同,資料輸出入事件隨機發生。

因應此狀況,周邊模組提供中斷控制模式。

因此,需透過中斷控制器整合與管理各模組之中斷訊號。

管理功能包括中斷向量、中斷致能與遮罩、中斷優先權、中斷旗標等。

中斷向量:

發生中斷時,CPU需執行之中斷服務程式所在之位址。

單晶片微處理機一般使用固定向量模式。

也就是說,各種周邊之中斷服務程式所在位址,記錄於固定位址。

CPU依所發生之中斷至對應位址讀取中斷服務程式所在位址,自動執行中斷服務程式。

中斷致能與遮罩:

各周邊模組之中斷功能可透過中斷控制器加以致能(使周邊產生中斷)、遮罩(使周邊無法產生中斷)。

此功能主要是避免未使用之模組產生中斷,或於中斷服務程式中再度被中斷。

中斷優先權:

當有不同周邊產生中斷訊號時,依中斷優先權執行對應之中斷服務程式。

優先權高之中斷將優先執行,優先權高之中斷訊號,可中斷優先權低之服務程式。

中斷旗標:

當有周邊產生中斷訊號時,同時會設定周邊模組之中斷旗標,供CPU辨識中斷來源。

當中斷旗標設定時,CPU將進入中斷模式,並執行中斷程序。

只要中斷旗標設定CPU會不斷進入中斷程序,因此中斷服務若確定已處理完畢,一定要清除對應之中斷旗標,避免CPU進入無窮盡之中斷程序。

有些CPU之中斷旗標會設定為硬體自動清除大部份無,因此最好查詢CPU之datasheet確認之。

11.2.4.時脈產生器(Timinggenerate)

數位系統運作需要有一基本之系統時脈。

並以此為基礎訊號,乘除某些數值,以便得到各周邊模組所需之工作時脈。

在單晶系統中常以簡單之振盪晶體或RC振盪電路(圖11-6)產生基本時脈(fHz)訊號。

若要產生更高之系統時脈,可應用鎖相迴路(phaselockloop,PLL)時脈合成器,產生N倍頻之系統時脈。

若要產生較低之時脈,可經由計數器除頻,產1/M倍頻之系統時脈。

除頻計數器:

除頻計數器由一組計數器與比較器構成,如圖11-7。

基本時脈(clock)觸發計數器上數,當比較器得到相等結果時,輸出除頻結果並重置計時器。

如此,將對輸入時脈進行除頻動作,得到較低之系統時脈。

鎖相迴路(PLL)之時脈合成器:

單晶之系統時脈,常因各種原因改變,如:

節省功率(低速率省功率)。

固定之晶體振盪電路無法達成需求。

因此,單晶片系統使用鎖相迴路時脈合成器合成所需之各種時脈。

應用固定之振盪頻率(Fosc),配合電壓控制振盪器、除頻電路(N)、相位偵測器與迴路濾波器,合成各種符合需求之系統時脈。

鎖相迴路(PLL)時脈合成器如圖11-8。

11.2.5.計時/計數器

計時/數模組為單晶片系統之重要模組。

圖11-9為基本之計時/計數器模組架構。

輸入訊號透過預除器(Prescaler),使時脈速率降低與獲得較穩定訊號。

計數後之輸出,通過後除器(Postescaler),可將計數結果分群輸出或降低模組計數輸出速率。

計數器模組使用時,透過控制暫存器設定預除器(N)、後除器(M)、及其它時脈參數(如:

正負緣觸發、時脈來源、中斷設定…等等)。

由狀態暫存器瞭解目前模組狀態。

妥善應用計時器模組所輸出之計數數值,可設計各種周邊應用模組,如:

捕抓(capture)模組、比較(compare)模組、脈波寬調變(pulsewidthmodulation,PWM)模組。

捕抓(capture)模組:

捕抓某外部訊號(脈衝訊號)發生之時間,可應用於碼表、測距等應用,如:

圖11-10。

啟動計時器後,於接收到觸發訊號時,捕捉計時器數值。

如圖11-10(a)測量訊號之時間間隔(碼表)。

圖11-10(b)測量發射與反射訊號之時間間隔,並透過轉換計算換算出發射器與反射物體之距離(測距)。

基本之捕捉模組架構圖如圖11-11。

輸入訊號經過預除器(Prescaler)可獲得較穩定訊號(假設觸發訊號為單頻脈衝訊號)。

邊緣偵測電路可記錄接收訊號之準確觸發時間,再將此時計時器數值捕捉至資料暫存器。

一般捕捉模組以中斷控制模式控制,如此才能在事件發生時立刻處理。

比較(compare)模組:

比較模組之輸出可以應用為系統之時基(Timebase)。

或產生特定週期之控制訊號,控制特殊模組,如:

ADC之取樣時脈,設定類比訊號轉換數位資訊之取樣週期(samplingtime)。

比較模組之基本架構圖如圖11-12。

由計時器(內部時脈計時)/計數器(外部訊號計數)、資料暫存器與比較器組成。

經由比較器之比對計時/計數器與資料暫存器之內容,於相等時產生訊號。

如此,可產生固定之時脈訊號,此種模式稱比較(compare)。

脈波寬調變(pulsewidthmodulation,PWM)模組:

PWM訊號常見用於功率、馬達轉速、亮度等直流平均值之控制,PWM訊號波形如圖11-13。

將高頻率脈波訊號之責任週期(Dutycycle)與訊號之直流平均值有關(可應用Fourier分析瞭解)。

因此,設定訊號之責任週期,同時使脈波訊號平均值依設定改變。

只要將訊號通過等效低通濾波器(不一定要有真正之濾波器),移除高頻訊號,就可隨意控制直流平均值。

但應用時,由於脈波頻率極高,PWM模組容易產生高頻諧波干擾。

11.2.6.基本I/O埠:

單晶系統之基本輸出入模組,可設定規劃各模組位元之輸出入方向(輸入、輸出或雙向)。

由於基本I/O埠所使用之腳位非常多(幾個I/O訊號就要幾隻腳位),因此一般會與其他模組多工使用晶片之腳位,因此規劃使用時需注意其他模組之使用情況。

某些單晶系統也會將並列式I/O埠與基本I/O埠多工使用,如此可以節省外部之接腳數,但相對增加使用之複雜度。

輸出埠之設計模式,有開集(汲)級輸出、三態輸出、圖騰柱輸出,以及是否資料緩衝(buffer)。

推動能力從數mA至數十mA,一般推動能力之流入電流(汲入sink)與流出電流(源出source)驅動力不同,使用時要注意資料說明。

輸入埠之設計模式,有弱提升電阻(pullupresistance)輸入模式、史密特觸發模式、資料閂鎖(latch)模式等。

由於省電是單晶重要課題,在省電模式底下,使用者需依照資料手冊與系統設計將所有輸出入埠設定至省電狀態(大部份為輸出方向,堆動力0mA之狀態)。

11.2.7.串列傳輸

串列傳輸為單晶片系統之基本資料傳輸界面,用於晶片間或數位系統間之資料傳輸。

單晶片微處理機常配置之串列傳輸模組規格有UART、I2C、…等。

傳輸模式依傳輸資料在傳送端與接收端是否同步,區分為同步(Synchronous)串列傳輸與非同步(Asynchronous)串列傳輸。

同步(Synchronous)傳輸之概念如圖11-14。

在啟動傳輸後資料位元隨傳輸時脈逐位元傳輸,傳輸端必需將傳輸時脈傳至接收端,供接收端同步接收。

非同步(Asynchronous)傳輸之概念如圖11-15。

與同步傳輸之主要差別為,傳輸時脈用於傳輸速率之參考,傳送時並不用傳遞時脈訊號至接收端。

訊號位元之偵測是透過startbit與stopbit控制。

接收端在接收到超過一個位元時間長度之STARTbit確認傳輸開始,開始接收第一個資料位元(bit0),當接收完最後位元(bit7/8)時,接收端以STOPbit判斷傳輸資料是否完整,若不完整將產生接收資料錯誤之訊號。

串列傳輸之速率規格稱baudrate(bit/sec),傳輸過程需遵守嚴謹之通訊交握協定。

因此,使用時需詳細了解各種串列傳輸規格之通訊協定(communicationprotocol)。

11.2.8.AnalogI/O:

ADC,DAC

將現實環境之訊號應用單晶片系統處理。

首先,必須將類比訊號轉換為數位資訊。

將類比訊號經過取樣、維持、轉換之等過程,轉變成為數位資訊,如圖11-16。

此轉換過程常簡稱為類比數位轉換(analog-to-digitalconversion,ADC)。

類比轉數位模組,由取樣電路、維持電容與類比轉數位轉換器電路所組成,如圖11-17為類比轉數位模組之基本架構圖。

類比數位轉換過程,若希望轉換完成之數位資訊保持所有原類比訊號之特徵。

根據訊號處理理論,需依取樣定理(samplingtheorem)取樣,取樣之時間間隔稱取樣時間

,必須符合取樣定理。

,

為類比訊號之最高頻率。

圖11-17為類比轉數位(ADC)基本架構圖。

運作方式,首先依取樣時間取樣(維持電路一般會自動運作),接著開始轉換,等待轉換完成訊號(endofconversion,EOC),最後讀取數位資訊。

開始轉換,至轉換完成一般須數個至數千個轉換時脈週期,稱ADC之轉換時間,與使用之轉換技術與位元解析度有關。

以10bit之轉換解析度而言,目前單晶片之ADC模組,一般須十數個時脈週期。

轉換完成後,模組會產生轉換完成之訊號(end-of-conversion,EOC)。

此時資料暫存器將儲存對應於取樣值之量化數位資料。

當系統處理完資料待輸出至現實環境時,也需還原為類比訊號型態。

此時,需要使用數位類比轉換器(digital-to-analogconversion,DAC),將數位資訊轉換為類比訊號。

數位資訊還原為類比訊號之轉換過程如圖11-18。

只要原始訊號在取樣時遵守取樣定理,則最後可將處理後之訊號正確還原為類比訊號。

圖11-19數位類比轉換器之架構圖,其中重建濾波器之主要功能類似一個低通濾波器,將多餘之高頻雜訊濾除。

低通濾波器之截止頻帶要大於訊號頻帶遠小於取樣頻率。

11.2.9.其他模組

除了常見之周邊模組外。

單晶片微處理機,常為了某些特殊用途,加入各種周邊模組,如:

射頻訊號發射接收模組(RF)、步進馬達控制模組、直流馬達控制模組、語音聲頻處理模組(audio)、語音辨識模組、…等等。

各種模組雖應用不同,但控制與應用之模式皆大同小異。

接下來,將介紹周邊模組之基本控制方法與概念。

11.3.周邊模組之控制方法

單晶片對周邊模組之控制方法,一般可分為兩類:

1、直接控制模式,2、互動控制模式。

1、直接控制模式:

設定後周邊模組自行運作不需額外控制,如:

基本之數位輸出/輸入埠、或PMM模組。

2、互動控制模式:

CPU與周邊模組需透過一來一往之交握(handshake)程序、或答詢過程,才能完成正確之控制。

一般依互動處理方式,分諮詢控制式與中斷控制式。

如:

串列傳輸、ADC/DAC、…等較複雜功能之周邊模組,皆屬於此控制模式。

周邊模組應用時,一定要依模組所規定之交握程序互動,才能正確控制。

單晶片微處理機中,各周邊模組必定有對應之控制暫存器、資料暫存器、旗標或狀態暫存器,用以設定、控制與應用周邊模組。

應用時只要正確設定就可輕鬆使用。

詳細之控制位元一定要確實查詢各CPU系列之模組資料,因為各種CPU之定義皆不相同。

11.3.1.直接控制式

基本動作如圖11-20所示,為最基本之控制方法,基本輸出入模組皆用此模式控制。

或控制流程簡單之周邊模組,如:

PWM設並後就自動週期性產生訊號,也是以直接模式控制。

11.3.2.諮詢控制式

屬於基本互動式控制,大部分模組皆可以控制,方法簡單。

由於控制方式須由以CPU不斷諮詢模組狀態,佔用大部分CPU時間,因此有效率低、與無法同時控制多周邊模組之缺點。

控制方法流程如圖11-21:

11.3.3.中斷控制模式

屬於背景式互動式控制,控制流程如圖11-22。

必需周邊模組提供中斷功能,才可使用此模式控制。

由於中斷發生時,才佔用CPU時間處理。

因此,控制效率佳,且可同時控制多數模組不影響周邊運作。

但由於中斷服務程式撰寫技巧較高與偵錯不易,較不易學習。

中斷服務程式為中斷控制是否完美之核心。

中斷服務程式之流程如圖11-23。

只要熟練中斷服務程式之設計規則,中斷控制模式將是單晶片微處理器控制周邊模組之最佳利器。

中斷服務程式之基本規則有:

1、使用中斷控制功能必須將中斷服務程式,設定至對應之中斷向量。

2、中斷服務程式必需執行下列步驟:

(1)遮罩低階或全部中斷,避免中斷期間再中斷。

(2)檢查中斷旗標,確定中斷源是那一周邊所產生。

(3)暫存器保存與還原。

(4)迅速處理中斷資料。

(5)清除中斷旗,使下次中斷訊號可繼續產生。

3、中斷服務程式必需以最短之時間結束,避免影響系統正常運作。

4、中斷服務程式之資料區,需為獨立單一入口,避免因中斷過程影響資料之完整性。

11.4.單晶片系統之設計與發展

系統設計開發過程包括有規格設定分析、系統架構設計、軟應體功能劃分、功能模擬與驗證、功能與系統測試、系統修改。

以下將針對單晶片微處理機系統之整合發展環境與學習流程建議加以說明。

11.4.1.單晶片之整合發展環境(integratedevelopmentenvironment,IDE)

由於系統設計開發過程繁瑣,透過整合發展環境可將所有功能整合在單一軟體界面,包括有:

專案管理、文件編輯與編譯、執行(模擬、執行、下載執行)、偵錯功能、記憶體檢視、反組譯功能、及其他檢查與控制功能。

11.4.2.單晶片微處理器學習流程:

由於全世界單晶片微處理器有許多系列,且不斷更新增加中。

因此需有正確之學習方法才能事半功倍。

各種系列之微處理器,雖然有不同之CPU核心(指令集)、周邊模組,但基本之程式技巧是不變的,周邊模組的應用與控制模式也是不變的,改變的只是指令集、模組暫存器之規劃、與細部功能之調整。

瞭解單晶片微處理器特性後,可以發現經由以下之步驟學習可以獲得良好之效果。

1.瞭解基本之單晶架構與周邊模組關係及各模組之用途。

2.進一步瞭解模組之應用與模組設計之技巧。

3.熟練基本之軟體程式技巧,透過對基本程式流程與資料處理技巧,可以以各種語言撰寫程式(因為單晶片講究效率,一般使用非標準化之組合語言,每一種系列CPU有自己之語言,可經由CPU之datasheet快速學習指令集)。

4.熟悉發展流程與發展之工具環境與應用技巧。

雖然各種環境有不同之功能,但只要瞭解發展流程與工具應用技巧,自然可輕鬆使用各種系統。

由於單晶系統有多樣性與軟、硬體並存之特性。

發展工具與環境也多元化,並且需軟硬體配合發展,造成學習入門之困擾。

因此,應以發展流程為學習重點而非工具之操作。

所以學習發展環境之操作時,需以發展流程中所需注意之概念為重點。

依筆者之經驗有以下幾點學習重點:

1.專案管理,學習各種相關檔案之設定與編輯之基本要素。

2.程式之撰寫與偵錯,瞭解程式流程與資料處理之技巧,可經由一般程式語言課程加強學習。

3.模組化之發展與偵錯,需學習單一模組之軟硬體獨立偵錯,將各模組之錯誤分別找出修正,減低整合系統時之偵錯負擔。

基本技巧為使用模擬激勵與資料,並透過虛擬架構(Dummyprogram)呼叫。

所謂虛擬架構呼叫指的是,與模組相關之訊號與程式,透過一空的程式將所需之資料與模擬激勵訊號傳回,並記錄輸入之參數。

空程式中並沒有其它功能。

單步執行(step)、中斷點(breakpoint)等設定程式觀察點,分析程式執行流程與結果,並判斷與預期是否相符。

以中斷模式控制之模組,由於中斷程式會與偵錯技巧中,單步執行(step)、中斷點(breakpoint)…等偵錯用中斷模式互相影響。

因此,建議周邊模組之偵錯,一定要盡量在單一模組發展過程完成,避免影響整合過程。

4.模擬仿真偵錯技巧,當硬體尚未正確完成時,一般可透過發展環境之模擬(simulation)或仿真(emulation)功能進行軟硬體之偵錯,可透過軟、硬體之中斷點(breakpoint)、流程追蹤(trace)、同步觸發等偵錯技巧發現程式間潛藏之錯誤(BUG)。

模擬(simulation),為整合發展環境(IDE)提供,以軟體模擬該單晶片微處理器之核心與周邊模組功能。

依整合發展環境提供不同等級之模擬功能。

高級之模擬功能,可在完全沒有相關硬體環境下,完成單晶系統程式之偵錯、功能驗證與修改。

仿真(emulation):

線上仿真器(incircuitemulation,ICE)提供單晶片微處理器之核心與周邊模組之硬體模擬,並可與外部之硬體電路連接,如此可輕易進行軟、硬體之交互偵測。

也可在程式未開發完成前,對硬體進行整合測試。

5.軟硬體與系統整合偵錯技巧,此過程一般需重覆步驟3,4,搭配各種硬體訊號之量測儀器(如:

示波器、邏輯分析儀、訊號產生器等),分析各種使用狀況之訊號與程式流程。

11.5.結論

單晶片系統是各種系統整合應用之核心,也是系統晶片(SOC)設計之重點。

由於應用與晶片種類之多樣化。

因此,學習時應以各種周邊模組之設計、應用與控制概念為主,配合相關晶片之實作演練,並於相關之課程多方瞭解,如此必能收到事半功倍之效果。

由於坊間有許多單晶片微處理機之學習資料,可挑選容易實作演練之晶片系列學習。

也