EDA考试常考试题.docx

《EDA考试常考试题.docx》由会员分享,可在线阅读,更多相关《EDA考试常考试题.docx(13页珍藏版)》请在冰豆网上搜索。

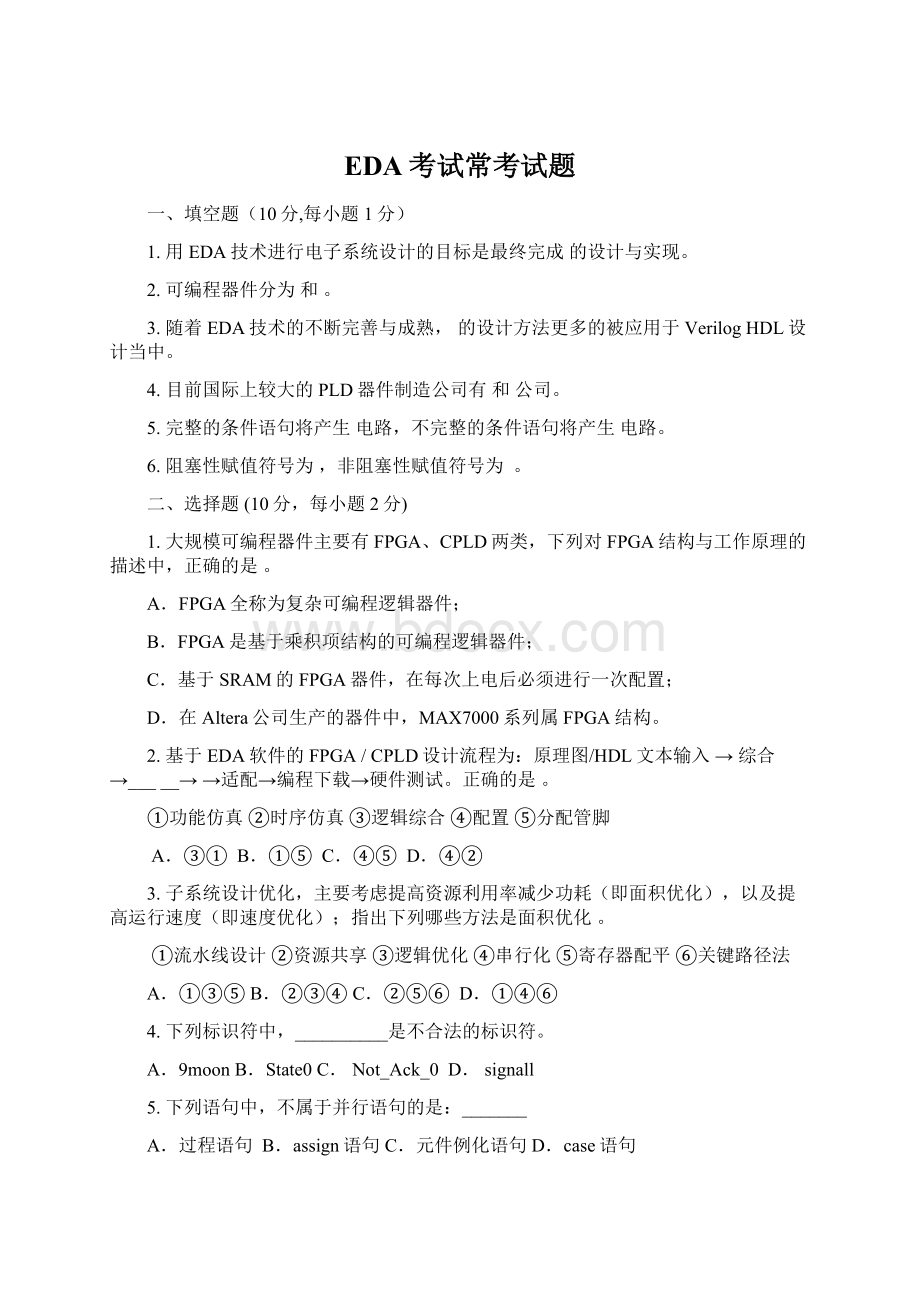

EDA考试常考试题

一、填空题(10分,每小题1分)

1.用EDA技术进行电子系统设计的目标是最终完成的设计与实现。

2.可编程器件分为和。

3.随着EDA技术的不断完善与成熟,的设计方法更多的被应用于VerilogHDL设计当中。

4.目前国际上较大的PLD器件制造公司有和公司。

5.完整的条件语句将产生电路,不完整的条件语句将产生电路。

6.阻塞性赋值符号为,非阻塞性赋值符号为。

二、选择题(10分,每小题2分)

1.大规模可编程器件主要有FPGA、CPLD两类,下列对FPGA结构与工作原理的描述中,正确的是。

A.FPGA全称为复杂可编程逻辑器件;

B.FPGA是基于乘积项结构的可编程逻辑器件;

C.基于SRAM的FPGA器件,在每次上电后必须进行一次配置;

D.在Altera公司生产的器件中,MAX7000系列属FPGA结构。

2.基于EDA软件的FPGA/CPLD设计流程为:

原理图/HDL文本输入→综合→_____→→适配→编程下载→硬件测试。

正确的是。

①功能仿真②时序仿真③逻辑综合④配置⑤分配管脚

A.③①B.①⑤C.④⑤D.④②

3.子系统设计优化,主要考虑提高资源利用率减少功耗(即面积优化),以及提高运行速度(即速度优化);指出下列哪些方法是面积优化。

①流水线设计②资源共享③逻辑优化④串行化⑤寄存器配平⑥关键路径法

A.①③⑤B.②③④C.②⑤⑥D.①④⑥

4.下列标识符中,__________是不合法的标识符。

A.9moonB.State0C.Not_Ack_0D.signall

5.下列语句中,不属于并行语句的是:

_______

A.过程语句B.assign语句C.元件例化语句D.case语句

三、EDA名词解释(10分)

写出下列缩写的中文含义:

ASIC:

RTL:

FPGA:

SOPC:

CPLD:

LPM:

EDA:

IEEE:

IP:

ISP:

四、简答题(10分)

1.简要说明仿真时阻塞赋值与非阻塞赋值的区别(本题4分)。

2.简述有限状态机FSM分为哪两类?

有何区别?

有限状态机的状态编码风格主要有哪三种?

FSM的三段式描述风格中,三段分别描述什么?

(本题6分)

五、程序注解(20分,每空1分)

moduleAAA(a,b);

outputa;

input[6:

0]b;

reg[2:

0]sum;

integeri;

rega;

always@(b)

begin

sum=0;

for(i=0;i<=6;i=i+1)

if(b[i])

sum=sum+1;

if(sum[2])a=1;

elsea=0;

end

endmodule

本程序的逻辑功能是:

。

六、VerilogHDL语言编程题(1、2小题10分,3小题20分)

要求:

写清分析设计步骤和注释。

1.试用VerilogHDL描述一个带进位输入、输出的8位全加器。

端口:

A、B为加数,CI为进位输入,S为和,CO为进位输出

2.编写一个带异步清零、异步置位的D触发器。

端口:

CLK为时钟,D为输入,CLK为清零输入端,SET为置位输入端;Q输出端。

3.设计一个带有异步复位控制端和时钟使能控制端的10进制计数器。

端口设定如下:

输入端口:

CLK:

时钟,RST:

复位端,EN:

时钟使能端,LOAD:

置位控制端,

DIN:

置位数据端;

输出端口:

COUT:

进位输出端,DOUT:

计数输出端。

一、填空题(每空2分,共20分)

1、ASIC

2、FPGA和CPLD。

3、自顶向下

4、Altera和Xilinx

5、组合时序

6、=<=

二、选择题(10分,每小题2分)

1、C2、B3、B4、A5、D

三、EDA名词解释(10分)

ASIC专用集成电路RTL寄存器传输级

FPGA现场可编程门阵列SOPC可编程片上系统

CPLD复杂可编程逻辑器件LPM 参数可定制宏模块库

EDA电子设计自动化IEEE 电子电气工程师协会

IP知识产权核ISP 在系统可编程

四、简答题(10分)

1、简要说明仿真时阻塞赋值与非阻塞赋值的区别(本题4分)。

答:

非阻塞(non-blocking)赋值方式(b<=a):

b的值被赋成新值a的操作,并不是立刻完成的,而是在块结束时才完成;

块内的多条赋值语句在块结束时同时赋值;

硬件有对应的电路。

阻塞(blocking)赋值方式(b=a):

b的值立刻被赋成新值a;

完成该赋值语句后才能执行下一句的操作;

硬件没有对应的电路,因而综合结果未知。

2、简述有限状态机FSM分为哪两类?

有何区别?

有限状态机的状态编码风格主要有哪三种?

FSM的三段式描述风格中,三段分别描述什么?

(本题6分)

答:

Mearly型,Moore型;前者与输入与当前状态有关,而后者只和当前状态有关;Binary,Gray,One-Hot编码;分别为状态保存,状态切换,输出;

五、程序注解(20分,每空1分)

moduleAAA(a,b);定义模块名为AAA,端口为a,b

outputa;定义a为输出端口

input[6:

0]b;定义b为输出端口,b为7位二进制数

reg[2:

0]sum;sum为reg型变量,用于统计赞成的人数

integeri;定义整型变量i为循环控制变量

rega;定义a为寄存器变量

always@(b)过程语句,敏感变量为b

begin语句块

sum=0;sum初值为0

for(i=0;i<=6;i=i+1)for语句,统计b为1的个数

if(b[i])条件语句

sum=sum+1;只要有人投赞成票,则sum加1

if(sum[2])a=1;若超过4人赞成,则表决通过

elsea=0;若不到4人,则不通过

end

endmodule

本程序的逻辑功能是:

7人投票表决器。

六、VerilogHDL编程题(1、2小题10分,3小题20分)

要求:

写清分析设计步骤和注释。

1.试用VerilogHDL描述一个带进位输入、输出的8位全加器。

端口:

A、B为加数,CIN为进位输入,S为和,COUT为进位输出

moduleadd4v(a,b,ci,s,co);

input[3:

0]a;

input[3:

0]b;

inputci;

output[3:

0]s;

outputco;

wire[3:

0]carry;

functionfa_s(inputa,inputb,inputci);

fa_s=a^b^ci;

endfunction

functionfa_c(inputa,inputb,inputci);

fa_c=a&b|a&ci|b&ci;

endfunction

assigns[0]=fa_s(a[0],b[0],ci);

assigncarry[0]=fa_c(a[0],b[0],ci);

assigns[1]=fa_s(a[1],b[1],carry[0]);

assigncarry[1]=fa_c(a[1],b[1],carry[0]);

assigns[2]=fa_s(a[2],b[2],carry[1]);

assigncarry[2]=fa_c(a[2],b[2],carry[1]);

assigns[3]=fa_s(a[3],b[3],carry[2]);

assignco=fa_c(a[3],b[3],carry[2]);

endmodule

2.编写一个带异步清零、异步置位的D触发器。

3.设计一个带有异步复位控制端和时钟使能控制端的10进制计数器。

mduleCNT10(CLK,RST,EN,LOAD,COUT,DOUT,DATA);

inputCLK;

inputEN;

inputRST;

inputLOAD;

input[3:

0]DATA;

output[3:

0]DOUT;

outputCOUT;

reg[3:

0]Q1;

regCOUT;

assignDOUT=Q1;

always@(posedgeCLKornegedgeRST)begin

if(!

RST)Q1<=0;

elseif(EN)

begin

if(!

LOAD)Q1<=DATA;

elseif(Q1<9)Q1<=Q1+1;

elseQ1<=4'b0000;

end

end

always@(Q1)

if(Q1==4'h9)COUT=1'b1;

elseCOUT=1'b0;

endmodule