软件总体架构图.doc

《软件总体架构图.doc》由会员分享,可在线阅读,更多相关《软件总体架构图.doc(14页珍藏版)》请在冰豆网上搜索。

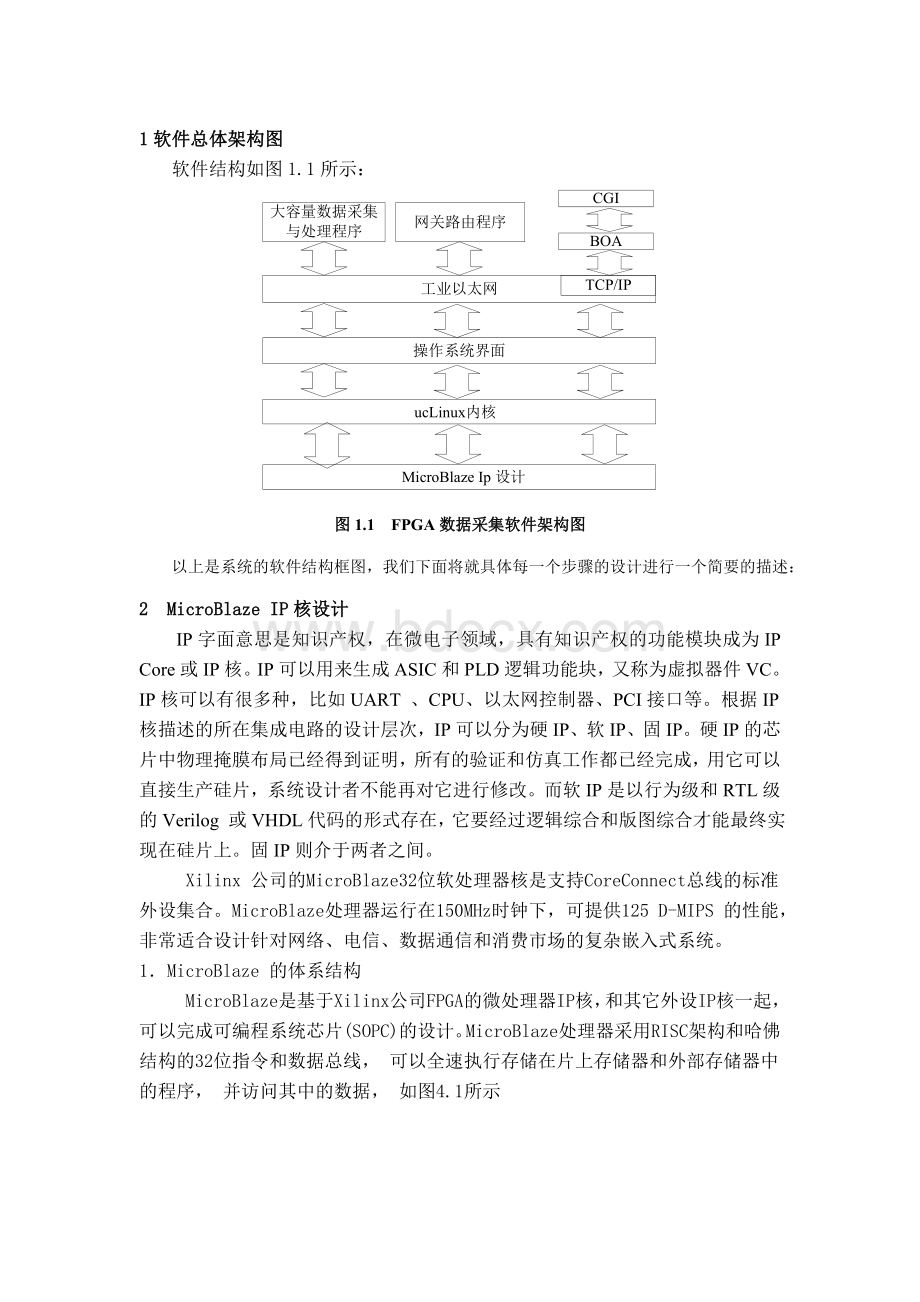

1软件总体架构图

软件结构如图1.1所示:

图1.1FPGA数据采集软件架构图

以上是系统的软件结构框图,我们下面将就具体每一个步骤的设计进行一个简要的描述:

2MicroBlazeIP核设计

IP字面意思是知识产权,在微电子领域,具有知识产权的功能模块成为IPCore或IP核。

IP可以用来生成ASIC和PLD逻辑功能块,又称为虚拟器件VC。

IP核可以有很多种,比如UART、CPU、以太网控制器、PCI接口等。

根据IP核描述的所在集成电路的设计层次,IP可以分为硬IP、软IP、固IP。

硬IP的芯片中物理掩膜布局已经得到证明,所有的验证和仿真工作都已经完成,用它可以直接生产硅片,系统设计者不能再对它进行修改。

而软IP是以行为级和RTL级的Verilog或VHDL代码的形式存在,它要经过逻辑综合和版图综合才能最终实现在硅片上。

固IP则介于两者之间。

Xilinx公司的MicroBlaze32位软处理器核是支持CoreConnect总线的标准外设集合。

MicroBlaze处理器运行在150MHz时钟下,可提供125D-MIPS的性能,非常适合设计针对网络、电信、数据通信和消费市场的复杂嵌入式系统。

1.MicroBlaze的体系结构

MicroBlaze是基于Xilinx公司FPGA的微处理器IP核,和其它外设IP核一起,可以完成可编程系统芯片(SOPC)的设计。

MicroBlaze处理器采用RISC架构和哈佛结构的32位指令和数据总线,可以全速执行存储在片上存储器和外部存储器中的程序,并访问其中的数据,如图4.1所示

图2.1MicroBlaze内核结构框图

(1)内部结构

MicroBlaze内部有32个32位通用寄存器和2个32位特殊寄存器——PC指针和MSR状态标志寄存器。

为了提高性能,MicroBlaze还具有指令和数据缓存。

所有的指令字长都是32位,有3个操作数和2种寻址模式。

指令按功能划分有逻辑运算、算术运算、分支、存储器读/写和特殊指令等。

指令执行的流水线是并行流水线,它分为3级流水:

取指、译码和执行,如图4.2所示。

图2.2MicroBlaze的流水线

(2)存储结构

MicroBlaze是一种大端存储系统处理器,使用如图4.3所式的格式来访问存储器。

图2.3大端数据格式

(3)中断控制和调试接口

MicroBlaze可以响应软件和硬件中断,进行异常处理,通过外加控制逻辑,可以扩展外部中断。

利用微处理器调试模块(MDM)IP核,可通过JTAG接口来调试处理器系统。

多个MicroBlaze处理器可以用1个MDM来完成多处理器调试。

(4)快速单一链路接口

MicroBlaze处理器具有8个输入和8个输出快速单一链路接口(FSL)。

FSL通道是专用于单一方向的点到点的数据流传输口。

FLS和MicroBlaze的接口宽度是32位。

每一个FSL通道都可以发送和接收控制或数据字。

2.CoreConnect技术

CoreConnect是由IBM开发的片上总线通信链,它使多个芯片核相互连接成为一个完整的新芯片成为可能。

CoreConnect技术使整合变得更为容易,而且在标准产品平台设计中,处理器、系统以及外围的核可以重复使用,以达到更高的整体系统性能。

Xilinx将为所有嵌入式处理器用户提供IBMCoreConnect许可,因为它是所有Xilinx嵌入式处理器设计的基础。

MicroBlaze处理器使用了与IBMPowerPC相同的总线,用作外设。

虽然MicroBlaze软处理器完全独立于PowerPC,但它让设计者可以选择芯片上的运行方式,包括一个嵌入式PowerPC,并共享它的外设。

CoreConnect总线架构如图4.4所示。

它包括片上外围总线(OPB),处理器本机总线(PLB),设备控制寄存器(DCR)总线以及1个总线桥和2个判优器。

图2.4CoreConnect总线架构

(1)片上外设总线(OPB)

内核通过片上外设总线(OPB)来访问低速和低性能的系统资源。

OPB是一种完全同步总线,它的功能处于一个单独的总线层级。

它不是直接连接到处理器内核的。

OPB接口提供分离的32位地址总线和32位数据总线。

处理器内核可以借助“PLBtoOPB”桥,通过OPB访问从外设。

作为OPB总线控制器的外设可以借助“OPBtoPLB”桥,通过PLB访问存储器。

(2)处理器本机总线(PLB)

PLB接口为指令和数据一侧提供独立的32位地址和64位数据总线。

PLB支持具有PLB总线接口的主机和从机通过PLB信号连接来进行读写数据的传输。

总线架构支持多主从设备。

每一个PLB主机通过独立的地址总线、读数据总线和写数据总线与PLB连接。

PLB从机通过共享但分离的地址总线、读数据总线和写数据总线与PLB连接,对于每一个数据总线都有一个复杂的传输控制和状态信号。

为了允许主机通过竞争来获得总线的所有权,有一个中央判决机构来授权对PLB的访问。

(3)设备控制寄存器总线(DCR)

设备控制寄存器总线(DCR)是为在CPU通用寄存器(GPRs)和DCR的从逻辑设备控制寄存器(DCRs)之间传输数据而设计的。

3.MicroBlaze的开发

应用EDK(嵌入式开发套件)可以进行MicroBlazeIP核的开发。

工具包中集成了硬件平台产生器、软件平台产生器、仿真模型生成器、软件编译器和软件调试工具等。

EDK中提供一个集成开发环境XPS(XilinxPlatformStudio),以便使用系统提供的所有工具,完成嵌入式系统开发的整个流程。

EDK中还带有一些外设接口的IP核,如LMB、OPB总线接口、外部存储控制器、SDRAM控制器、UART、中断控制器、定时器等。

利用这些资源,可以构建一个较为完善的嵌入式微处理器系统。

在FPGA上设计的嵌入式系统层次结构为5级,可在最低层硬件资源上开发IP核,或利用已开发的IP核搭建嵌入式系统,这是硬件开发部分;开发IP核的设备驱动、应用接口(API)和应用层(算法),属软件开发内容。

利用MicroBlaze构建基本的嵌入式系统如图4.5所示。

通过标准总线接口——LMB总线和OPB总线的IP核,MicroBlaze就可以和各种外设IP核相连。

图2.5MicroBlaze系统架构图

EDK中提供的IP核均有相应的设备驱动和应用接口,使用者只需利用相应的函数库,就可以编写自己的应用软件和算法程序。

对于用户自己开发的IP核,需要自己编写相应的驱动和接口函数。

软件设计流程如图4.6所示。

图2.6软件开发流程

3移植uclinux

首先不管什么平台,移植uclinux,整个流程都遵从于:

Kernelpreparation—>isntallBSP—>Buildhardwareplatform—>Memorytest—>Buildkernelimage—>Download具体来说,如下图4.7所示:

图3.1uclinux移植流程

1.搭建开发环境

操作系统:

RedhatHatLinux9,安装的时候添加开发和编译环境。

(编译内核)Windows(安装EDK)

交叉编译工具:

针对不同的CPU系列,有不同的编译环境,通常,程序是在一台计算机上编译,然后再分布到将要使用的其他计算机上。

当主机系统(运行编译器的系统)和目标系统(产生的程序将在其上运行的系统)不兼容时,该过程就叫做交叉编译。

建立一个交叉编译工具链是一个相当复杂的过程,网上有一些编译好的可用的交叉编译工具链可以下载。

下载并安装好,我们的编译环境就搭建好了。

(1)下载并创建BSP

从petalogix站点下载BSP,并安装到电脑上。

把在EDK下生成的包含硬件系统信息的“auto-config.in”文件复制到linux的/home/devel/src\uClinux-2.4.x\arch\microblaze\platform\uclinux-auto路径下。

编译器需要从auto-config.in文件里知道“theaddressmapandtheprocessorsystem”以及其它相关信息。

(2)配置内核

在网站上下载源代码包,并安装在系统的任意目录。

此时,就可以使用命令来进行内核的配置了:

$cd~/uClinux-dist

$makemenuconfig

这里,我们需要进行一系列内核配置的选择。

(3)编译内核生成image文件

$cd~/uClinux-dist

$makedep

$makeclean

$make

这个过程期间将完成下面的内容:

编译内核(Buildkernel)

编译uclinux的C库(Clibraries)

编译用户程序(userapplications)

转换成二进制文件

编译内核文件系统

合并内核和文件系统为一个二进制文件

编译成功,你就会在uClinux-dist的目录下发现一个新的目录images。

里面就包含了你编译成功的系统文件,image.elf和image.bin两个文件。

(4)下载内核文件到目标板

将在上面编译生成的内核文件image.bin下载到目标板上去并运行.

4.1移植工业以太网协议

由于Spartan-3E只提供了物理层(PHY)的网络控制器,所以对于处理本装置的物理层以上的网络设备,需要重新制定适合本系统的网络协议。

工业以太网EtherNet/IP,是一种适用于工业环境的通讯体系,能够在广阔的区域中支持大量现场设备的连接。

它采用通用工业协议(CIP)作为其应用层协议。

CIP协议支持各种控制、配置和信息处理服务,包括显式报文(用于信息传输,灵活的报文交换)以及隐式报文(用于控制和实时I/O数据的传输),支持轮询、周期和状态改变数据传输触发机制,点对点单播和广播数据传输方式[3]。

OE服务的设计简化了EtherNet/IP的移植,只需要修改操作环境文件来适合FPGA操作体系。

4.2移植BOA

从www.boa.org下载一个主流版本的BOA源码包,本系统用的是boa-0.94.13.tar.gz。

第一步:

修改Makefile文件,编译BOA源码,生成BOA可执行文件。

修改Makefile文件,因为我们要编译的是二进制代码,所以必须修改Makefile中的CC和CPP,然后运行make进行编译,得到可执行程序BOA。

第二步:

配置BOA。

BOA启动时将加载一个配置文件boa.conf,在boa程序运行前,必须首先编辑该文件。

在Boa源码目录下已有一个示例boa.conf,可以在其基础上修改。

配置好的主要内容如下:

Usernobody

Group0

ServerNameXilinxFPGA

ErrorLog/var/log/boa/error_log

AccessLog/var/log/boa/access_log

DocumentRoot/var/www

MimeTypes/etc/mime.types

ScriptAlias/cgi-bin//var/www/cgi-bin/

据此配置,需要创建日志文件目录/var/log/boa,HTML文档的主目录/var/www,将静态网页存入该目录下,CGI脚本所在目录/var/www/cgi-bin,将cgi的脚本存放在该目录下。

4.3CGI网关接口程序

CGI(通用网关接口)提供Web服务器一个执行外部程序的通道,这种服务端技术建立了Web浏览器与W