EDA考试常用程序 武汉大学.docx

《EDA考试常用程序 武汉大学.docx》由会员分享,可在线阅读,更多相关《EDA考试常用程序 武汉大学.docx(17页珍藏版)》请在冰豆网上搜索。

EDA考试常用程序武汉大学

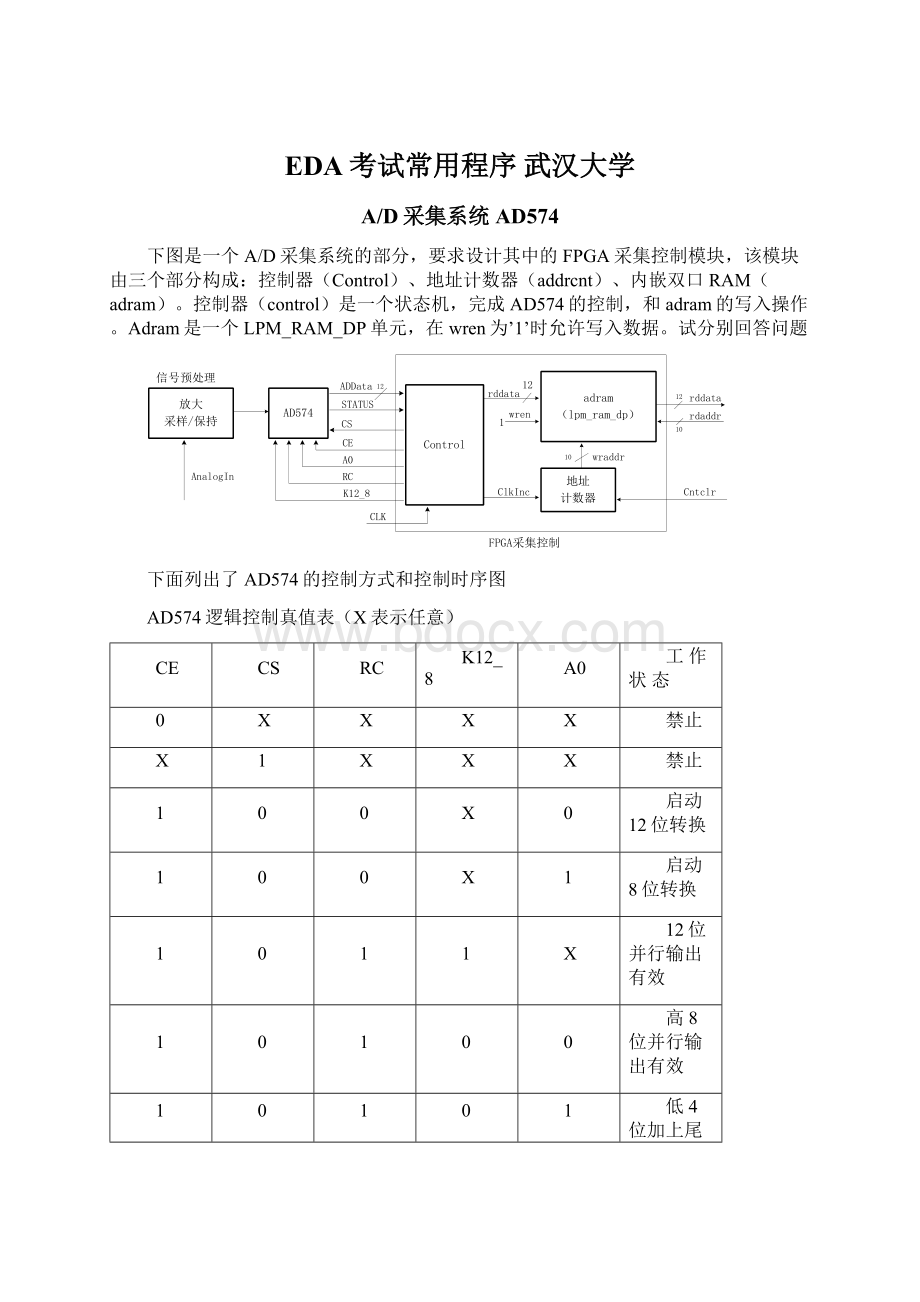

A/D采集系统AD574

下图是一个A/D采集系统的部分,要求设计其中的FPGA采集控制模块,该模块由三个部分构成:

控制器(Control)、地址计数器(addrcnt)、内嵌双口RAM(adram)。

控制器(control)是一个状态机,完成AD574的控制,和adram的写入操作。

Adram是一个LPM_RAM_DP单元,在wren为’1’时允许写入数据。

试分别回答问题

下面列出了AD574的控制方式和控制时序图

AD574逻辑控制真值表(X表示任意)

CE

CS

RC

K12_8

A0

工作状态

0

X

X

X

X

禁止

X

1

X

X

X

禁止

1

0

0

X

0

启动12位转换

1

0

0

X

1

启动8位转换

1

0

1

1

X

12位并行输出有效

1

0

1

0

0

高8位并行输出有效

1

0

1

0

1

低4位加上尾随4个0有效

AD574工作时序:

1.要求AD574工作在12位转换模式,K12_8、A0在control中如何设置

K12_8为‘1’,A0为‘0’

2.试画出control的状态机的状态图

类似书上图8-4

3.对地址计数器模块进行VHDL描述

输入端口:

clkinc计数脉冲

cntclr计数器清零

输出端口:

rdaddrRAM读出地址,位宽10位

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityaddr_cntis

port(clkinc,cntclr:

instd_logic;

wraddr:

outstd_logic_vector(9downto0));

endaddr_cnt;

architectureoneofaddr_cntis

signaltmp:

std_logic_vector(9downto0);

begin

process(clkinc,cntclr)

begin

ifclkinc'eventandclkinc='1'then

ifcntclr='1'then

tmp<=(others=>'0');

else

tmp<=tmp+1;

endif;

endif;

endprocess;

wraddr<=tmp;

endone;

4.根据状态图,试对control进行VHDL描述

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entitycontrolis

port(addata:

instd_logic_vector(11downto0);

status,clk:

instd_logic;

cs,ce,a0,rc,k12_8,clkinc:

outstd_logic;

rddata:

outstd_logic_vector(11downto0));

endcontrol;

architecturebehavofcontrolis

typecon_stis(s0,s1,s2,s3,s4);

signalcst,nst:

con_st;

signallock:

std_logic;

signalreg12:

std_logic_vector(11downto0);

begin

a0<='0';

k12_8<='1';

ce<='1';

cs<='0';

REGP:

process(clk)

begin

ifclk'eventandclk='1'then

cst<=nst;

endif;

endprocess;

COMP:

process(cst,status,addata)

begin

case(cst)is

whens0=>rc<='1';lock<='0';nst<=s1;

whens1=>rc<='0';lock<='0';nst<=s2;

whens2=>ifstatus='1'thennst<=s3;endif;

rc<='1';lock<='0';

whens3=>rc<='1';lock<='1';nst<=s4;

whens4=>rc<='1';lock<='0';nst<=s0;

whenothers=>nst<=s0;

endcase;

endprocess;

LOCKP:

process(lock)

begin

iflock='1'andlock'eventthen

reg12<=addata;

endif;

endprocess;

rddata<=reg12;

clkinc<=lock;--(或者为NOTLOCK,延后半个时钟)

endbehav;

5.已知adram的端口描述如下

ENTITYadramIS

PORT

(

data:

INSTD_LOGIC_VECTOR(11DOWNTO0);--写入数据

wraddress:

INSTD_LOGIC_VECTOR(9DOWNTO0);--写入地址

rdaddress:

INSTD_LOGIC_VECTOR(9DOWNTO0);--读地址

wren:

INSTD_LOGIC:

='1';--写使能

q:

OUTSTD_LOGIC_VECTOR(11DOWNTO0)--读出数据

);

ENDadram;

试用例化语句,对整个FPGA采集控制模块进行VHDL描述

libraryieee;

useieee.std_logic_1164.all;

entitydacois

port(clk,cntclr,status:

instd_logic;

addata:

instd_logic_vector(11downto0);

rdaddr:

instd_logic_vector(9downto0);

cs,ce,a0,rc,k12_8:

outstd_logic;

rddata:

outstd_logic_vector(11downto0));

enddaco;

architectureoneofdacois

componentcontrolis

port(addata:

instd_logic_vector(11downto0);

status,clk:

instd_logic;

cs,ce,a0,rc,k12_8,clkinc:

outstd_logic;

rddata:

outstd_logic_vector(11downto0));

endcomponent;

componentaddr_cntis

port(clkinc,cntclr:

instd_logic;

wraddr:

outstd_logic_vector(9downto0));

endcomponent;

componentadramISPORT

(data:

INSTD_LOGIC_VECTOR(11DOWNTO0);--写入数据

wraddress:

INSTD_LOGIC_VECTOR(9DOWNTO0);--写入地址

rdaddress:

INSTD_LOGIC_VECTOR(9DOWNTO0);--读地址

wren:

INSTD_LOGIC:

='1';--写使能

q:

OUTSTD_LOGIC_VECTOR(11DOWNTO0)--读出数据

);

ENDcomponent;

signalrds:

std_logic_vector(11downto0);

signalclkinc:

std_logic;

signalwraddr:

std_logic_vector(9downto0);

begin

u1:

controlportmap(addata=>addata,status=>status,

clk=>clk,cs=>cs,ce=>ce,a0=>a0,rc=>rc,

k12_8=>k12_8,clkinc=>clkinc,rddata=>rds);

u2:

addr_cntportmap(clkinc=>clkinc,cntclr=>cntclr,wraddr=>wraddr);

u3:

adramportmap(data=>rds,wraddress=>wraddr,

rdaddress=>rdaddr,wren=>'1',q=>rddata);

endone;

看下面原理图,写出相应VHDL描述

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYTRI_STATEIS

PORT(E,A:

INSTD_LOGIC;

Y:

INOUTSTD_LOGIC;

B:

OUTSTD_LOGIC);

ENDTRI_STATE;

ARCHITECTUREBEHAVOFTRI_STATEIS

BEGIN

PROCESS(E,A,Y)

BEGIN

IFE='0'THEN

B<=Y;

Y<='Z';

ELSE

B<='Z';

Y<=A;

ENDIF;

ENDPROCESS;

ENDBEHAV;

带计数使能的异步复位计数器

输入端口:

clk时钟信号

rst异步复位信号

en计数使能

load同步装载

data(装载)数据输入,位宽为10

输出端口:

q计数输出,位宽为10

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYCNT1024IS

PORT(CLK,RST,EN,LOAD:

INSTD_LOGIC;

DATA:

INSTD_LOGIC_VECTOR(9DOWNTO0);

Q:

OUTSTD_LOGIC_VECTOR(9DOWNTO0));

ENDCNT1024;

ARCHITECTUREONEOFCNT1024IS

BEGIN

PROCESS(CLK,RST,EN,LOAD,DATA)

VARIABLEQ1:

STD_LOGIC_VECTOR(9DOWNTO0);

BEGIN

IFRST='1'THEN

Q1:

=(OTHERS=>'0');

ELSIFCLK='1'ANDCLK'EVENTTHEN

IFLOAD='1'THEN

Q1:

=DATA;

ELSE

IFEN='1'THEN

Q1:

=Q1+1;

ENDIF;

ENDIF;

ENDIF;

Q<=Q1;

ENDPROCESS;

ENDONE;

设计一个64位宽度的双向总线驱动电路。

参考程序:

libraryIEEE;

useIEEE.STD_LOGIC_1164.all;

entitybidiris

Port(dir,en:

instd_logic;

a,b:

inoutstd_logic_vegtor(width-1downto0));

endbidir;

architectureart1ofbidiris

Signalaout,bout:

std_logic_vegtor(width-1downto0);

Constantwidth:

=64;

Begin

Process(a,dir,en)

Begin

If((en=‘1’)and(dir=‘1’))thenbout<=a;

Elsebout<=“zzzzzzzz”;

Endif;

B<=bout;

Endprocess;

Process(b,dir,en)

Begin

If((en=‘1’)and(dir=‘0’))thenaout<=b;

Elseaout<=“zzzzzzzz”;

Endif;

a<=aout;

Endprocess;

endart1;

2设计一个带异步复位和可预置初值的10进制加1计数器。

参考程序:

libraryIEEE;

useIEEE.STD_LOGIC_1164.ALL;

useIEEE.STD_LOGIC_ARITH.ALL;

useIEEE.STD_LOGIC_UNSIGNED.ALL;

entitycounteris

Port(a:

instd_logic_vector(3downto0);

load:

instd_logic;

reset:

instd_logic;

count:

outstd_logic_vector(3downto0);

clk:

instd_logic);

endcounter;

architectureBehavioralofcounteris

begin

process(reset,clk)

ifreset='1'thencount='0000'

elsifclk'eventandclk='1'then

begin

ifload='1'thencount<=a;

elsifcount>'1001'thencount<='0000';

elsecount=count+1;

endif;

endif;

endprocess;

endBehavioral;

3、设计一个带进位位的8位二进制全加器电路。

参考程序:

libraryIEEE;

useIEEE.STD_LOGIC_1164.ALL;

useIEEE.STD_LOGIC_ARITH.ALL;

useIEEE.STD_LOGIC_UNSIGNED.ALL;

entityadd8is

Port(a:

instd_logic_vector(0to7);

b:

instd_logic_vector(0to7);

ci:

instd_logic;

cout:

outstd_logic;

sum:

outstd_logic_vector(0to7));

endadd8;

architectureBehavioralofadd8is

variabletmp:

std_logic_vector(0to8);

begin

process(a,b)

begin

tmp:

='0'&a+'0'&b;

tmp:

=tmp+ci;

cout<=tmp(8);

sum<=tmp(7:

0);

endprocess;

endBehavioral;

异步复位和并行置位的左移一位寄存器

1.libraryIEEE;

2.useIEEE.STD_LOGIC_1164.all;

3.entityLshifteris

4.Port(clk,rst,load:

instd_logic;

5.din:

instd_logic_vector(7downto0);

6.qb:

outstd_logic);

7.endLshifter;

8.architectureart1ofLshifteris

9.Begin

10.Process(clk,rst,load)

11.Variablereg8:

std_logic_vector(7downto0);

12.Begin

13.Ifload=’1’thenreg8:

=(others=’0’);

14.IFCLK’EVENTANDCLK=’1’THEN

15.Ifload=’1’thenreg8:

=din;

16.Elsereg8(7downto1):

=reg8(6downto0);

17.Endif;

18.Endif;

19.QB<=REG8(7);

20.Endprocess;

21.endart1;

用VHDL语言实现一个3—8译码器

22.libraryIEEE;

23.useIEEE.STD_LOGIC_1164.ALL;

24.entityde3to8is

25.Port(inp:

instd_logic_vector(2downto0);

26.outp:

outstd_logic_vector(7downto0));

27.endde3to8;

28.architectureart3ofde3to8is

29.Begin

30.Caseinpis

31.Outp(0)<=’1’wheninp=“000”else’0’;

32.Outp

(1)<=’1’wheninp=“001”else’0’;

33.Outp

(2)<=’1’wheninp=“010”else’0’;

34.Outp(3)<=’1’wheninp=“011”else’0’;

35.Outp(4)<=’1’wheninp=“100”else’0’;

36.Outp(5)<=’1’wheninp=“101”else’0’;

37.Outp(6)<=’1’wheninp=“110”else’0’;

38.Outp(7)<=’1’wheninp=“111”else’0’;

39.Endcase;

40.endart3;

十进制数中六十进制加法计数器

41.libraryIEEE;

42.useIEEE.STD_LOGIC_1164.all;

43.useIEEE.STD_LOGIC_UNSIGNED.all;

44.entityCNT60is

45.Port(CLK,RST,EN:

inSTD_LOGIC;

46.CQ:

OUTSTD_LOGIC_vector(7downto0);

47.COUT:

OUTSTD_LOGIC);

48.endCNT60;

49.architectureBHVofCNT60is

50.SignalQ1:

STD_LOGIC_vector(7downto0);

51.Begin

52.Process(CLK,RST,EN)

53.VARIABLECQI:

STD_LOGIC_vector(7downto0);

54.VARIABLEHIGHCQI,LOWCQI:

STD_LOGIC_vector(3downto0);

55.Begin

56.IFRST=’1’THENCQI:

=(OTHERS=’0’);

57.HIGHCQI:

=CQI[7:

4];

58.LOWCQI:

=CQI[3:

0];

59.ELSIFCLK’EVENTANDCLK=’1’THEN

60.IFEN=’1’THEN

61.IFLOWCQI<’9’THENLOWCQI:

=LOWCQI+1;

62.ELSELOWCQI:

=(OTHERS=’0’);

63.HIGHCQI:

=HIGHCQI+1;

64.ENDIF;

65.IFHIGHCQI>=’5’THENCOUT<=’1’;

66.HIGHCQI:

=(OTHERS=’0’);

67.ENDIF;

68.ELSECOUT<=’0’;

69.ENDIF;

70.ENDIF;

71.ENDIF;

72.CQI:

=HIGHCQI&LOWCQI;

73.CQ<=CQI;

74.Endprocess;

75.endBHV

数码管

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYLED7SEGIS

PORT(A:

INSTD_LOGIC_VECTOR(3DOWNTO0);

CLK:

INSTD_LOGIC;

LED7S:

OUTSTD_LOGIC_VECTOR(6DOWNTO0));

ENDLED7SEG;

ARCHITECTUREoneOFLED7SEGIS

SIGNALTMP:

STD_LOGIC_VECTOR(3DOWNTO0);

BEGIN

SYNC:

PROCESS(CLK,A)

BEGIN

IFCLK'EVENTANDCLK='1'THEN

TMP<=A;

ENDIF;

ENDPROCESS;

OUTLED:

PROCESS(TMP)

BEGIN

CASETMPIS

WHEN"0000"=>L