FPGAverilog数字系统设计考试题.docx

《FPGAverilog数字系统设计考试题.docx》由会员分享,可在线阅读,更多相关《FPGAverilog数字系统设计考试题.docx(12页珍藏版)》请在冰豆网上搜索。

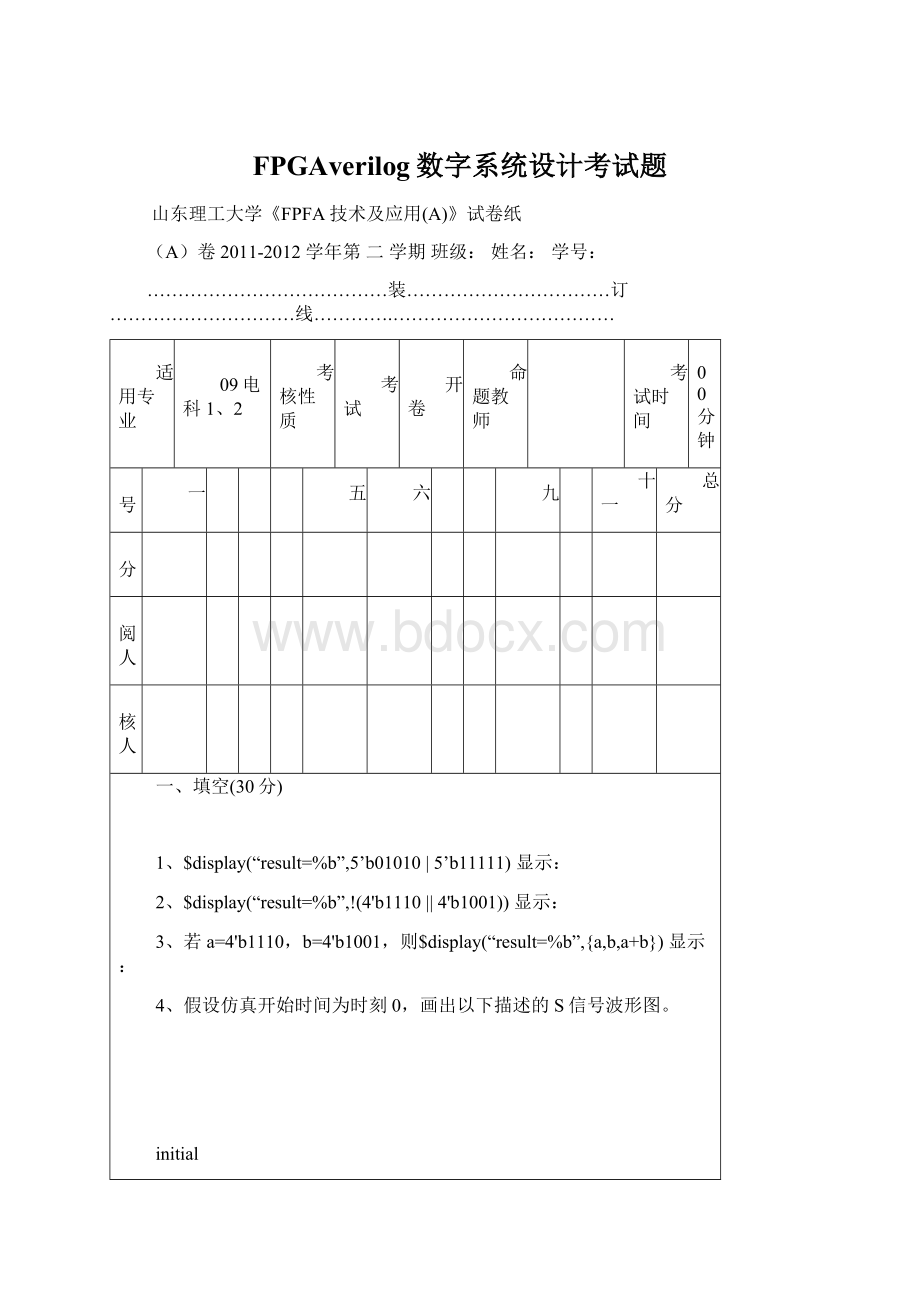

FPGAverilog数字系统设计考试题

山东理工大学《FPFA技术及应用(A)》试卷纸

(A)卷2011-2012学年第二学期班级:

姓名:

学号:

…………………………………装……………………………订…………………………线………….………………………………

适用专业

09电科1、2

考核性质

考试

开卷

命题教师

考试时间

100分钟

题号

一

二

三

四

五

六

七

八

九

十

十一

总分

得分

评阅人

复核人

一、填空(30分)

1、$display(“result=%b”,5’b01010|5’b11111)显示:

2、$display(“result=%b”,!

(4'b1110||4'b1001))显示:

3、若a=4'b1110,b=4'b1001,则$display(“result=%b”,{a,b,a+b})显示:

4、假设仿真开始时间为时刻0,画出以下描述的S信号波形图。

initial

begin

#2S=1;

#5S=0;

#3S=1;

#4S=0;

#2S=1;

#5S=0;

end

波形图:

5、写出仿真如下top_alu模块后屏幕上应显示的信息:

_________________________________

`timescale1ns/1ns

moduletop_alu;

wire[7:

0]out;

reg[2:

0]op;

reg[7:

0]d1,d2;

initial

begin

d1=8’h3e;

d2=8’h52;

op=3’b011;

#10$display(“ouput=%d”,out);

#10$stop;

end

alum(out,op,d1,d2);

endmodule

`defineplus3'd0

`defineminus3'd1

`defineband3'd2

`definebor3'd3

`defineunegate3'd4

modulealu(out,opcode,a,b);

output[7:

0]out;

input[2:

0]opcode;

input[7:

0]a,b;

reg[7:

0]out;

always@(opcodeoraorb)

begin

case(opcode)

`plus:

out=a+b;

`minus:

out=a-b;

`band:

out=a&b;

`bor:

out=a|b;

`unegate:

out=~a;

default:

out=8'hx;

endcase

end

endmodule

共4页第1页

山东理工大学《FPFA技术及应用(A)》试卷纸

(A)卷2011-2012学年第二学期班级:

姓名:

学号:

…………………………………装……………………………订…………………………线………….………………………………

二、根据功能模块写出Verilog描述(35分)

1、写出每个及连接在一起的逻辑功能模块Verilog描述(忽略逻辑部分)。

2、写出以下逻辑电路的门级结构Verilog描述和行为Verilog描述。

3、编写二、2逻辑电路的测试模块。

共4页第2页

山东理工大学《FPFA技术及应用(A)》试卷纸

(A)卷2011-2012学年第二学期班级:

姓名:

学号:

…………………………………装……………………………订…………………………线………….………………………………

三、根据要求设计逻辑电路(35分)

1.设计检测串行序列的逻辑电路,要求当检测到110时输出高电平脉冲。

画出状态图,写出verilog描述。

2.设计一能进行4、8分频的分频器,写出分频器和测试模块的Verilog描述。

共4页第3页

山东理工大学《FPFA技术及应用(A)》试卷纸

(A)卷2011-2012学年第二学期班级:

姓名:

学号:

…………………………………装……………………………订…………………………线………….………………………………

3、设计3位二进制码(Binary)到格雷码(Gray)的编码器,写出Verilog描述,码表如下:

二进制码(Binary)

格雷码(Gray)

000

000

001

001

010

011

011

010

100

110

101

111

110

101

111

100

共4页第4页

答案

一、填空(30分)

1、result=11111

2、result=0

3、result=111010010111

4、

5、output=126

说明:

每小题6分,共30分。

二、(35分)

1、

modulem(ena,out);

inputena;

wire[7:

0]data;

wirec;

outputout;

m1m1_inst(data,ena,c);

m2m2_inst(data,c,out);

endmodule

2、

3、

或

modulem31(clk,rst,x,z);

inputclk,rst,x;

outputz;

reg[1:

0]state;

parameteridle=2’b00,S0=2’b01,

S1=2’b10,S2=2’b11;

always@(posedgeclk)

if(rst)

state<=idle;

else

case(state)

Idle:

if(x)

state<=S0;

else

state<=idle;

S0:

if(x)

state<=S1;

else

state<=idle;

S1:

if(!

x)

state<=S2;

else

state<=S1;

S2:

if(x)

state<=S0;

else

state<=idle;

default:

state<=idle;

endcase

assignz=(state==S2)?

1’b1:

1’b0;

endmodule

答案不限上述两种,只要实现功能即可。

三、(35分)

1、

modulem32(clk,reset,clk4,clk8);

inputclk,reset;

outputclk4,clk8;

reg[2:

0]state;

parameterS0=3’b000,S1=3’b001,

S2=3’b010,S3=3’b011,

S4=3’b100,S5=3’b101,

S6=3’b110,S7=3’b111;

always@(posedgeclk)

if(reset)

state<=S0;

else

case(state)

S0:

state<=S1;

S1:

state<=S2;

S2:

state<=S3;

S3:

state<=S4;

S4:

state<=S5;

S5:

state<=S6;

S6:

state<=S7;

S7:

state<=S0;

default:

state<=S0;

endcase

assignclk4=(state==S0orstate==S1)?

1’b1:

1’b0;

assignclk8=(state==S0orstate==S1orstate==S2orstate==S3)?

1’b1:

1’b0;

endmodule

2、

`include“m32.v”

`timescale1ns/1ns

moduletest_m;

regclk,reset;

wireclk4,clk8;

initial

begin

reset=1;

clk=0;

#15reset=0;

#1000$stop;

end

always#10clk=~clk;

m32inst_m32(clk,reset,clk4,clk8);

endmodule

答案不限于上述描述,

以实现功能描述为准。

modulem33(din,dout);

input[2:

0]din;

output[2:

0]dout;

reg[2:

0]dout;

always@(din)

case(din)

3’b000:

dout=3’b000;

3’b001:

dout=3’b001;

3’b010:

dout=3’b011;

3’b011:

dout=3’b010;

3’b100:

dout=3’b110;

3’b101:

dout=3’b111;

3’b110:

dout=3’b101;

3’b111:

dout=3’b100;

default:

state<=3’bx;

endcase

endmodule

3、

WelcomeTo

Download!

!

!

欢迎您的下载,资料仅供参考!