嵌入式复习资料.docx

《嵌入式复习资料.docx》由会员分享,可在线阅读,更多相关《嵌入式复习资料.docx(15页珍藏版)》请在冰豆网上搜索。

嵌入式复习资料

1.嵌入式系统软件部分:

决定了硬件的操作模式。

通过良好的操作系统以及应用程序,把硬件功能发挥到极至。

嵌入式系统硬件部分:

决定了嵌入式系统的先天功能。

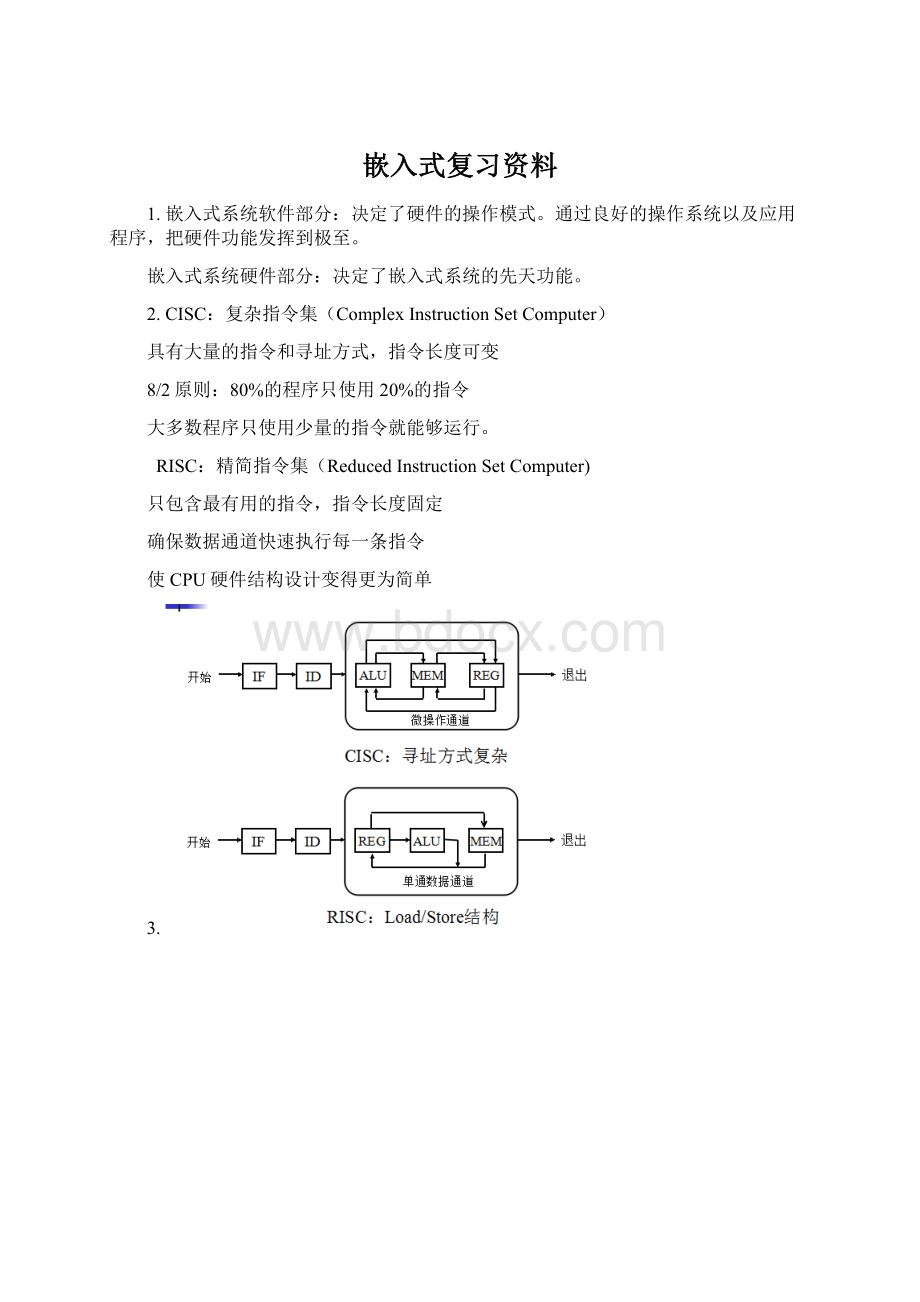

2.CISC:

复杂指令集(ComplexInstructionSetComputer)

具有大量的指令和寻址方式,指令长度可变

8/2原则:

80%的程序只使用20%的指令

大多数程序只使用少量的指令就能够运行。

RISC:

精简指令集(ReducedInstructionSetComputer)

只包含最有用的指令,指令长度固定

确保数据通道快速执行每一条指令

使CPU硬件结构设计变得更为简单

3.

4.

5.流水线(Pipeline)技术:

几个指令可以并行执行

(1)提高了CPU的运行效率

(2)内部信息流要求通畅流动

6.

(1)为增加处理器指令流的速度,ARM7系列使用3级流水线.

允许多个操作同时处理,比逐条指令执行要快。

(2)PC指向正被取指的指令,而非正在执行的指令

7.在AMBA总线规范中,定义了3种总线:

AHB(AdvancedHigh-performanceBus):

用于高性能系统模块的连接,支持突发模式数据传输和事务分割;可以有效地连接处理器、片上和片外存储器,支持流水线操作。

ASB(AdvancedSystemBus):

也用于高性能系统模块的连接,由AHB总线替代;

APB(AdvancedPeripheralBus):

用于较低性能外设的简单连接,一般是接在AHB或ASB系统总线上的第二级总线。

8.NOR技术闪速存储器是最早出现的FlashMemory,源于传统的EPROM器件。

与其它FlashMemory技术相比,具有可靠性高、随机读取速度快的优势。

在擦除和编程操作较少而直接执行代码的场合,尤其是代码(指令)存储的应用中广泛使用。

由于NOR技术FlashMemory的擦除和编程速度较慢,而块尺寸又较大,因此擦除和编程操作所花费的时间很长,在纯数据存储和文件存储的应用中,NOR技术显得力不从心。

1999年推出ARMv5TE其增强了Thumb体系,增强的Thumb体系增加了一个新的指令同时改进了Thumb/ARM相互作用、编译能力和混合及匹配ARM与Thumb例程,以更好地平衡代码空间和性能

并在ARMISA上扩展了增强的DSP 指令集:

增强的DSP指令包括支持饱和算术(saturatedarithmetic),并且针对AudioDSP应用提高了70%性能。

‘E’扩展表示在通用的CPU上提供DSP能力。

9.ARM内核是一种32位RISC微处理器,具有功耗低、性价比高、代码密度高等三大特色。

10.ARM体系结构的基本版本命名规则:

ARM{x}{y}{z}{T}{D}{M}{I}{E}{J}{F}{-S}

大括号内的字母是可选的,各个字母的含义如下:

x——系列号,例如ARM7中的“7”、ARM9中的“9”;

y——内部存储管理/保护单元,例如ARM72中的“2”、ARM94中的“4”;

z——内含有高速缓存Cache;

T——技持16位的Thumb指令集;

D——支持JTAG片上调试;

M——支持用于长乘法操作(64位结果)的ARM指令,包含快速乘法器;

I——带有嵌入式追踪宏单元ETM(EmbeddedTraceMacro),用来设置断点和观察点的调试硬件;

E——增强型DSP指令(基于TDMI);

J——含有Java加速器Jazelle,与Java虚拟机相比,Java加速器Jazelle使Java代码运行速度提高了8倍,功耗降低到原来的80%;

F——向量浮点单元;

S——可综合版本,意味着处理器内核是以源代码形式提供的。

这种源代码形式又可以被编译成一种易于EDA工具使用的形式。

11.Thumb在处理器中仍然要扩展为标准的32位ARM指令来运行。

用户采用16位Thumb指令集最大的好处就是可以获得更高的代码密度和降低功耗。

12.

ARM流水线

13.ARM处理器支持下列数据类型:

字节8位

半字16位(必须分配为占用两个字节)

字32位(必须分配为占用4各字节)

14.ARM处理器包含32位ARM指令集和16位Thumb指令集。

因此ARM处理器有两种操作状态:

ARM状态:

32位,这种状态下执行的是字方式的ARM指令;

Thumb状态:

16位,这种状态下执行半字方式的ARM指令。

注意:

使用BX指令将ARM内核的操作状态在ARM状态和Thumb状态之间进行切换,且两个状态之间的切换并不影响处理器模式或寄存器内容。

15.处理器7种模式

16.特权模式:

除用户模式外,其它模式均为特权模式。

ARM内部寄存器和一些片内外设在硬件设计上只允许特权模式下访问。

此外,特权模式可以自由的切换处理器模式,而用户模式不能直接切换到别的模式

17.异常模式:

快中断(fiq),中断(irq),管理(svc),中止(abt),未定义(und),这五种模式称为异常模式。

它们除了可以通过程序切换进入外,也可以由特定的异常进入。

当特定的异常出现时,处理器进入相应的模式。

每种异常模式都有一些独立的寄存器,以避免异常退出时用户模式的状态不可靠。

18.ARM处理器有37个寄存器

(1)31个通用32位寄存器:

程序计数器、堆栈及其他通用寄存器

(2)6个状态寄存器

注:

这些寄存器不能同时看到,不同的处理器状态和工作模式确定哪些寄存器是对编程者是可见的

19.用户和系统模式:

20.

注:

在汇编语言中寄存器R0~R13为保存数据或地址值的通用寄存器。

它们是完全通用的寄存器,不会被体系结构作为特殊用途,并且可用于任何使用通用寄存器的指令。

其中R0~R7为未分组的寄存器,也就是说对于任何处理器模式,这些寄存器都对应于相同的32位物理寄存器。

寄存器R8~R14为分组寄存器。

它们所对应的物理寄存器取决于当前的处理器模式,几乎所有允许使用通用寄存器的指令都允许使用分组寄存器

寄存器R8~R12有两个分组的物理寄存器。

一个用于除FIQ模式之外的所有寄存器模式,另一个用于FIQ模式。

这样在发生FIQ中断后,可以加速FIQ的处理速度。

寄存器R13、R14分别有6个分组的物理寄存器。

一个用于用户和系统模式,其余5个分别用于5种异常模式。

R13(也被称为SP指针)被用作堆栈指针,通常在系统初始化时需要对所有模式下的SP指针赋值,当CPU在不同的模式时栈指针会被自动切换成相应模式下的值

R14为链接寄存器(LR),在结构上有两个特殊功能:

在每种模式下,模式自身的R14用于保存子程序返回地址;

当发生异常时,将R14对应的异常模式版本设置为异常返回地址(有些异常有一个小的固定偏移量)。

寄存器R15为程序计数器(PC),它指向正在取指的地址。

可以认为它是一个通用寄存器,但是对于它的使用有许多与指令相关的限制或特殊情况。

如果R15使用的方式超出了这些限制,那么结果将是不可预测的。

正常操作时,从R15读取的值是处理器正在取指的地址,即当前正在执行指令的地址加上8个字节(两条ARM指令的长度)。

寄存器CPSR为当前程序状态寄存器,在异常模式中,另外一个寄存器“保护程序状态寄存器(SPSR)”可以被访问。

每种异常都有自己的SPSR,在进入异常时它保存CPSR的当前值,异常退出时可通过它恢复CPSR。

21.R14(LR)寄存器与子程序调用:

操作流程

R14寄存器与异常发生

异常发生时,程序要跳转至异常服务程序,对返回地址的处理与子程序调用类似,都是由硬件完成的。

区别在于有些异常有一个小常量的偏移。

注:

当发生异常嵌套时,这些异常之间可能会发生冲突。

IRQ服务程序A执行完毕,将R14_irq寄存器的内容减去某个常量后存入PC,返回之前被中断的程序;

22.Thumb状态寄存器与ARM状态寄存器有如下的关系:

Thumb状态R0~R7与ARM状态R0~R7相同;

Thumb状态CPSR和SPSR与ARM状态CPSR和SPSR相同;

Thumb状态SP映射到ARM状态R13;

Thumb状态LR映射到ARM状态R14;

Thumb状态PC映射到ARM状态PC(R15)

23.在Thumb状态中访问高寄存器:

在Thumb状态中,高寄存器(R8~R12)不是标准寄存器集的一部分。

但可用汇编程序受限制地访问这些寄存器,将其用作快速的暂存器。

程序状态寄存器

24.每个异常模式还带有一个程序状态保存寄存器(SPSR),它用于保存在异常发生之前的CPSR。

CPSR和SPSR通过特殊指令(MRS、MSR)进行访问。

Q位(27):

DSP的溢出/饱和。

在ARMV5及以上版本DSP扩展的ARM内核;

J位(24):

在有Jazelle扩展的处理器中,仅在5TEJ系列中有效,J位置位反映了内核处于Jazelle状态;

条件代码标志:

大多数“数值处理指令”可以选择是否影响条件代码标志位。

通常如果指令带S后缀,则该指令的执行会影响条件代码标志;但有一些指令的执行总是会影响条件代码标志。

N、Z、C和V位都是条件代码标志。

绝大多数ARM指令都可按条件来执行,而Thumb指令中只有分支指令可按条件执行。

V当进行加法/减法运算,并且发生有符号溢出时V=1,否则V=0,其它指令V通常不变。

控制位:

CPSR的最低8位为控制位,当发生异常时,这些位被硬件改变。

当处理器处于一个特权模式时,可用软件操作这些位。

包括:

中断禁止位,T位,模式位。

中断禁止位包括I和F位:

当I位为1时,IRQ中断被禁止;当F位为1时,FIQ中断被禁止。

T位反映了正在操作的状态:

当T位为1时,处理器正在Thumb状态下运行;当T位清零时,处理器正在ARM状态下运行。

模式位包括M4、M3、M2、M1和M0,这些位决定处理器的操作模式。

注意:

不是所有模式位的组合都定义了有效的处理器模式,如果使用了错误的设置,将引起一个无法恢复的错误。

25.

26.保留位:

CPSR中的保留位被保留将来使用。

为了提高程序的可移植性,当改变CPSR标志和控制位时,请不要改变这些保留位。

另外,请确保程序的运行不受保留位的值影响,因为将来的处理器可能会将这些位设置为1或者0。

27.异常是由内部或者外部原因引起的,当异常发生时CPU将暂停执行当前指令自动到指定的向量地址读取指令并且执行。

在X86上,当有异常发生时CPU是到指定的向量地址读取要执行的程序的地址

而ARM是到向量地址的地方读取指令,也就是ARM的向量地址处存放的是一条指令(一般是一条跳转指令)

28.进入异常:

在异常发生后,ARM内核会作以下工作:

1).在适当的LR中保存下一条指令的地址,当异常入口来自:

ARM状态,那么ARM将PC加4或加8复制(取决于异常的类型)到LR中;

为Thumb状态,那么ARM将PC加2、4或加8(取决于异常的类型)复制到LR中;异常处理器程序不必确定状态。

2).将CPSR复制到适当的SPSR中;

3).将CPSR模式位强制设置为与异常类型相对应的值;

4).强制PC从相关的异常向量处取指。

5).根据需要设置屏蔽中断和快速中断屏蔽位。

ARM内核在中断异常时置位中断禁止标志,这样可以防止不受控制的异常嵌套。

注:

异常总是在ARM状态中进行处理。

当处理器处于Thumb状态时发生了异常,在异常向量地址装入PC时,会自动切换到ARM状态。

29.退出异常:

当异常结束时,异常处理程序必须:

1).将LR(R14)中的值减去偏移量后存入PC,偏移量根据异常的类型而有所不同;

2).将SPSR的值复制回CPSR;

3).清零在入口置位的中断禁止标志。

注:

恢复CPSR的动作会将T、F和I位自动恢复为异常发生前的值。

30.快速中断请求:

快速中断请求(FIQ)适用于对一个突发事件的快速响应,这得益于在ARM状态中,快中断模式有8个专用的寄存器可用来满足寄存器保护的需要(这可以加速上下文切换的速度)。

不管异常入口是来自ARM状态还是Thumb状态,FIQ处理程序都会通过执行下面的指令从中断返回:

SUBSPC,R14_fiq,#4

在一个特权模式中,可以通过置位CPSR中的F位来禁止FIQ异常。

31.中断请求:

中断请求(IRQ)异常是一个由nIRQ输入端的低电平所产生的正常中断(在具体的芯片中,nIRQ由片内外设拉低,nIRQ是内核的一个信号,对用户不可见)。

IRQ的优先级低于FIQ。

对于FIQ序列它是被屏蔽的。

任何时候在一个特权模式下,都可通过置位CPSR中的I位来禁止IRQ。

不管异常入口是来自ARM状态还是Thumb状态,IRQ处理程序都会通过执行下面的指令从中断返回:

SUBSPC,R14_irq,#4

32.中止:

中止发生在对存储器的访问不能完成时,中止包含两种类型:

预取中止发生在指令预取过程中

数据中止发生在对数据访问时

33.中止——预取指中止:

当发生预取中止时,ARM内核将预取的指令标记为无效,但在指令到达流水线的执行阶段时才进入异常。

如果指令在流水线中因为发生分支而没有被执行,中止将不会发生。

在处理中止的原因之后,不管处于哪种处理器操作状态,处理程序都会执行下面的指令恢复PC和CPSR并重试被中止的指令:

SUBSPC,R14_abt,#4

34.中止——数据中止:

当发生数据中止后,根据产生数据中止的指令类型作出不同的处理:

数据转移指令(LDR、STR)回写到被修改的基址寄存器。

中止处理程序必须注意这一点;

交换指令(SWP)中止好像没有被执行过一样(中止必须发生在SWP指令进行读访问时);

在修复产生中止的原因后,不管处于哪种处理器操作状态,处理程序都必须执行下面的返回指令,重试被中止的指令:

SUBSPC,R14_abt,#8

35.软件中断指令:

使用软件中断(SWI)指令可以进入管理模式,通常用于请求一个特定的管理函数。

SWI处理程序通过执行下面的指令返回:

MOVSPC,R14_svc

这个动作恢复了PC并返回到SWI之后的指令。

SWI处理程序读取操作码以提取SWI函数编号。

36.未定义的指令:

当ARM处理器遇到一条自己和系统内任何协处理器都无法处理的指令时,ARM内核执行未定义指令陷阱。

软件可使用这一机制通过模拟未定义的协处理器指令来扩展ARM指令集。

注:

ARM处理器完全遵循ARM结构v4T,可以捕获所有分类未被定义的指令位格式。

在模拟处理了失败的指令后,陷阱程序执行下面的指令:

MOVSPC,R14_und

这个动作恢复了PC并返回到未定义指令之后的指令。

38.异常优先级:

当多个异常同时发生时,一个固定的优先级系统决定它们被处理的顺序:

37.异常向量:

注:

表中的I和F表示不对该位有影响,保留原来的值。

高向量地址:

0xFFFF0000~0xFFFF001C实现定义

39.复位:

当nRESET信号被拉低时(一般外部复位引脚电平的变化和芯片的其它复位源会改变这个内核信号),ARM处理器放弃正在执行的指令。

在复位后,除PC和CPSR之外的所有寄存器的值都不确定。

当nRESET信号再次变为高电平时,ARM处理器执行下列操作:

1.强制CPSR中的M[4:

0]变为b10011(管理模式);

2.置位CPSR中的I和F位;

3.清零CPSR中的T位;

4.强制PC从地址0x00开始对下一条指令进行取指。

40.ARM的寻址空间是线性的地址空间,为232=4G

41.ARM支持大端(Big-endian)和小端(Little-endian)的内存数据方式,可以通过硬件的方式设置(没有提供软件的方式)端模式

42.大端的数据存放格式:

worda=0xf6734bcd

最高有效字节位于最低地址,最高有效字节的地址就是该word的地址

小端的数据格式:

worda=0xf6734bcd

最低有效字节的地址就是该word的地址,最低有效字节位于最低地址

43.

44.

ARM的I/O端口都是内存映射的方式,即对I/O端口的访问与内存的访问的方式完全一样。

通常将I/O所映射的存储系统标识为非高速缓存(uncachable)和非缓冲(unbufferable)。

{(...)Bytes0to3存储第一个word,bytes4to7存储第二个word}

ARMv7定义了3种不同的处理器配置(processorprofiles):

ProfileA是面向复杂、基于虚拟内存的OS和用户应用

ProfileR是针对实时系统的

ProfileM是针对低成本应用的优化的微控制器的。

所有ARMv7profiles实现Thumb-2技术,同时还包括了NEON™技术的扩展提高DSP和多媒体处理吞吐量400% ,并提供浮点支持以满足下一代3D图形和游戏以及传统嵌入式控制应用的需要。