FPGA代码.docx

《FPGA代码.docx》由会员分享,可在线阅读,更多相关《FPGA代码.docx(69页珍藏版)》请在冰豆网上搜索。

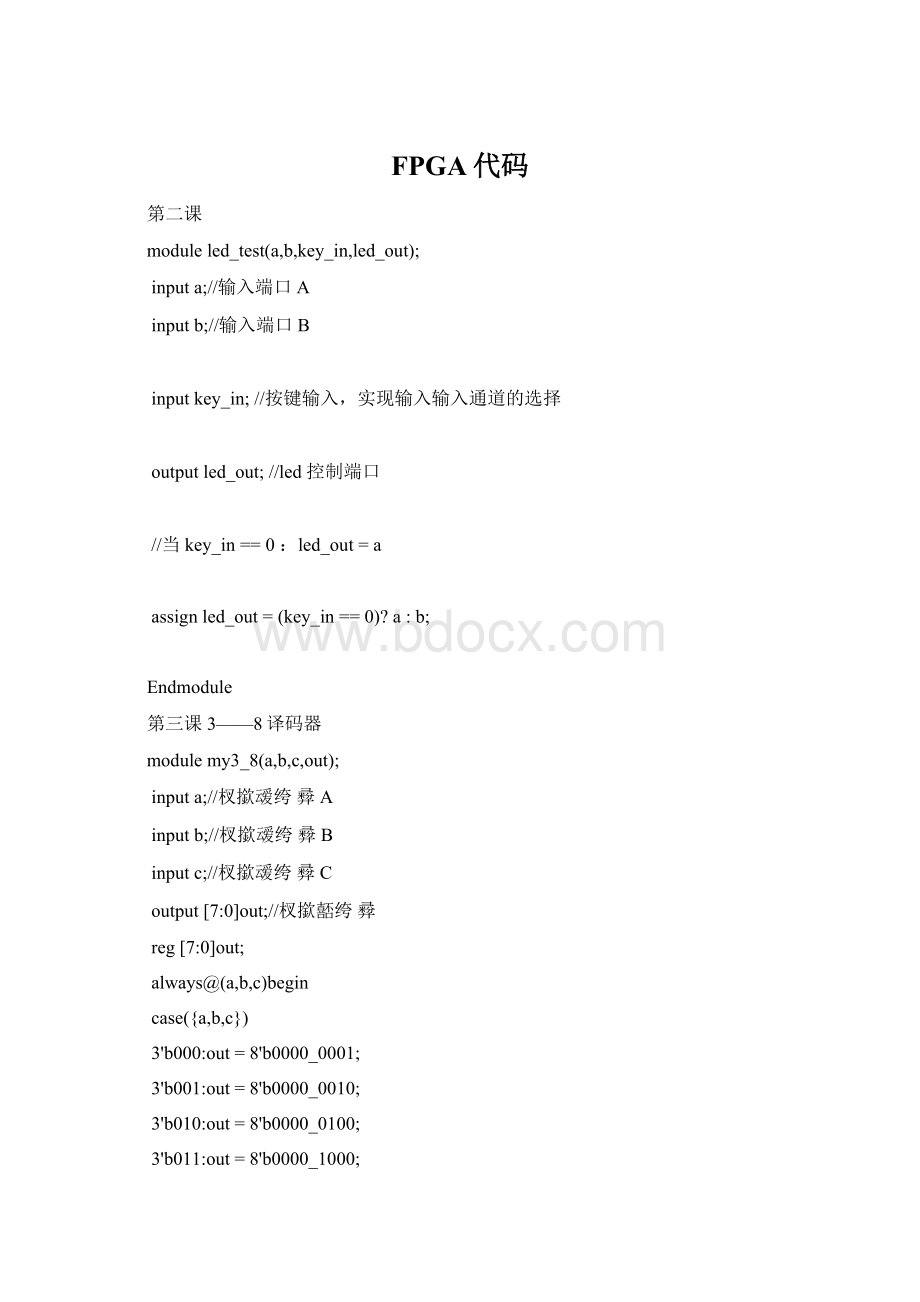

FPGA代码

第二课

moduleled_test(a,b,key_in,led_out);

inputa;//输入端口A

inputb;//输入端口B

inputkey_in;//按键输入,实现输入输入通道的选择

outputled_out;//led控制端口

//当key_in==0:

led_out=a

assignled_out=(key_in==0)?

a:

b;

Endmodule

第三课3——8译码器

modulemy3_8(a,b,c,out);

inputa;//杈撳叆绔彛A

inputb;//杈撳叆绔彛B

inputc;//杈撳叆绔彛C

output[7:

0]out;//杈撳嚭绔彛

reg[7:

0]out;

always@(a,b,c)begin

case({a,b,c})

3'b000:

out=8'b0000_0001;

3'b001:

out=8'b0000_0010;

3'b010:

out=8'b0000_0100;

3'b011:

out=8'b0000_1000;

3'b100:

out=8'b0001_0000;

3'b101:

out=8'b0010_0000;

3'b110:

out=8'b0100_0000;

3'b111:

out=8'b1000_0000;

endcase

end

endmodule

第四课计数器

modulecounter(Clk50M,Rst_n,led);

inputClk50M;//系统时钟,50M

inputRst_n;//全局复位,低电平复位

outputregled;//led输出

reg[24:

0]cnt;//定义计数器寄存器

//计数器计数进程

always@(posedgeClk50MornegedgeRst_n)

if(Rst_n==1'b0)

cnt<=25'd0;

//elseif(cnt==25'd24_999_999)

elseif(cnt==25'd24_999)

cnt<=25'd0;

else

cnt<=cnt+1'b1;

//led输出控制进程

always@(posedgeClk50MornegedgeRst_n)

if(Rst_n==1'b0)

led<=1'b1;

//elseif(cnt==25'd24_999_999)

elseif(cnt==25'd24_999)

led<=~led;

else

led<=led;

endmodule

第五课计数器——IP核

modulecounter_top(cin,clk,cout,q);

inputcin;

inputclk;

outputcout;

output[7:

0]q;

wirecout0;

countercounter0(

.cin(cin),

.clock(clk),

.cout(cout0),

.q(q[3:

0])

);

countercounter1(

.cin(cout0),

.clock(clk),

.cout(cout),

.q(q[7:

4])

);

endmodule

Testbench(仿真)

`timescale1ns/1ns

`defineclock_period20

modulecounter_tb;

regcin;//进位输入

regclk;//计数基准时钟

wirecout;//进位输出

wire[3:

0]q;

countercounter0(

.cin(cin),

.clock(clk),

.cout(cout),

.q(q)

);

initialclk=1;

always#(`clock_period/2)clk=~clk;

initialbegin

repeat(20)begin

cin=0;

#(`clock_period*5)cin=1;

#(`clock_period)cin=0;

end

#(`clock_period*200);

$stop;

end

Endmodule

top_ip

`timescale1ns/1ns

`defineclock_period20

modulecounter_top_tb;

regcin;//进位输入

regclk;//计数基准时钟

wirecout;//进位输出

wire[7:

0]q;

counter_topcounter0(

.cin(cin),

.clk(clk),

.cout(cout),

.q(q)

);

initialclk=1;

always#(`clock_period/2)clk=~clk;

initialbegin

repeat(300)begin

cin=0;

#(`clock_period*5)cin=1;

#(`clock_period)cin=0;

end

#(`clock_period*200);

$stop;

end

Endmodule

第六课BCD计数器

moduleBCD_Counter(Clk,Cin,Rst_n,Cout,q);

inputClk;//计数基准时钟

inputCin;//计数器进位输入

inputRst_n;//系统复位

outputCout;//计数进位输出

output[3:

0]q;//计数值输出

reg[3:

0]cnt;//定义计数器寄存器

//执行计数过程

always@(posedgeClkornegedgeRst_n)

if(Rst_n==1'b0)

cnt<=4'd0;

elseif(Cin==1'b1)begin

if(cnt==4'd9)

cnt<=4'd0;

else

cnt<=cnt+1'b1;

end

else

cnt<=cnt;

//产生进位输出信号

assignCout=(Cin==1'b1&&cnt==4'd9);

assignq=cnt;

Endmodule

Counter_Top

moduleBCD_Counter_top(Clk,Cin,Rst_n,Cout,q);

inputClk;//计数基准时钟

inputCin;//计数器进位输入

inputRst_n;//系统复位

outputCout;//计数进位输出

output[11:

0]q;//计数值输出

wireCout0,Cout1;

wire[3:

0]q0,q1,q2;

assignq={q2,q1,q0};

BCD_CounterBCD_Counter0(

.Clk(Clk),

.Cin(Cin),

.Rst_n(Rst_n),

.Cout(Cout0),

.q(q0)

);

BCD_CounterBCD_Counter1(

.Clk(Clk),

.Cin(Cout0),

.Rst_n(Rst_n),

.Cout(Cout1),

.q(q1)

);

BCD_CounterBCD_Counter2(

.Clk(Clk),

.Cin(Cout1),

.Rst_n(Rst_n),

.Cout(Cout),

.q(q2)

);

endmodule

仿真

`timescale1ns/1ns

`defineclock_period20

moduleBCD_Counter_tb;

regClk;

regCin;

regRst_n;

wireCout;

wire[3:

0]q;

BCD_CounterBCD_Counter0(

.Clk(Clk),

.Cin(Cin),

.Rst_n(Rst_n),

.Cout(Cout),

.q(q)

);

initialClk=1'b1;

always#(`clock_period/2)Clk=~Clk;

initialbegin

Rst_n=1'b0;

Cin=1'b0;

#(`clock_period*200);

Rst_n=1'b1;

#(`clock_period*20);

repeat(30)begin

Cin=1'b1;

#`clock_period;

Cin=1'b0;

#(`clock_period*5);

end

#(`clock_period*20);

$stop;

end

Endmodule

Top_仿真

`timescale1ns/1ns

`defineclock_period20

moduleBCD_Counter_top_tb;

regClk;

regCin;

regRst_n;

wireCout;

wire[11:

0]q;

BCD_Counter_topBCD_Counter_top0(

.Clk(Clk),

.Cin(Cin),

.Rst_n(Rst_n),

.Cout(Cout),

.q(q)

);

initialClk=1'b1;

always#(`clock_period/2)Clk=~Clk;

initialbegin

Rst_n=1'b0;

Cin=1'b0;

#(`clock_period*200);

Rst_n=1'b1;

#(`clock_period*20);

Cin=1'b1;

#(`clock_period*5000);

$stop;

end

endmodule

第七课阻塞与非阻塞

`timescale1ns/1ns

`definetp1

moduleblock_nonblock(Clk,Rst_n,a,b,c,out);

inputClk;

inputRst_n;

inputa,b,c;

outputreg[1:

0]out;

//out=a+b+c;

//d=a+b;

//out=d+c;

reg[1:

0]d;

always@(posedgeClkornegedgeRst_n)

if(!

Rst_n)

out<=2'b0;

elsebegin

out<=a+b+c;

end

endmodule

仿真

`timescale1ns/1ns

`defineclock_period20

moduleblock_nonblock_tb;

regClock;

regRst_n;

rega,b,c;

wire[1:

0]out;

block_nonblockblock_nonblock0(Clock,Rst_n,a,b,c,out);

initialClock=1;

always#(`clock_period/2)Clock=~Clock;

initialbegin

Rst_n=1'b0;

a=0;

b=0;

c=0;

#(`clock_period*200+1);

Rst_n=1'b1;

#(`clock_period*200);

a=0;b=0;c=0;

#(`clock_period*200);

a=0;b=0;c=1;

#(`clock_period*200);

a=0;b=1;c=0;

#(`clock_period*200);

a=0;b=1;c=1;

#(`clock_period*200);

a=1;b=0;c=0;

#(`clock_period*200);

a=1;b=0;c=1;

#(`clock_period*200);

a=1;b=1;c=0;

#(`clock_period*200);

a=1;b=1;c=1;

#(`clock_period*200);

#(`clock_period*200);

$stop;

end

Endmodule

第八课状态机

moduleHello(Clk,Rst_n,data,led);

inputClk;//50M

inputRst_n;//低电平复位

input[7:

0]data;

outputregled;

localparam

CHECK_H=5'b0_0001,

CHECK_e=5'b0_0010,

CHECK_la=5'b0_0100,

CHECK_lb=5'b0_1000,

CHECK_o=5'b1_0000;

reg[4:

0]state;

always@(posedgeClkornegedgeRst_n)

if(!

Rst_n)begin

led<=1'b1;

state<=CHECK_H;

end

elsebegin

case(state)

CHECK_H:

if(data=="H")

state<=CHECK_e;

else

state<=CHECK_H;

CHECK_e:

if(data=="e")

state<=CHECK_la;

else

state<=CHECK_H;

CHECK_la:

if(data=="l")

state<=CHECK_lb;

else

state<=CHECK_H;

CHECK_lb:

if(data=="l")

state<=CHECK_o;

else

state<=CHECK_H;

CHECK_o:

begin

state<=CHECK_H;

if(data=="o")

led<=~led;

else

led<=led;

end

default:

state<=CHECK_H;

endcase

end

endmodule

仿真

`timescale1ns/1ns

`defineclock_period20

moduleHello_tb;

regClk;

regRst_n;

reg[7:

0]ASCII;

wireled;

HelloHello0(

.Clk(Clk),

.Rst_n(Rst_n),

.data(ASCII),

.led(led)

);

initialClk=1;

always#(`clock_period/2)Clk=~Clk;

initialbegin

Rst_n=0;

ASCII=0;

#(`clock_period*200);

Rst_n=1;

#(`clock_period*200+1);

foreverbegin

ASCII="I";

#(`clock_period);

ASCII="A";

#(`clock_period);

ASCII="M";

#(`clock_period);

ASCII="X";

#(`clock_period);

ASCII="i";

#(`clock_period);

ASCII="a";

#(`clock_period);

ASCII="o";

#(`clock_period);

ASCII="M";

#(`clock_period);

ASCII="e";

#(`clock_period);

ASCII="i";

#(`clock_period);

ASCII="g";

#(`clock_period);

ASCII="e";

#(`clock_period);

ASCII="H";

#(`clock_period);

ASCII="E";

#(`clock_period);

ASCII="M";

#(`clock_period);

ASCII="l";

#(`clock_period);

ASCII="H";

#(`clock_period);

ASCII="E";

#(`clock_period);

ASCII="L";

#(`clock_period);

ASCII="L";

#(`clock_period);

ASCII="O";

#(`clock_period);

ASCII="H";

#(`clock_period);

ASCII="e";

#(`clock_period);

ASCII="l";

#(`clock_period);

ASCII="l";

#(`clock_period);

ASCII="o";

#(`clock_period);

ASCII="l";

end

end

Endmodule

第九课按键消抖

modulekey_filter(Clk,Rst_n,key_in,key_flag,key_state);

inputClk;

inputRst_n;

inputkey_in;

outputregkey_flag;

outputregkey_state;

localparam

IDEL=4'b0001,

FILTER0=4'b0010,

DOWN=4'b0100,

FILTER1=4'b1000;

reg[3:

0]state;

reg[19:

0]cnt;

regen_cnt;//浣胯兘璁℃暟瀵勫瓨鍣?

//瀵瑰閮ㄨ緭鍏ョ殑寮傛淇″彿杩涜鍚屾澶勭悊

regkey_in_sa,key_in_sb;

always@(posedgeClkornegedgeRst_n)

if(!

Rst_n)begin

key_in_sa<=1'b0;

key_in_sb<=1'b0;

end

elsebegin

key_in_sa<=key_in;

key_in_sb<=key_in_sa;

end

regkey_tmpa,key_tmpb;

wirepedge,nedge;

regcnt_full;//璁℃暟婊℃爣蹇椾俊鍙?

//浣跨敤D瑙﹀彂鍣ㄥ瓨鍌ㄤ袱涓浉閭绘椂閽熶笂鍗囨部鏃跺閮ㄨ緭鍏ヤ俊鍙凤紙宸茬粡鍚屾鍒扮郴缁熸椂閽熷煙涓級鐨勭數骞崇姸鎬?

always@(posedgeClkornegedgeRst_n)

if(!

Rst_n)begin

key_tmpa<=1'b0;

key_tmpb<=1'b0;

end

elsebegin

key_tmpa<=key_in_sb;

key_tmpb<=key_tmpa;

end

//浜х敓璺冲彉娌夸俊鍙?

assignnedge=!

key_tmpa&key_tmpb;

assignpedge=key_tmpa&(!

key_tmpb);

always@(posedgeClkornegedgeRst_n)

if(!

Rst_n)begin

en_cnt<=1'b0;

state<=IDEL;

key_flag<=1'b0;

key_state<=1'b1;

end

elsebegin

case(state)

IDEL:

begin

key_flag<=1'b0;

if(nedge)begin

state<=FILTER0;

en_cnt<=1'b1;

end

else

state<=IDEL;

end

FILTER0:

if(cnt_full)begin

key_flag<=1'b1;

key_state<=1'b0;

en_cnt<=1'b0;

state<=DOWN;

end

elseif(pedge)begin

state<=IDEL;

en_cnt<=1'b0;

end

else

state<=FILTER0;

DOWN:

begin

key_flag<=1'b0;

if(pedge)begin

state<=FILTER1;

en_cnt<=1'b1;