杭电数电实验课内题设计答案.docx

《杭电数电实验课内题设计答案.docx》由会员分享,可在线阅读,更多相关《杭电数电实验课内题设计答案.docx(29页珍藏版)》请在冰豆网上搜索。

杭电数电实验课内题设计答案

数字逻辑电路

课内仿真实验

第六章QuartusII原理图设计初步

一、实验目的:

初步了解学习使用Quartus||软件进行电路自动化设计。

二、实验仪器:

Quartus||软件。

三、实验内容:

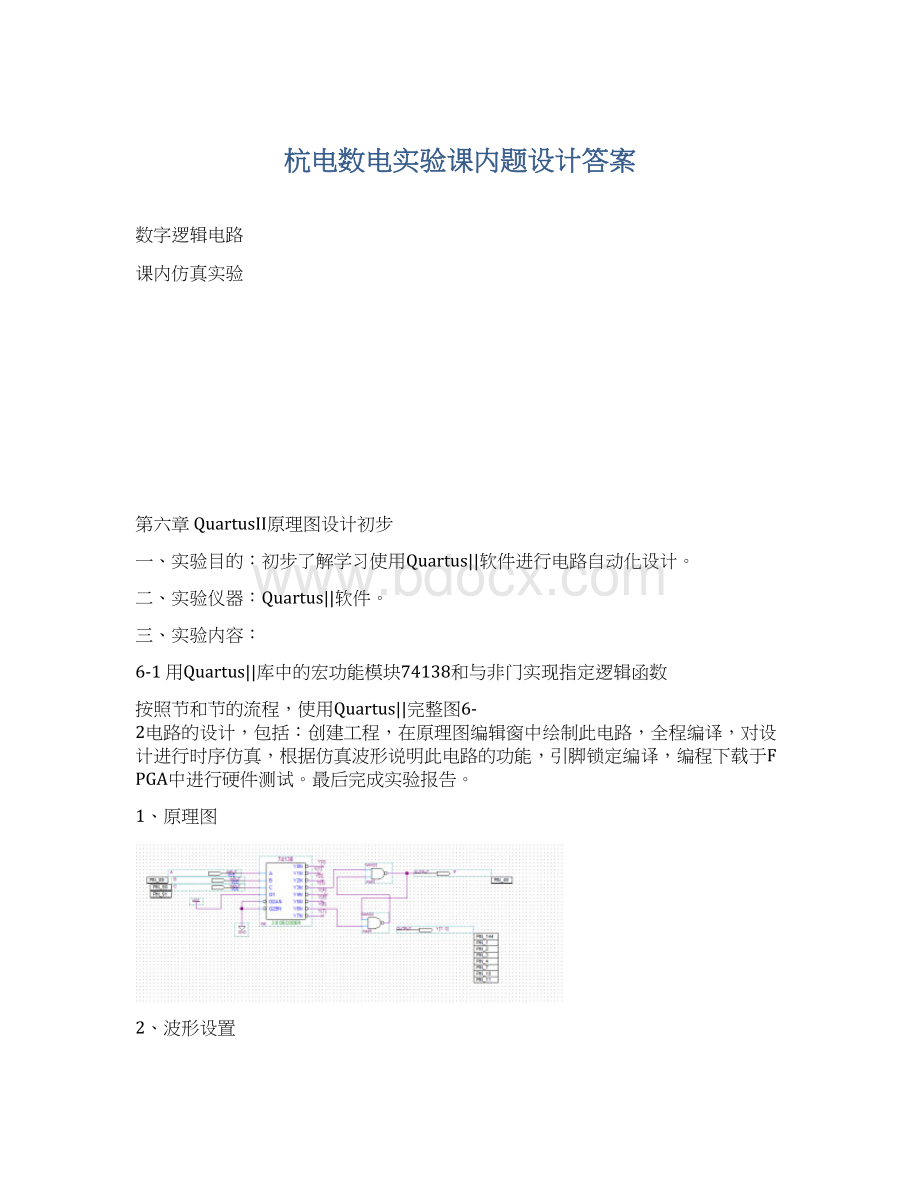

6-1用Quartus||库中的宏功能模块74138和与非门实现指定逻辑函数

按照节和节的流程,使用Quartus||完整图6-2电路的设计,包括:

创建工程,在原理图编辑窗中绘制此电路,全程编译,对设计进行时序仿真,根据仿真波形说明此电路的功能,引脚锁定编译,编程下载于FPGA中进行硬件测试。

最后完成实验报告。

1、原理图

2、波形设置

3、仿真波形

6-2用两片7485设计一个8位比较器

用两片4位二进制数值比较器7485串联扩展为8位比较器,使用Quartus||完成全部设计和测试,包括创建工程、编辑电路图、全程编译、时序仿真及说明此电路的功能、引脚锁定、编程下载,进行硬件测试。

最后完成实验报告。

1、原理图

2、波形设置

3、波形仿真

6-3设计8位串行进位加法器

首先根据图4-33,用半加器设计一个全加器元件,然后根据图4-34,在顶层设计中用8个1位全加器构成8位串行进位加法器。

给出时序仿真波形并说明之,引脚锁定编译,编程下载于FPGA中进行硬件测试,最后完成实验报告,讨论这个加法器的工作速度。

1、原理图:

半加器

1位全加器

8位串行进位全加器

集成后的8位串行进位全加器

2、波形设置

3、波形仿真

6-5设计一个十六进制7段显示译码器

用Verilog的case语句设计一个可以控制显示共阴7段数码管的十六进制码7段显示译码器。

首先给出此译码器的真值表,此译码器有4个输入端:

D、C、B、A。

D是最高位,A是最低位;输出有8位:

p、g、f、e、d、c、b、a,其中p和a分别是最高和最低位,p控制小数点。

对于共阴控制,如果要显示A,输入DCBA=1010;若小数点不亮,则输出pgfedcba=01110111=77H,给出时序仿真波形并说明之,引脚锁定,下载于FPGA中对共阴数码管进行硬件测试。

1、程序代码

2、电路原理图

3、波形设置

4、波形仿真

6-6设计一个5人表决电路

用case语句设计一个5人表决电路,参加表决者5人,同意为1,不同意为0,同意者过半则表决通过,绿指示灯亮;表决不通过则红指示灯亮。

给出时序仿真波形并说明之,引脚锁定,编程下载硬件测试。

最后完成实验报告。

1、程序代码

2、电路原理图

3、波形设置

4、波形仿真

第八章时序电路的自动化设计与分析

根据节,首先使用74390设计一个2位十进制计数器,然后使此计数器在新的工程中作为一个可调用的元件,用它构建一个8位十进制计数器。

给出仿真结果,最后在FPGA上进行硬件验证。

原理图:

波形仿真设置:

仿真波形:

原理图:

波形设置:

仿真波形:

根据节,用74161模块设计一个十二进制加法计数器,并注意计数器的可行性和可靠性考察;然后设计一个数控分频器。

利用Quartus||创建工程,绘制电路图,全程编译,时序仿真,并根据仿真波形作出说明,引脚锁定编译后下载FPGA中,在实验系统上硬件验证,完成实验报告。

原理图:

波形仿真设置:

仿真波形:

利用一般模型设计一个同步模7计数器,其状态图如图所示。

结合第6章介绍的Quartus||流程来实现。

原理图:

波形仿真设置:

仿真波形:

基于自动化设计方法的一般模型,设计一个模可控的同步加法计数器,要求当控制信号M=0时为六进制计数器,当M=1时为十二进制计数器。

原理图:

仿真波形设置:

波形仿真结果:

设计一个基于一般模型的十进制加法计数器,利用Quartus||创建工程,编辑电路图,时序仿真,并根据仿真波形作说明,在实验系统上硬件验证。

注意计数器的自启动问题。

原理图:

波形仿真设置:

仿真波形结果:

用自动设计技术完成基于计数器一般模型的可逆8位二进制计数器设计。

原理图:

波形仿真设置:

仿真波形结果:

根据节,完成基于LPM_COUNTER的16位可逆可预置型计数器设计。

利用Quartus||创建工程,时序仿真,在实验系统上硬件验证。

完成实验报告。

原理图:

波形仿真设置:

仿真波形结果:

根据节,用状态机5完成键触点消抖动电路的全部设计,对电路进行仿真。

在硬件验证中参考实验7-2给出的方法。

为了电路的可靠性,讨论状态机工作时时钟频率的最佳值。

仍然基于状态机,探寻更好更可靠的设计方案,并验证之。

原理图

波形仿真设置:

仿真波形结果:

根据节,首先完成此节的设计内容,并验证仿真结果。

针对系统中所需要的定时器,设计一个更灵活实用的定时器。

原理图:

波形仿真设置:

仿真波形结果:

用状态机设计一个序列发生器。

设序列发生器可周期性输出编码01,高位在前。

原理图

仿真波形设置:

波形仿真结果:

分频

IO找

引脚锁定

LOCATIOn

ClkPIN_22

PIN_596460有标志

Pin5855

Spk11143

下载

Tool

硬件

Quarter2drive安驱动

Setting设置对那个波形仿真