基于QuartusII的两种数字频率计的设计与比较.pdf

《基于QuartusII的两种数字频率计的设计与比较.pdf》由会员分享,可在线阅读,更多相关《基于QuartusII的两种数字频率计的设计与比较.pdf(2页珍藏版)》请在冰豆网上搜索。

福建电脑福建电脑2008年第6期福建电脑基于QuartusII的两种数字频率计的设计与比较曾永西(泉州师范学院理工学院福建泉州362000)【摘要】:

文中提出了基于QuartusII的两种数字频率计的设计与比较,分别采用原理图输入和VHDL文本输入两种设计方法,给出设计的部分代码,在QuartusII上对设计进行全程编译和仿真,并在ALTERA公司的FPGA器件EP1K30TC144-3上进行硬件下载验证,最后对两种设计进行比较,发现两种设计方法切实可行。

【关键词】:

QuartusII;数字频率计;VHDL语言;EDA0、引言数字频率计是电子设计、仪器仪表、资源勘测等应用领域不可缺少的测量仪器,不少物理量的测量,如振动、转速等的测量都涉及到或可以转化为频率的测量。

传统的数字频率计一般由分立元件组合而成,其测量范围、测量精度和测量速度均受到较大的限制。

单片机的发展与应用改善了这种情况13,但由于单片机本身也受到工作频率及内部计数器位数等因素的限制,所以无法在此领域取得突破性的进展。

随着大规模可编程逻辑器件技术的发展,能够将大量的逻辑功能集成于单个芯片中,根据不同的需要所提供的逻辑门数目可以从几百至上百万之多,从根本上解决了单片机的先天性限制问题。

在基准频率及精度等外部条件的允许下,根据不同场合的精度要求,对硬件描述语言作进一步的改动,可以较容易的使系统在性能上得到升级,从而降低系统的整体造价。

QuartusII是Altera公司推出的一款功能强大,兼容性最好的EDA工具软件。

该软件界面友好、使用便捷、功能强大,是一个完全集成化的可编程逻辑设计环境,具有开放性、与结构无关、多平台、完全集成化、丰富的设计库、模块化工具、支持多种硬件描述语言及有多种高级编程语言接口等特点4。

QuartusII支持原理图输入与VHDL输入混合设计,可以将VHDL设计文件包装成元件,通过原理图方式被调用,为设计者提供了极大的方便4。

文中在QuartusII开发环境下,运用原理图输入和VHDL输入两种设计方法对数字频率计进行设计,对两种设计分别在QuatrusII上进行全程编译和仿真,并通过GW48系列EDA实验开发系统在ALTERA公司的FPGA器件EP1K30TC144-3上进行硬件下载验证,最后对两种设计方法进行比较。

1、系统功能及分析设计一数字频率计,测量范围1Hz9999Hz,四位数码管显示测量值,能实现自动测频,并留有扩大测量范围的接口。

图1数字频率计系统框图一般数字频率计系统应包括输入整形电路、核心控制电路(FPGA模块)和输出显示电路,如图1所示。

被测信号经过输入整形电路生成方波输入到FPGA模块中进行计数处理,FPGA中的计数模块根据所提供方波的上升沿或下降沿进行计数,计数时间则由时间控制模块决定,可以根据频率所处的范围来决定档位,然后将计数的结果输出给显示电路,通过静态或动态扫描方式,在数码管上显示所测频率的大小。

文中所采用的GW48系列EDA实验开发系统含有较丰富的外围资源,可以充分利用其上所提供的各种时钟信号和输出数码管显示模块等外围资源,于是本文设计的重点就是核心控制电路模块。

核心控制电路模块由三大部分组成:

时间控制模块主要用来产生自动测频所需的计数、锁存和清零信号;计数模块是在计数允许信号有效的条件下,对经过整形后的方波信号进行计数,一般计数允许时间是1S,计数的结果直接反映信号的频率大小,如果对测频的反应速度有所要求,可以合理控制计数允许时间,再对计数结果进行相应的数学运算后再输出到显示模块;显示模块主要为输出显示电路提供稳定的显示数据,保证数码管不会由于周期性的清零信号而出现不断的闪烁的现象。

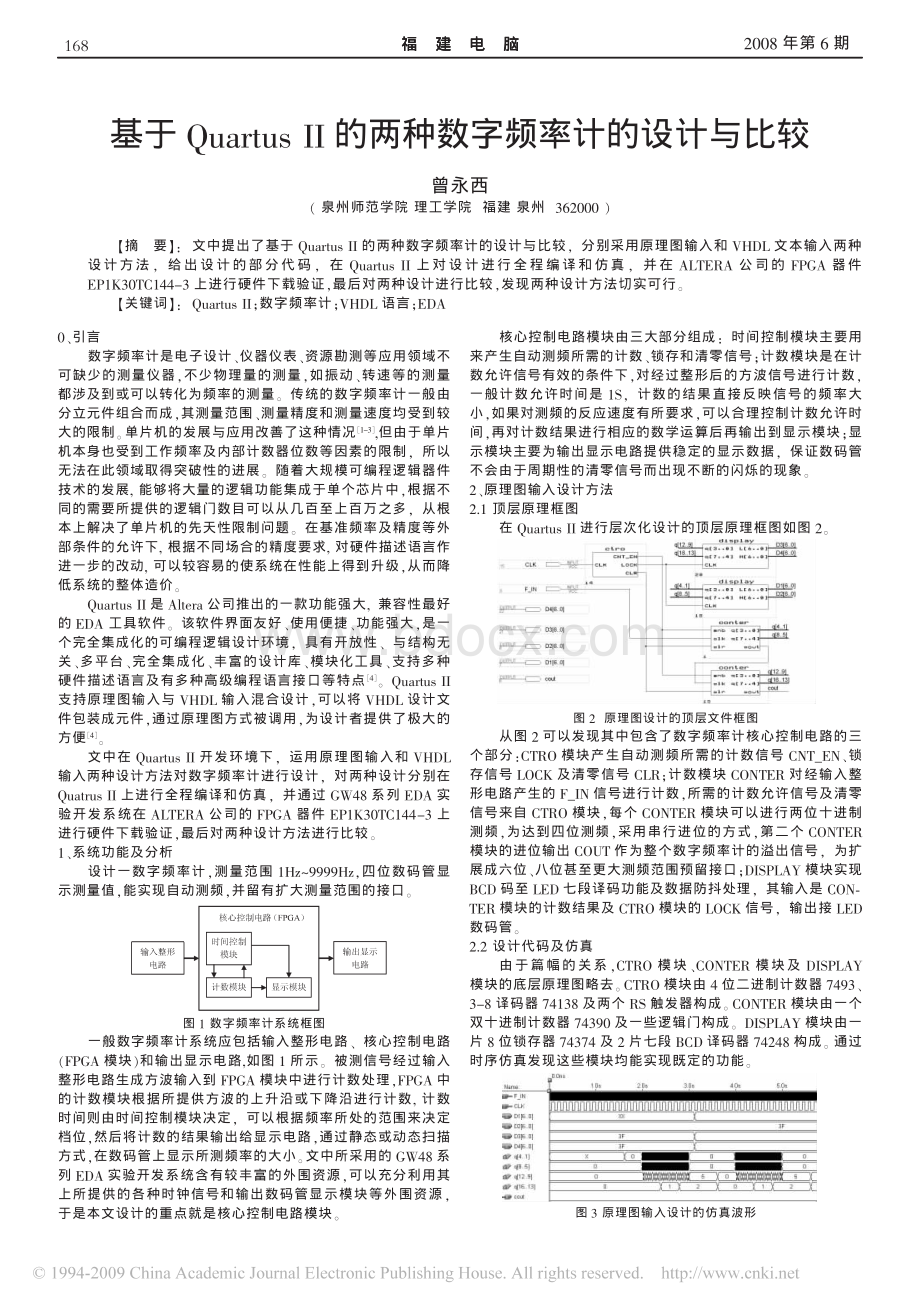

2、原理图输入设计方法2.1顶层原理框图在QuartusII进行层次化设计的顶层原理框图如图2。

图2原理图设计的顶层文件框图从图2可以发现其中包含了数字频率计核心控制电路的三个部分:

CTRO模块产生自动测频所需的计数信号CNT_EN、锁存信号LOCK及清零信号CLR;计数模块CONTER对经输入整形电路产生的F_IN信号进行计数,所需的计数允许信号及清零信号来自CTRO模块,每个CONTER模块可以进行两位十进制测频,为达到四位测频,采用串行进位的方式,第二个CONTER模块的进位输出COUT作为整个数字频率计的溢出信号,为扩展成六位、八位甚至更大测频范围预留接口;DISPLAY模块实现BCD码至LED七段译码功能及数据防抖处理,其输入是CON鄄TER模块的计数结果及CTRO模块的LOCK信号,输出接LED数码管。

2.2设计代码及仿真由于篇幅的关系,CTRO模块、CONTER模块及DISPLAY模块的底层原理图略去。

CTRO模块由4位二进制计数器7493、3-8译码器74138及两个RS触发器构成。

CONTER模块由一个双十进制计数器74390及一些逻辑门构成。

DISPLAY模块由一片8位锁存器74374及2片七段BCD译码器74248构成。

通过时序仿真发现这些模块均能实现既定的功能。

图3原理图输入设计的仿真波形168福建电脑2008年第6期福建电脑(上接第198页)!

养学生的创新意识和创新能力,并组织学生参加全国大学生电子大赛、数学建模大赛、齐鲁软件大赛等大型赛事。

建立了软件综合设计实验室、数字媒体创新实验室、数学建模实验室、电子设计与创新实验室等开放性实验室;同时安排有经验的骨干教师,针对各项大赛进行辅导,并注重学生之间的传帮带作用。

最终在学生中掀起了科技创新的良好学风,学生实践能力逐年稳步提高。

4总结总之,社会发展和经济建设需要适应型、应用型、创新型人才,提高人才的实践能力,保证学校培养出有用、合格的人才,加强实践教学环节至关重要。

计算机专业应不断加强实践教学体系建设,建立分层次、多模块的实验教学体系,提高学生综合素质,确保人才培养质量。

同时,实践教学体系的构建,必须有相应的课程体系作保障,应积极开展课程结构改革,改变单一、落后的学科型课程模式,代之以能力为本位的模块课程,将提高学生实践能力和全面素质系统地贯穿于教学过程中。

参考文献:

1.董维佳.高职院校实践教学多元拓展的理性思考J.黑龙江高教研究,2007(11):

169-171.2.尹德成,张森.对高职院校实践教学建设的几点思考J.中国成人教育,2007(20):

79-80.3.李元元,李正,徐向民.改革实践教学模式培养创新型工程人才J.中国高等教育,2006(23):

31-33.当输入信号F_IN的频率为2500Hz,基准时钟信号CLK为8Hz,CTRO模块产生的计数允许信号的脉宽为1秒,对顶层设计文件进行时序仿真,仿真波形如图3,从图3可以发现仿真所得到的输出是2500Hz,结果是完全正确的。

3、VHDL文本输入设计方法3.1顶层VHDL设计文件框图在QuartusII开发环境下,编写时间控制模块TEST_CTL、计数模块CNT10和显示控制模块REG16的VHDL代码,并利用VHDL语言中的元件例化语句,按照图4中各个模块的连接情况编写顶层设计文件的代码,其中进位输出CARRY_OUT作为整个数字频率计的溢出信号,为扩大测频范围预留接口。

图4VHDL文本输入设计的顶层文件框图3.2设计代码及仿真由于篇幅的关系,TEST_CTL模块、CNT10模块及REG16模块的VHDL代码略去。

其中TEST_CTL模块产生0.5Hz的周期信号作为计数允许信号TEST_EN,由于每个周期的高电平为1秒,故计数的结果直接显示被测信号的频率,本设计直接将TEXT_EN信号取反后作为锁存信号LOAD;REG16模块是16位的寄存器,对四个CNT10模块产生的四组信号进行锁存,使数码管显示的数据稳定,不会由于周期性的清零信号而不断的闪烁。

最后对采用VHDL文本输入设计的数字频率计进行全程编译和仿真,当输入信号F_IN的频率为2500Hz时,得到仿真波形如图5。

从图5可以发现仿真结果也是正确的。

图5VHDL文本输入设计的仿真波形4、两种设计方法的比较将以上通过原理图输入和VHDL文本输入两种方法设计的数字频率计在GW48系列EDA实验开发系统上进行硬件下载验证,选用的FPGA器件是Aletra公司ACEX1K系列的EP1K30TC144-3,下载模式为JTAG模式。

经硬件下载验证,发现两种方法设计的数字频率计均能正确的对输入信号进行测频,且数据显示稳定无闪烁,若将溢出接口接一指示灯,当超出测量范围时,指示灯会闪烁。

在本文中采用原理图输入方法设计的数字频率计共需要4个BDF文件,设计者不必学习新的知识,如硬件描述语言,因其设计方式与传统的电子设计方式是一样的,又由于其设计方式接近于底层电路布局,因此易于控制逻辑资源的耗用。

采用VHDL文本输入方法设计的数字频率计亦需要4个VHD文件,它可以充分利用VHDL语言的电路描述和建模能力,不必深入了解硬件情况,简化硬件设计任务,提高设计效率和可靠性,若编写得当,可以较有效的节省可编程逻辑器件的资源。

在QuartusII开发平台上,对两种方法设计的数字频率计分别进行全程编译,并对两种设计部分的编译结果进行比较如下:

选用相同系列相同型号的目标芯片,原理图输入设计的输入输出端口为31(占总端口数的30%),VHDL文本输入设计的输入输出端口为19(占总端口数的18%),由于两种设计在GW48系列EDA实验开发系统上选择不同的电路模式进行硬件仿真,故所需的I/O口可以不同;两种设计均没有占用芯片内部存储位;原理图输入设计方法耗用的逻辑阵列块为80个(占逻辑阵列块总数的4.5%),VHDL文本输入设计方法耗用的逻辑阵列块为46个(占逻辑阵列块总数的2.5%),可见采用VHDL文本输入设计方法耗用芯片的资源比较少,当系统规模较大时,这种节省资源的优势将更明显。

由于两种设计方案均能达到正确测频的要求,且目前一般的PLD器件内部资源均能满足数字频率计设计的需要,故在应用上两种方法都可行,如果从耗用资源的角度考虑,则应优先采用第二种设计方法。

5、结语基于QuartusII开发环境,运用原理图输入设计和VHDL文本输入设计两种方法设计数字频率计,在GW48系列EDA实验开发系统中进行硬件下载验证,发现两种设计方法切实可行。

文中给出了两种设计顶层设计文件的框图和部分波形仿真图,最后对两种设计进行比较,可以为采用PLD器件来设计数字频率计提供参考。

参考文献:

1.林晓焕,林刚.基于VHDL语言的数字频率计设计J.西安工程科技学报,2005,19(3):

321-324.2.张新安.基于单片机控制的高性能数字频率合成器的设计J.湖南科技学院学报,2007,28(9):

25-28.3.倪淑艳,李晓波,于涵.单片机C8051F303在数字锁相式频率合成器中的应用J.现代电子技术,2006,(8):

19-21.4.潘松,黄继业编著.EDA技术实用教程(第三版)M.科学出版社2006.169