组合逻辑电路 课后答案.docx

《组合逻辑电路 课后答案.docx》由会员分享,可在线阅读,更多相关《组合逻辑电路 课后答案.docx(27页珍藏版)》请在冰豆网上搜索。

组合逻辑电路课后答案

第4章

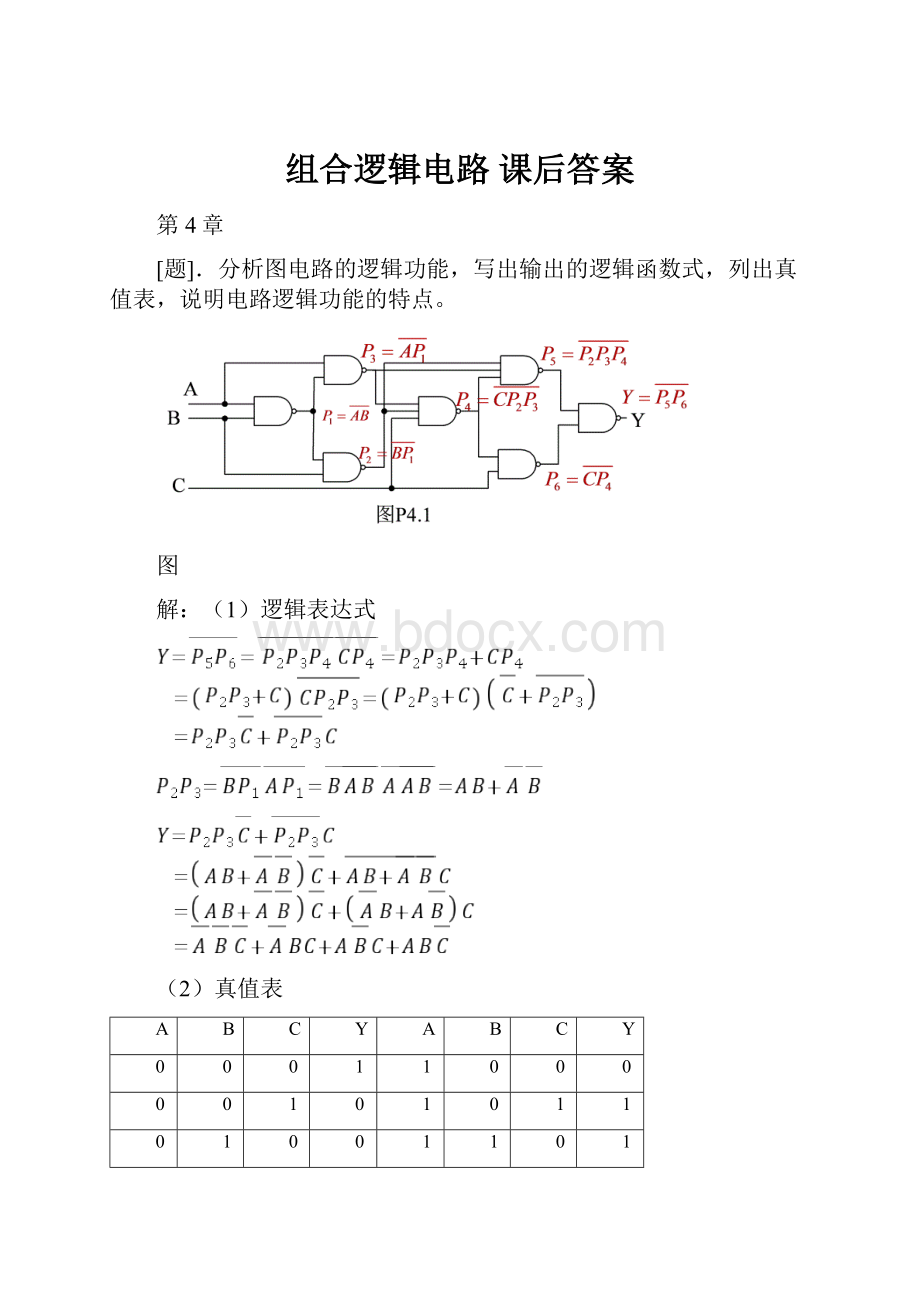

[题].分析图电路的逻辑功能,写出输出的逻辑函数式,列出真值表,说明电路逻辑功能的特点。

图

解:

(1)逻辑表达式

(2)真值表

A

B

C

Y

A

B

C

Y

0

0

0

1

1

0

0

0

0

0

1

0

1

0

1

1

0

1

0

0

1

1

0

1

0

1

1

1

1

1

1

0

(3)功能

从真值表看出,这是一个三变量的奇偶检测电路,当输入变量中有偶数个1和全为0时,Y=1,否则Y=0。

[题]分析图电路的逻辑功能,写出Y1、、Y2的逻辑函数式,列出真值表,指出电路完成什么逻辑功能。

[解]

解:

真值表:

ABC

Y1Y2

000

00

001

10

010

10

011

01

100

10

101

01

110

01

111

11

由真值表可知:

电路构成全加器,输入A、B、C为加数、被加数和低位的进位,Y1为“和”,Y2为“进位”。

[题]图是对十进制数9求补的集成电路CC14561的逻辑图,写出当COMP=1、Z=0、和COMP=0、Z=0时,Y1~Y4的逻辑式,列出真值表。

[解]

(1)COMP=1、Z=0时,TG1、TG3、TG5导通,TG2、TG4、TG6关断。

,

(2)COMP=0、Z=0时,

Y1=A1,Y2=A2,Y3=A3,Y4=A4。

、COMP=1、Z=0时的真值表

十进制数

A4A3A2A1

Y4Y3Y2Y1

十进制数

A4A3A2A1

Y4Y3Y2Y1

0

0000

1001

8

1000

0001

1

0001

1000

9

1001

0000

2

0010

0111

伪

码

1010

0111

3

0011

0110

1011

0110

4

0100

0101

1100

0101

5

0101

0100

1101

0100

6

0110

0011

1110

0011

7

0111

0010

1111

0010

COMP=0、Z=0的真值表从略。

[题]用与非门设计四变量的多数表决电路。

当输入变量A、B、C、D有3个或3个以上为1时输出为1,输入为其他状态时输出为0。

[解]题的真值表如表所示,逻辑图如图(b)所示。

由表可写输出逻辑函数式

填卡诺图,如图(a)所示合并最小项,得最简与—或式

[题]有一水箱由大、小两台泵ML和MS供水,如图所示。

水箱中设置了3个水位检测元件A、B、C。

水面低于检测元件时,检测元件给出高电平;水面高于检测元件时,检测元件给出低电平。

现要求当水位超过C点时水泵停止工作;水位低于C点而高于B点时MS单独工作;水位低于B点而高于A点时ML单独工作;水位低于A点时ML和MS同时工作。

试用门电路设计一个控制两台水泵的逻辑电路,要求电路尽量简单。

[解]题的真值表如表所示。

表

ABC

MSML

000

00

001

10

010

××

011

01

100

××

101

××

110

××

111

11

真值表中的、、、为约束项,利用卡诺图图(a)化简后得到:

,

(MS、ML的1状态表示工作,0状态表示停止)。

逻辑图如图(b)。

[题]设计一个代码转换电路,输入为4位二进制代码,输出为4位循环码。

可以采用各种逻辑功能的门电路来实现。

[解]题的真值表如表所示。

表

二进制代码

循环码

二进制代码

循环码

A3

A2

A1

A0

Y3

Y2

Y1

Y0

A3

A2

A1

A0

Y3

Y2

Y1

Y0

0

0

0

0

0

0

0

0

1

0

0

0

1

1

0

0

0

0

0

1

0

0

0

0

1

0

0

1

1

1

0

1

0

0

1

0

0

0

1

1

1

0

1

0

1

1

1

1

0

0

1

1

0

0

1

0

1

0

1

1

1

1

1

0

0

1

0

0

0

1

1

0

1

1

0

0

1

0

1

0

0

1

0

1

0

1

1

1

1

1

0

1

1

0

1

1

0

1

1

0

0

1

0

1

1

1

1

0

1

0

0

1

0

1

1

1

0

1

0

0

1

1

1

1

1

0

0

0

由真值表得到,,,

逻辑图如图所示。

[题]试画出用4片8线-3线优先编码器74LS148组成32线-5线优先编码器的逻辑图。

74LS148的逻辑图见图。

允许附加必要的门电路。

[解]以表示32个低电平有效的编码输入信号,以D4D3D2D1D0表示输出编码,可列出D4、D3与YEX4YEX3YEX2YEX1关系的真值表。

如表所示。

表

工作的芯片号

YEX4

YEX3

YEX2

YEX1

D4

D3

(4)

1

0

0

0

1

1

(3)

0

1

0

0

1

0

(2)

0

0

1

0

0

1

(1)

0

0

0

1

0

0

从真值表得到

逻辑电路图略。

[题]某医院有一、二、三、四号病室4间,每室设有呼叫按钮,同时在护士值班室内对应地装有一号、二号、三号、四号4个指示灯。

现要求当一号病室的铵钮按下时,无论其他病室内的按钮是否按下,只有一号灯亮。

当一号病室的按钮没有按下,而二号病室的按钮按下时,无论三、四号病室的按钮是否按下,只有二号灯亮。

当一、二号病室的按钮都未按下而三号病室的按钮按下时,无论四号病室的铵钮是否按下,只有三号灯亮。

只有在一、二、三号病室的按钮均未按下,而四号病室的按钮按下时,四号灯才亮。

试分别用门电路和优先编码器74LS148及门电路设计满足上述控制要求的逻辑电路,给出控制四个指示灯状态的高、低电平信号。

74LS148的逻辑图如图所示,其功能表如表所示。

输入

输出

1

0

0

0

0

0

0

0

0

0

××××××××

11111111

×××××××0

××××××01

×××××011

××××0111

×××01111

××011111

×0111111

01111111

111

111

000

001

010

011

100

101

110

111

11

01

10

10

10

10

10

10

10

10

表74LS148的功能表

[解]

设一、二、三、四号病室分别为输入变量

,当其值为0时,表示呼叫按钮按下,为1时表示没有按呼叫铵钮,将它们接到74HC148的

输入端后,便在74HC148的输出端

得到对应的输出编码;设一、二、三、四号病室呼叫指示灯分别为Z1、Z2、Z3、Z4,其值为1指示灯亮,否则灯不亮,列出真值表,如表示。

表

Z1Z2Z3Z4

0×××

1001

1000

10××

1011

0100

110×

1101

0010

1110

1111

0001

1111

1110

0000

将该真值表与表对照可知,在74LS148中

应接1,

。

则

由上式可得出用74LS148和门电路实现题目要求的电路如图所示。

[题]写出图中Z1、Z2、Z3的逻辑函数式,并化简为最简的与-或表达式。

74LS42为拒伪的二-十进制译码器。

当输入信号A3A2A1A0为0000~1001这10种状态时,输出端从依次给出低电平,当输入信号为伪码时,输出全为1。

[解]

利用伪码用卡诺图化简,得:

约束条件:

[题]画出用两片4线-16线译码器74LS154组成5线-32线译码的接线图。

图是74LS154的逻辑框图,图中是两个控制端(亦称片选端)译码器工作时应使同时为低电平,输入信号A3、A2、A1、A0为0000~1111这16种状态时,输出端从依次给出低电平输出信号。

[解]电路如图所示。

当A4=0时,片

(1)工作,对应输出低电平;当A4=1时,片

(2)工作,对应输出低电平。

[题]试画出用3线-8线译码器74LS138和门电路产生多输出逻辑函数的逻辑图(74LS138逻辑图如图所示,功能表如表所示)。

表74LS138功能表

输入

输出

允许

选择

A2

A1

A0

×

1

×

×

×

1

1

1

1

1

1

1

1

0

×

×

×

×

1

1

1

1

1

1

1

1

1

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

1

1

0

1

1

1

1

1

1

1

0

0

1

0

1

1

0

1

1

1

1

1

1

0

0

1

1

1

1

1

0

1

1

1

1

1

0

1

0

0

1

1

1

1

0

1

1

1

1

0

1

0

1

1

1

1

1

1

0

1

1

1

0

1

1

0

1

1

1

1

1

1

0

1

1

0

1

1

1

1

1

1

1

1

1

1

0

[解]令A=A2,B=A1,C=AO。

将Y1Y2Y3写成最小项之和形式,并变换成与非-与非形式。

用外加与非门实现之,如图所示。

[题]画出用4线-16线译码器74LS154(参见题)和门电路产生如下多输出逻辑函数的逻辑图。

[解]

电路图如图所示。

[题]用3线-8线译码器74LS138和门电路设计1位二进制全减器电路。

输入为被减数、减数和来自低位的借位;输出为两数之差及向高位的借位信号。

[解]设ai为被减数,bi为减数,ci-1为来自低位的借位,

首先列出全减器真值表,然后将Di,Ci表达式写成非-与非形式。

最后外加与非门实现之。

由全减器真值表知:

全减器真值表

同理可知

令ai=A2,bi=A1,ci-1=A0。

电路如图所示。

[题]试用两片双4选1数据选择器74LS153和3线-8线译码器74LS138接成16选1数据选择器。

74LS153的逻辑图见图,74LS138的逻辑图见图。

[解]见图。

[题]分析图电路,写出输出Z的逻辑函数式,并化简。

CC4512为8选1数据选择器,它的逻辑功能表如表所示。

表CC4512的功能表

[解]

=

[题]图是用两个4选1数据选择器组成的逻辑电路,试写出输出Z与输入M、N、P、Q之间的逻辑函数。

已知数据选择器的逻辑函数式为

[解]

[题]试用4选1数据选择器74LS153产生逻辑函数

[解]4选1数据选择器表达式为:

而所需的函数为

与4选1数据选择器逻辑表达式比较,则令

,

接线图如图所示。

[题]用8选1数据选择器74HC151(参见图)产生逻辑函数

[解]令A=A2,B=A1,C=A0,D=D0~D7,将Y写成最小项之和的形式,找出与8选1数据选择器在逻辑上的对应关系,确定D0~D7所接信号。

则

如图所示。

[题]用8选1数据选择器74HC151(参见图)产生逻辑函数

[解]将Y变换成最小项之和形式。

令A=A2,B=A1,C=A0,

凡Y中含有的最小项,其对应的Di接1,否则接0。

如图所示。

[题]设计用3个开关控制一个电灯的逻辑电路,要求改变任何一个开关的状态都控制电灯由亮变灭或由灭变亮。

要求用数据选择器来实现。

[解]以A、B、C表示三个双位开关,并用0和1分别表示开关的两个状态。

以Y表示灯的状态,用1表示亮,用0表示灭。

设ABC=000时Y=0,从这个状态开始,单独改变任何一个开关的状态Y的状态要变化。

据此列出Y与A、B、C之间逻辑关系的真值表。

如表所示。

表

A

B

C

Y

A

B

C

Y

0

0

0

0

0

1

1

0

0

0

1

1

1

0

1

0

0

1

0

1

1

1

0

0

1

0

0

1

1

1

1

1

从真值表写出逻辑式

取4选1数据选择器,令A1=A,A0=B,D0=D3=C,D1=D2=,即得图。

[题]人的血型有A、B、AB、O四种。

输血时输血者的血型与受血者血型必须符合图中用箭头指示的授受关系。

试用数据选择器设计一个逻辑电路,判断输血者与受血者的血型是否符合上述规定。

(提示:

可以用两个逻辑变量的4种取值表示输血者的血型,用另外两个逻辑变量的4种取值表示受血者的血型。

)

[解]以MN的4种状态组合表示输血者的4种血型,并以PQ的4种状态组合表示受血者的4种血型,如图(a)所示。

用Z表示判断结果,Z=0表示符合图(a)要求,Z=1表示不符合要求。

据此可列出表示Z与M、N、P、Q之间逻辑关系的真值表。

从真值表写出逻辑式为

其真值表如表所示。

表

M

N

P

Q

Z

M

N

P

Q

Z

0

0

0

0

0

1

0

0

0

1

0

0

0

1

1

1

0

0

1

1

0

0

1

0

0

1

0

1

0

0

0

0

1

1

1

1

0

1

1

1

0

1

0

0

1

1

1

0

0

0

0

1

0

1

0

1

1

0

1

0

0

1

1

0

0

1

1

1

0

0

0

1

1

1

1

1

1

1

1

0

令A2=M,A1=N,A0=P,并使D0=D1=D3=D5=Q,D2=,D4=1,D6=D7=0,则得到图(b)电路。

[题]用8选数据选择器74HC151(参见图)设计一个组合逻辑电路。

该电路有3个输入逻辑变量A、B、C和1个工作状态控制变量M。

当M=0时电路实现“意见一致”功能(A、B、C状态一致时输出为1,否则输出为0),而M=1时电路实现“多数表决”功能,即输出与A、B、C中多数的状态一致。

[解]根据题意可列出真值表,如表所示。

以Z表示输出。

表

M

A

B

C

Z

M

A

B

C

Z

0

0

0

0

1

1

0

0

0

0

0

0

0

1

0

1

0

0

1

0

0

0

1

0

0

1

0

1

0

0

0

0

1

1

0

1

0

1

1

1

0

1

0

0

0

1

1

0

0

0

0

1

0

1

0

1

1

0

1

1

0

1

1

0

0

1

1

1

0

1

0

1

1

1

1

1

1

1

1

1

由真值表写出逻辑式为

8选1数据选择器的输出逻辑式为

将要求产生的函数式化为与数据选择器输出函数式完全对应的形式,得到

用74CC151接成的电路如图。

其中A2=A,A1=B,A0=C,D0=,D1=D2=D4=0,D3=D5=D6=M,D7=1。

[题]用8选1数据选择器设计一个函数发生器电路,它的功能表如表所示。

[解]由功能表写出逻辑式

8选1数据选择器的输出逻辑式为

将要求产生的函数式化为与数据选择器输出函数式完全对应的形式,得到

令A2=S1,A1=S0,A0=A,D0=D7=0,D1=D2=D4=B,D3=D6=1,D5=,即得到图电路。

[题]试用4位并进行加法器74LS283设计一个加/减运算电器。

当控制信号M=0时它将两个输入的4位二进制数相加,而M=1时它将两个输入的4位二进制数相减。

允许附加必要的电路。

[解]被加数用A表示,从74LS283的

端接入;加数用C表示,从74LS283的

端接入。

电路如图。

M=0时,

即S3S2S1S0=A3A2A1A0+C3C2C1C0,此时令

即可

M=1时,

即

S3S2S1S0=A3A2A1A0-C3C2C1C0

=A3A2A1A0+[C3C2C1C0]补

此时令

即可。

为此,将74LS283的进位输入端CI接控制信号M,加数的输入端接一异或门,所接电路图如图JT4-240所示。

[题]能否用一片4位并行加法器74LS283将余3代码转换成8421的二十进制代码?

如果可能,应当如何连线?

[解]由第一章的表可知,从余3码中减去3(0011)即可能得到8421码。

设相加(减)的两个数均为正整数;被加数为

,从74LS283的

端接入;加数为

,从74LS283的

端接入;相加时,应使A和C直接相加;相减时,应使A和C的补码相加。

本题,

=余3码,

=0011,要利用74LS283实现,实现原理如下:

于是得到图电路。

[题]试利用两片4位二制并行加法器74LS283和必要的门电路组成1位二—十进制加法器电路。

(提示:

根据BCD码中8421码的加法运算规则,当两数之和小于、等于9(1001)时,相加的结果和按二进制数相加所得到的结果一样。

当两数之和大于9(即等于1010~1111)时,则应在按二进制数相加的结果上加6(0110),这样就可能给出进位信号,同时得到一个小于9的和。

)

[解]当两个8421BCD码相加时,每个数都不会大于9(1001),考虑低位的进位,最大的和为9+9+1=19。

当用4位二进制加法器74283完成这个加法运算时,加法器输出的是4位二进制数表示的和,而不是BCD码表示的和。

因此,必须将4位二进制数表示的和转换成8421BCD码。

(1)和数一览表如表(a)所示

将0~19的二进制数和与用8421BCD码表示的和进行比较发现,当和数<1001(9)时,二进制码与8421BCD码相同;当数>1001时,只要在二进制和上加0110(6)就可以把二进制和转换为8421BCD码的和,同时产生进位输出。

这一转换可以由一个修正电路来完成。

(2)修正电路的设计

设计修正电路,先列设计一览表,见表JT4-25(b).

由表A4-27(b)可写出修正函数

用卡诺图化简修正函数,化简过程如图(c)所示,结果得

B2=B1=CO1+A3A1+A3A2

从表(b)还可看出,两个8421BCD码相加时的进位CO等于A2或A1。

根据式和上述分析画电路图,如图(d)所示。

[题]若使用4位数值比较器74LS85(见图)组成10位数值比较器,需要用几片?

各片之间的应如何连接?

[解]

需要用三片。

根据CC14585的功能表,各片之间的连接方法如图所示。

[题]试用两个4位数值比较器组成三个数的判断电路。

要求能够判别三个4位二进制数A(a3a2a1a0)、B(b3b2b1b0)、C(c3c2c1c0)是否相等、A是否最大、A是否最小,并分别给出“三个数相等”、“A最大”、“A最小”的输出信号。

可以附加必要的门电路。

[解]如图所示。

[题]若将二一十进制编码中的8421码、余3码、余3循环码、2421码和5211码分别加到二—十进制译码器74HC42(见图)的输入端,并按表的排列顺序依次变化时,输出端是否都会产生尖峰脉冲?

试简述理由。

[解]在这几种二—十进制编码中,只有将余3循环码加到74LS42的输入端、并令其按表1.1.1的状态排列顺序变化时,不会在输出端产生尖峰脉冲。

因为每次输入状态变化时,任何一个与门的4个输入当中仅可能有一个改变状态,所以不存在竞争—冒险现象。

[题]试分析图电路当中A、B、C、D单独一个改变状态时是否存在竞争-冒险现象?

如果存在竞争-冒险现象,那么都发生在其他变量为何种取值的情况下?

[解]写出Y的逻辑表达式:

根据“只要输出端的逻辑函数在一定条件下能化简成或,则必然会出现竞争冒险现象”的方法可知:

当B=0,C=D=1,A发生变化时;当A=0,B=D=1,C发生变化时;

当A=D=1,C=0,B发生变化时;当A=0,B=X,C=1,D发生变化时;

当B=1,D=0,A=X,C发生变化时;当A=1,B=0,C=1,D发生变化时;

电路均会产生竞争冒险现象。