EMC和ESD分析学习资料.docx

《EMC和ESD分析学习资料.docx》由会员分享,可在线阅读,更多相关《EMC和ESD分析学习资料.docx(12页珍藏版)》请在冰豆网上搜索。

EMC和ESD分析学习资料

EMC和ESD

一:

PCB的EMC设计

1PCB的EMC简单对策

同系统EMC的解决措施一样,PCB的EMC也要针对其三要素(干扰源、耦合途径、敏感装置)对症下药:

降低EMI强度

切断耦合途径

提高自身的抗扰能力

针对PCB的耦合途径之一传导干扰,我们通常采用扩大线间距、滤波等措施;

针对PCB的耦合途径之二辐射干扰,我们通常主要采取控制表层布线,增加屏蔽等手段;

2、单板层设置的一般原则

A.元器件下面(顶层、底层)为地平面,提供器件屏蔽层以及顶层布线提供回流平面;

B.所有信号层尽可能与地平面相邻(确保关键信号层与地平面相邻),关键信号不跨分割;

C.尽量避免两信号层直接相邻;

D.主电源尽可能与其对应地相邻;

E.兼顾层压结构对称;

具体PCB的层设置时,要对以上原则进行灵活掌握(?

),根据实际单板的需求,确定层的排布,切忌生搬硬套.以下为为单板层排布方案,供大家参考:

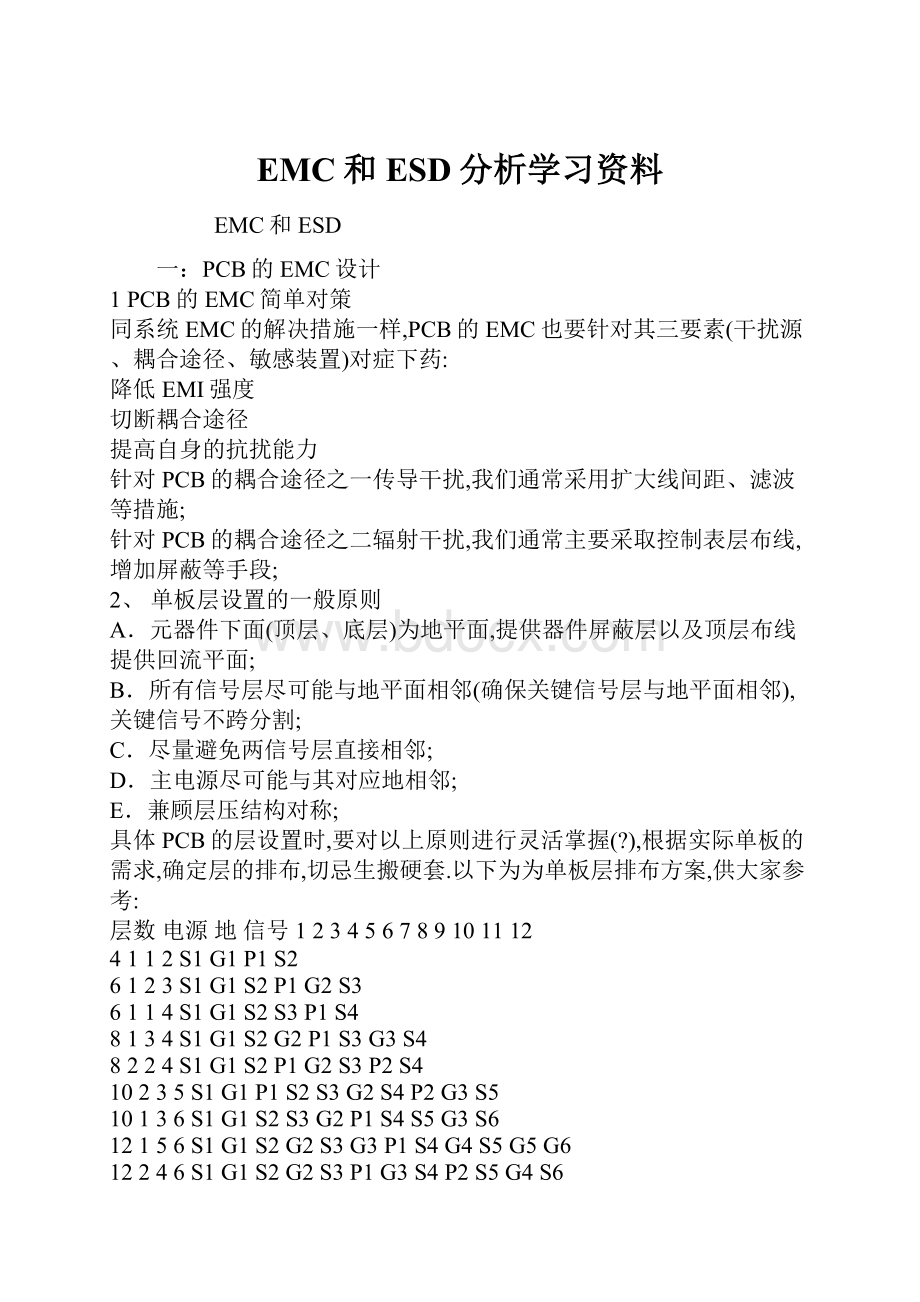

层数电源地信号123456789101112

4112S1G1P1S2

6123S1G1S2P1G2S3

6114S1G1S2S3P1S4

8134S1G1S2G2P1S3G3S4

8224S1G1S2P1G2S3P2S4

10235S1G1P1S2S3G2S4P2G3S5

10136S1G1S2S3G2P1S4S5G3S6

12156S1G1S2G2S3G3P1S4G4S5G5G6

12246S1G1S2G2S3P1G3S4P2S5G4S6

以六层板为例,以下有3种方案:

A.S1G1S2S3P1S4

B.S1G1S2P1G2S3

C.S1G1S2G2P1S3

优先考虑方案B,并优先考虑布线层S2,其次是S3、S1;

在成本较高时,可采用方案A,优选布线层S1,S2,其次是S3,S4;

对于局部、少量信号要求较高的场合,方案C比方案A更合适;(为什么?

)

(注意,在考虑电源、地平面的分割情况下,实际情况因分割等因素可能有所出入)

3.电源、地系统的设计

3.1滤波设计

3.1.1滤波电路的基本概念

滤波电路是由电感、电容、电阻、铁氧体磁珠和共模线圈等构成的频率选择性网络,低通滤波器是EMC抑制技术中普遍应用的滤波器,低频信号可以很小的衰减通过,而高频信号则被滤除.

3.1.2电源滤波

电源的滤波有三层:

A.电源经滤波处理后,分别跨入单板各模块,此部分中间的电源通路滤波处理

B.板级滤波:

储能、滤波电容

C.元件级滤波:

去耦电容

3.1.2.1典型分散式供电单板电源的设计

A.按照原理框图布局,电源流向清晰,避免输入、输出交叉布局;

B.先防护,后滤波,防护通道线宽》50MIL;

C.各功能模块相对集中、紧凑(如模块电源的CASE管脚上电容靠近CASE管脚放置,且CASE管脚到电容的连线短而粗),严禁交叉、错位;

D.整个电流通路布线(或铜箔)线宽满足栽流能力要求,且》50MIL(我司可适当减小)

E.电源输入到DC/DC的输入侧,除对应的平面外,一般采用内电层挖空处理,接口电源电源对应区域无其它走线、平面穿过;

F.VCC输出滤波电路靠近DC/DC输出位置;

3.1.2.2单板内部电源的设计

A.板内分支电源的设计

板内分支电源常用的为派型滤波、LC滤波或DC/DC变换,此类分支电源的设计要求为:

(1)靠近使用该电源的电路布局;滤波电路布局要紧凑;

(2)整个电源通道的线宽要满足载流需求;

B.关键芯片的电源设计

对于一些功耗大、高频、高速器件,其电源要求:

(1)在该芯片周围均匀放置1-4个电容(储能);

(2)对于芯片手册指定的电源管脚,必须就近放置去藕电容,对去藕无特殊需求的情况下,可酌情考虑放置适当的去藕电容;

(3)滤波电容靠近IC的电源管脚放置,位置、数量适当;

3.2地设计

3.2.1常见接地方式及其特点:

A.单点串联接地

B.单点并联接地

C.多点接地

D.混合接地

单点接地的好处是接地线比较明确清楚,但在高频时阻抗大,可能影响IC自身的稳定工作,更多的时候是产生共阻抗干扰耦合到相邻的共地线IC上.我司现在根据单板的工作频率酌情处理,但在频率较高时,建议尽量减少使用单点接地(硬件提供此类要求).

多点接地的优点是IC工作有各自的电流回路,不会产生共地线阻抗的互扰问题,同时接地线很短,减少地线阻抗.但其不足之处为:

单板高频回路数量剧增,这些高频电流回路对磁场很敏感(EMS能力差),所以在进行设计时需要注意.

混合接地结合了两者特点,低频电流单点接地,高频电流将沿着各自IC的接地电容回流,相互独立.(需要LAYOUT人员丰富自己的硬件知识)

3.2.2单板中各种地的命名和意义

PGND:

机壳地.和系统或插框的金属外壳相连,即和系统的基准地(大地)相连,主要作用是为异地系统之间的相互通信提供统一的信号基准,同时为各种防护滤波电路通路电流的旁路点.

GND:

系统地.为系统或插框内各个单板之间的通信提供基准(参考),多板集成时,主要存在主板上,一般形式为平面方式.单板上为DGND和GND连接.

DGND:

数字信号地.是单板上各种数字电路和IC工作的基准.

AGND:

模拟信号地.是单板上各种模拟电路和IC工作的基准.

(单板接地建议)

3.3电源、地的分割

电源平面的设置需要满足以下条件:

A.单一电源或多种互不交错的电源;

B.相邻层的关键信号不跨分割区;

(地平面的设置除满足电源平面的要求外,还要考虑回流的距离)

C.元件面的下面(等2层或倒数第2层)有相对完整的平面;

D.高频、高速、时钟等关键信号有一相邻地平面;

E.关键电源有一对应地平面相邻;

3.420H规则

什么是20H规则?

由于电源层与地层之间的电场是变化的,在板的边缘会向外辐射电磁干扰.我们称之为电源、地的边沿效应.

将电源层对地层适当内缩,可有效减少电源层与地层之间的对外EMI辐射,降低电源、地的边沿效应.以电源和地之间的介质厚度(H)为单位,若内缩20H则可以将70%的电场限制在接地层边沿内;内缩100H则可以将98%的电场限制在内.

同理,普遍要求关键布线区域相对参考平面内缩3H以上.

4.PCB布局与EMC

布局的基本原则:

A.参照原理功能框图,基于信号走向,按照功能模块划分

B.数字电路与模拟电路、高速电路与低速电路、干扰源与敏感电路分开布局

C.敏感信号、强辐射信号回路面积最小

D.晶体、晶振、继电器、开关电源等强辐射器件或敏感器件远离单板对外接口连接器、敏感器件装置,推荐距离》1000MIL

E.隔离器件、A/D器件输入、输出互相分开,无耦合通路(如相邻的参考平面),最好跨接于对应的分割区

4.1滤波电容的布局

A.单板接口位置应放置适量的储能电容;

B.所有分支电源接口电路;

C.存在较大电流变化的区域,如电源模块的输入与输出端、风扇、继电器等;

D.PCB电源接口电路(滤波);

E.去藕电容靠近电源,同时位置、数量适当;

4.2接口电路布局

A.接口信号的滤波、防护、和隔离等器件靠近接口连接器放置,先防护,后滤波

B.接口变压器、光藕等隔离器件做到初次级完全隔离

C.变压器与连接器之间的信号网络无交叉

D.变压器对应的BOTTOM层区域尽可能没有其它器件放置

E.接口IC(网口、通信口(高速)、串口等)尽量靠近变压器或连接器放置

F.相应,网口、通信口(高速)、串口的接收、发送端匹配电阻靠近对应的接口IC放置

4.3时钟电路布局

A.时钟电路(晶振、时钟驱动电路等)离对外接口电路》1000MIL

B.多负载时,晶振、时钟驱动电路要与对应负载呈星型排布

C.时钟驱动器靠近晶振放置,推荐曼哈顿距离《1000MIL

D.时钟输出的匹配电阻靠近晶振或时钟驱动电路的输出脚,推荐距离《1000MIL

E.晶振、时钟驱动电路必须进行LC或派型滤波,滤波电路的布局遵照电源滤波电路布局要求

F.时钟驱动电路远离敏感电路

G.不同的晶振及时钟电路不相邻放置

4.4其它模块布局的基本原则

A.看门狗电路及复位电路远离接口

B.隔离器件如磁珠、变压器、光藕放在分割线上,且两侧分开

C.扣板连接器周围的滤波电容布局数量、位置合理

D.板内散热器接地(推荐多点接地),且远离接口,推荐距离》1000MIL;

E.A/D、D/A器件放在模拟、数字信号分界处,避免模拟、数字信号布线交叠

F.同一差分线对上的滤波器件同层、就近、并行、对称放置

5 PCB布线与EMC

布线基本原则

A.走线短,间距宽,过孔少,无环路

B.有延时要求的走线,其长度符合要求

C.无直角,对关键信号线优先采用元弧倒角(差别不大)

D.相邻层信号走线互相垂直或相邻层的关键信号平行布线《1000MIL

E.走线线宽无跳变或满足阻抗一致

5.1电源、地的布线要求

A.无环路地,电源及对应地构成的回路面积小

B.共用一个电源、地过孔的管脚数《4

C.滤波电容的电源、地走线宽度、长度需优先

D.屏蔽地线接地过孔间距《3000MIL

5.2接口电路布线

A.接口变压器等隔离器件初、次级互相隔离,无相邻平面等耦合通路,对应参考平面隔离宽度》100MIL

B.接口电路的布线要遵循先防护、后滤波的原则顺序

C.接口电路的差分线遵守:

并行、同层、等长;(不同线对满足3W原则)

D.PGND以外的参考平面与接口位置的PGND平面无重叠

E.板边接插件孔金属化,并接PGND

F.跨分割的复位线在跨分割处加桥接措施(地线或电容)

G.接口IC的电源、地参考器件手册处理,如果需要分割时,数字部分不能扩展到外接接口信号线附近

5.3时钟电路布线

A.表层无时钟线或布线长度《500MIL,关键时钟表层布线《200MIL,并且要有完整地平面作回流,跨分割位置已做桥接处理

B.晶振及时钟驱动电路区域相邻层无其它布线穿过

C.与电源滤波电路布线要求相同

D.时钟线周围避免有其它信号线(推荐满足3W)

E.不同时钟信号之间拉大距离(满足5W)

F.当时钟信号换层且回流参考平面也改变时,推荐在时钟线换层过孔旁布一接地过孔

G.时钟布线与I/O接口、端子的间距》1000MIL

H.时钟线与相邻层平行布线的平行长度《1000MIL

I.时钟线无线头,若出于增加测试点的需要,则线头长度《500MIL

5.4其他布线要求

A.单板已做传输线阻抗控制及匹配处理

B.无孤立铜皮,散热片/器做接地处理

C.地址总线(尤其是低3位的地址总线A0、A1、A2)参照时钟布线要求

D.差分线除保持基本原则外,不能有其它线在中间

E.关键信号走线未跨分割(包括过孔,焊盘导致的参考平面缝隙)

F.滤波器等器件的输入、输出信号线未互相平行、交叉走线

G.关键信号线距参考平面边沿》3H

I. 电源》1A的电源所用的表贴器件的焊盘要至少有2个连接到相应的电源平面

二:

PCB布线是ESD防护的一个关键要素,合理的PCB设计可以减少故障检查及返工所带来的不必要成本。

在PCB设计中,由于采用了瞬态电压抑止器(TVS)二极管来抑止因ESD放电产生的直接电荷注入,因此PCB设计中更重要的是克服放电电流产生的电磁干扰(EMI)电磁场效应。

本文将提供可以优化ESD防护的PCB设计准则。

电路环路

电流通过感应进入到电路环路,这些环路是封闭的,并具有变化的磁通量。

电流的幅度与环的面积成正比。

较大的环路包含有较多的磁通量,因而在电路中感应出较强的电流。

因此,必须减少环路面积。

最常见的环路如图1所示,由电源和地线所形成。

在可能的条件下,可以采用具有电源及接地层的多层PCB设计。

多层电路板不仅将电源和接地间的回路面积减到最小,而且也减小了ESD脉冲产生的高频EMI电磁场。

如果不能采用多层电路板,那么用于电源线和接地的线必须连接成如图2所示的网格状。

网格连接可以起到电源和接地层的作用,用过孔连接各层的印制线,在每个方向上过孔连接间隔应该在6厘米内。

另外,在布线时,将电源和接地印制线尽可能靠近也可以降低环路面积,如图3所示。

减少环路面积及感应电流的另一个方法是减小互连器件间的平行通路,见图4。

当必须采用长于30厘米的信号连接线时,可以采用保护线,如图5所示。

一个更好的办法是在信号线附近放置地层。

信号线应该距保护线或接地线层13毫米以内。

如图6所示,将每个敏感元件的长信号线(>30厘米)或电源线与其接地线进行交叉布置。

交叉的连线必须从上到下或从左到右的规则间隔布置。

电路连线长度

长的信号线也可成为接收ESD脉冲能量的天线,尽量使用较短信号线可以降低信号线作为接收ESD电磁场天线的效率。

尽量将互连的器件放在相邻位置,以减少互连的印制线长度。

地电荷注入

ESD对地线层的直接放电可能损坏敏感电路。

在使用TVS二极管的同时还要使用一个或多个高频旁路电容器,这些电容器放置在易损元件的电源和地之间。

旁路电容减少了电荷注入,保持了电源与接地端口的电压差。

TVS使感应电流分流,保持TVS钳位电压的电位差。

TVS及电容器应放在距被保护的IC尽可能近的位置(见图7),要确保TVS到地通路以及电容器管脚长度为最短,以减少寄生电感效应。

连接器必须安装到PCB上的铜铂层。

理想情况下,铜铂层必须与PCB的接地层隔离,通过短线与焊盘连接。

PCB设计的其它准则

避免在PCB边缘安排重要的信号线,如时钟和复位信号等;

将PCB上未使用的部分设置为接地面;

机壳地线与信号线间隔至少为4毫米;

PS:

消费者分析 保持机壳地线的长宽比小于5:

1,以减少电感效应;

用TVS二极管来保护所有的外部连接;

保护电路中的寄生电感

TVS二极管通路中的寄生电感在发生ESD事件时会产生严重的电压过冲。

尽管使用了TVS二极管,由于在电感负载两端的感应电压VL=L×di/dt,过高的过冲电压仍然可能超过被保护IC的损坏电压阈值。

(2)物品的独一无二

保护电路承受的总电压是TVS二极管钳位电压与寄生电感产生的电压之和,VT=VC+VL。

一个ESD瞬态感应电流在小于1ns的时间内就能达到峰值(依据IEC

5、就业机会和问题分析 61000-4-2标准),假定引线电感为每英寸20nH,线长为四分之一英寸,过冲电压将是50V/10A的脉冲。

经验设计准则是将分流通路设计得尽可能短,以此减少寄生电感效应。

就算你买手工艺品来送给朋友也是一份意义非凡的绝佳礼品哦。

而这一份礼物于在工艺品店买的现成的礼品相比,就有价值意义,虽然它的成本比较低但它毕竟它是你花心血花时间去完成的。

就像现在最流行的针织围巾,为何会如此深得人心,更有人称它为温暖牌绝大部分多是因为这个原因哦。

而且还可以锻炼你的动手能力,不仅实用还有很大的装饰功用哦。

所有的电感性通路必须考虑采用接地回路,TVS与被保护信号线之间的通路,以及连接器到TVS器件的通路。

被保护的信号线应该直接连接到接地面,若无接地面,则接地回路的连线应尽可能短。

TVS二极管的接地和被保护电路的接地点之间的距离应尽可能短,以减少接地平面的寄生电感。

2、价格“适中化”

精明的商家不失时机地打出“自己的饰品自己做”、“DIY(DoItYourself)饰品、真我个性”的广告,推出“自制饰品”服务,吸引了不少喜欢标新立异、走在潮流前端的年轻女孩,成为上海的时尚消费市场。

其市场现状特点具体表现为:

最后,TVS器件应该尽可能靠近连接器以减少进入附近线路的瞬态耦合。

虽然没有到达连接器的直接通路,但这种二次辐射效应也会导致电路板其它部分的工作紊乱。

1996年“碧芝自制饰品店”在迪美购物中心开张,这里地理位置十分优越,交通四通八达,由于位于市中心,汇集了来自各地的游客和时尚人群,不用担心客流量的问题。

迪美有300多家商铺,不包括柜台,现在这个商铺的位置还是比较合适的,位于中心地带,左边出口的自动扶梯直接通向地面,从正对着的旋转式楼梯阶而上就是人民广场中央,周边4、5条地下通道都交汇于此,从自家店铺门口经过的90%的顾客会因为好奇而进去看一下。

参考文献:

1.Boxleitner,Warren,"ElectrostaticDischargeand

为此,装潢美观,亮丽,富有个性化的店面环境,能引起消费者的注意,从而刺激顾客的消费欲望。

这些问题在今后经营中我们将慎重考虑的。

ElectronicEquipment,"IEEEPress,1989.

2.Mardiguian,Michel,"Electrostatic

Discharge,Understand,SimulateandFixESDproblems,"

3.InterferenceControltechnologies,1992.

3、你是否购买过DIY手工艺制品?

4.Russell,Bill,"PowerProtectionisCriticalFor

2、你大部分的零用钱用于何处?

Today'sShrinkingSystemDesigns,"WirelessSystems

Design,February1999.

5.Standler,RonaldB.,"ProtectionofElectronic

CircuitsfromOvervoltages,"JohnWiley&Sons,1989.