数电课设四位二进制减计数缺0011 0100 0101.docx

《数电课设四位二进制减计数缺0011 0100 0101.docx》由会员分享,可在线阅读,更多相关《数电课设四位二进制减计数缺0011 0100 0101.docx(20页珍藏版)》请在冰豆网上搜索。

数电课设四位二进制减计数缺001101000101

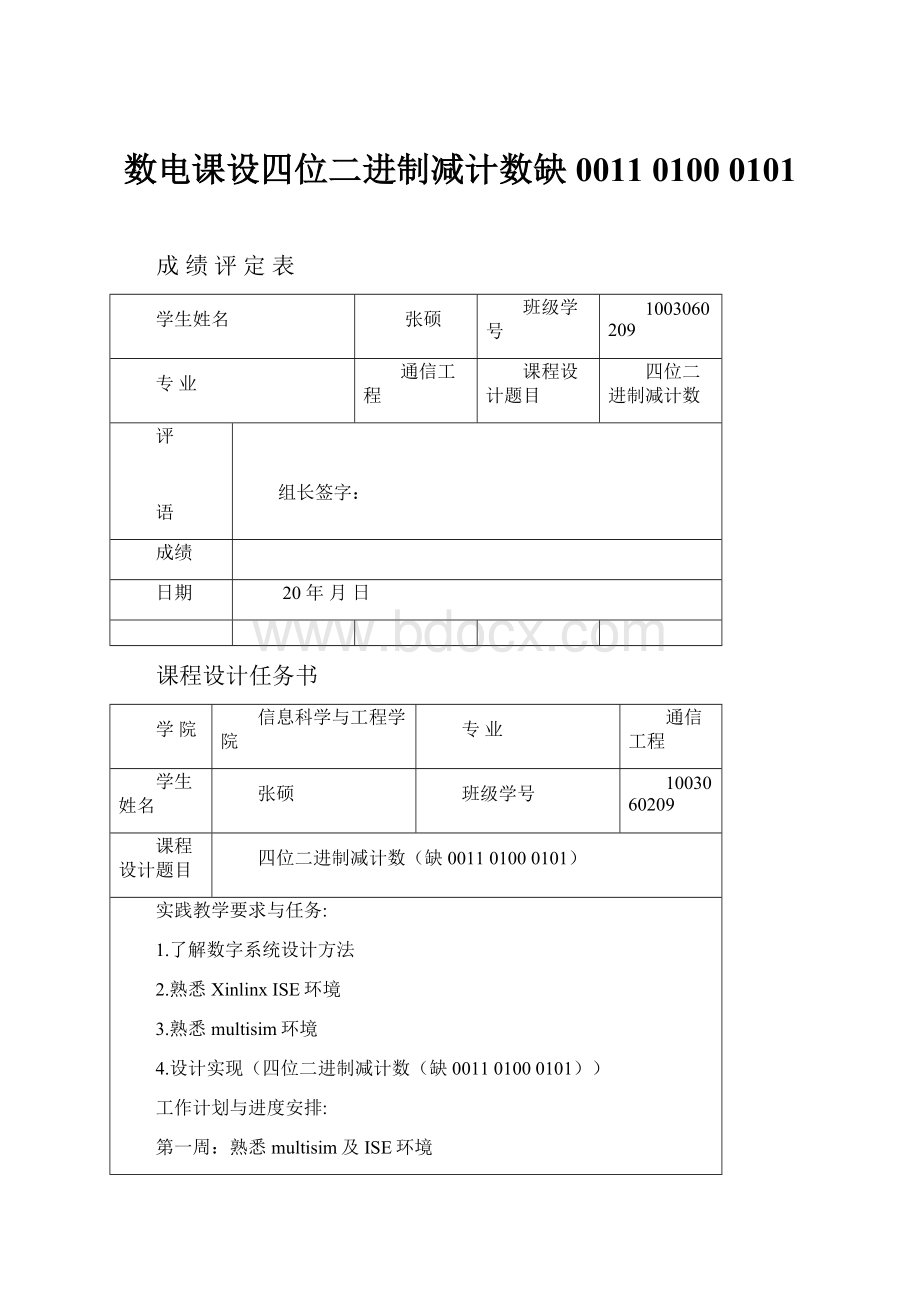

成绩评定表

学生姓名

张硕

班级学号

1003060209

专业

通信工程

课程设计题目

四位二进制减计数

评

语

组长签字:

成绩

日期

20年月日

课程设计任务书

学院

信息科学与工程学院

专业

通信工程

学生姓名

张硕

班级学号

1003060209

课程设计题目

四位二进制减计数(缺001101000101)

实践教学要求与任务:

1.了解数字系统设计方法

2.熟悉XinlinxISE环境

3.熟悉multisim环境

4.设计实现(四位二进制减计数(缺001101000101))

工作计划与进度安排:

第一周:

熟悉multisim及ISE环境

练习数字系统设计方法

第二周:

(1)在ISE环境中仿真实现(四位二进制减计数(缺001101000101))并下载到FPGA目标芯片上

(2)在Multisim环境中仿真实现(四位二进制减计数(缺001101000101))并通过虚拟仪器验证其正确性

指导教师:

201年月日

专业负责人:

201年月日

学院教学副院长:

201年月日

目录

一、课程设计目的3

二、设计实验框图4

三、实现过程4

1、VHDL4

1、1、建立工程4

1、2VHDL源程序6

1、3编译及仿真9

1、4引脚锁定与下载12

1、5仿真结果分析15

2电路设计15

2、1设计原理15

2、2基于Multisim的设计电路18

2、3虚拟观察的波形19

2、4仿真结果分析19

四、设计的总结与体会20

一、课程设计目的

1.了解数字系统设计方法

2.熟悉XinlinxISE环境

3.熟悉multisim环境

4.设计实现(四位二进制减计数(缺001101000101))

二、设计实验框图

状态转换图如下:

11111110110111001011101010011000011101100010000100001111是有效循环

三、实现过程

1、VHDL

代码

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

entityzs1is

PORT(cp,r:

INSTD_LOGIC;

q:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));

endzs1;

ARCHITECTUREBehavioralOFzs1IS

SIGNALcount:

STD_LOGIC_VECTOR(3DOWNTO0);

BEGIN

PROCESS(cp,r)

BEGIN

ifr='0'thencount<="1111";

elsiFcp'EVENTANDcp='1'THEN

ifcount="0110"THEN

count<="0010";

ELSEcount<=count-1;

ENDIF;

endif;

ENDPROCESS;

q<=count;

endBehavioral;

1、1、建立工程

File——〉NewProject;ProjectName:

zs;ProjectLocation:

工程保存的位置(例:

C:

\Users\Administrator\Desktop\geng\count4\zs);next——>……——>next直至finish。

1、2VHDL源程序

右击xc95108-15pc84,选NewSource,再选VHDLModule后,填加文件名(例:

Filename:

zs1)——〉next(PortName中随便填c)——〉finish。

然后写入程序,保存程序,双击ImplementDesign(或右键Run),运行程序,调试成功显示如下:

1、3编译及仿真

综合通过后,回到vi.vhd界面,建立波形仿真文件进行观察,在ISE软件左侧右键点击zs1-BehavioralSource,选择NewSource,在弹出的对话框中选择Testbenchwaveform,键入波形图文件名,点击Next进入一路点到next,如图:

左侧Sourcesfor栏内选择BehavioralSimulation,选择t1,打开Processes下的XilinxISESimulator如图

点击SimulateBehavioralModel(或右键RUN)运行仿真波形,如下(负逻辑)

时序图如图:

时序图如图

1、4引脚锁定与下载

左上侧Sourcefor选项中选择Synthesis/Implementation,左下侧Processes——〉UserConstraints——〉AssignPackagePins分配引脚:

Cp-key1,r-sw1,q3-L1,q2-L2,q1-L3,q0-L4。

点击保存,OK。

回到ISE:

Processes——〉ImplementDesign——〉OptionalImplementationTools——〉双击LockPins锁定引脚

Processes——〉ImplementDesign——〉双击GenerateProgrammingFile——〉ConfigureDevice(iMPACT),默认JTAG,finishi,v1.jed——〉Open

右键点绿——〉Progaram——〉OK,结束下载。

(调试时sw向上是1;灯亮为1)

1、5仿真结果分析

如仿真波形所示,输出的四位二进制数按减法计数依次逐渐减小,并且每当循环到0110时,紧接着下一个数是0010(缺0101,0100,0011),符合题目要求,仿真成功。

2电路设计

2、1设计原理

1.选择触发器

选用由于JK触发器功能齐全、使用灵活,在这里选用4个CP下降沿触发的边沿JK触发器。

2.求时钟方程、状态方程

(1)求时钟方程

采用同步方案,故取CP0=CP1=CP2=CP3=CP。

CP是整个要设计的时序电路的输入时钟脉冲。

(2)求状态方程

由图2.1所示状态图可直接画出如图2.3所示电路次态

的卡诺图,再分解开便可以得到如图2.4所示各触发器的卡诺图。

00

01

11

10

00

1111

0000

X

0001

01

X

X

0110

0010

11

1011

1100

1110

1101

10

0111

1000

1010

1001

图2.3次态

的卡诺图

00

01

11

10

00

1

0

X

0

01

X

X

0

0

11

1

1

1

1

10

0

1

1

1

(a)

00

01

11

10

00

1

0

X

0

01

X

X

1

0

11

0

1

1

1

10

1

0

0

0

(b)

00

01

11

10

00

1

0

X

0

01

X

X

1

1

11

1

0

1

0

10

1

0

1

0

(c)

00

01

11

10

00

1

0

X

1

01

X

X

0

0

11

1

0

0

1

10

1

0

0

1

(d)

根据卡诺图得到:

4.求驱动方程

JK触发器的特性方程为

与特性方程做比较,可得

2、2基于Multisim的设计电路

根据所选用的触发器和时钟方程、输出方程、驱动方程,便可以画出如图2.5所示的逻辑电路图。

图2.5逻辑电路图

2、3虚拟观察的波形

2、4仿真结果分析

状态图如下:

11111110110111001011101010011000011101100010000100001111是有效循环

将无效状态0011,0100,0101代入状态方程,进行计算,结果如下:

01001011,01010110,00110010

可见在输入计数脉冲cp操作下,都能回到有效状态,所以此时序电路能自启动

四、设计的总结与体会

在平时上课是看到老师试用那个Multisim软件,一直很好奇,在这次课程设计中,我研究了有关ISE以及Multisim软件的应用以及使用方法,在和同学的研究下完成了对四位二进制减法计数器的编程,并且分别运用ISE和Multisim软件实现并得到正确的仿真波形。

虽然最后能做出仿真波形,但是我对Multisim软件操作还不够熟练,需要加强学习,对逻辑电路的设计方法也需要改进,后续的学习中还应予以提高。

希望在下次学习中能做得更好。