quartusII图形设计过程教程.docx

《quartusII图形设计过程教程.docx》由会员分享,可在线阅读,更多相关《quartusII图形设计过程教程.docx(20页珍藏版)》请在冰豆网上搜索。

quartusII图形设计过程教程

Quartus

的使用

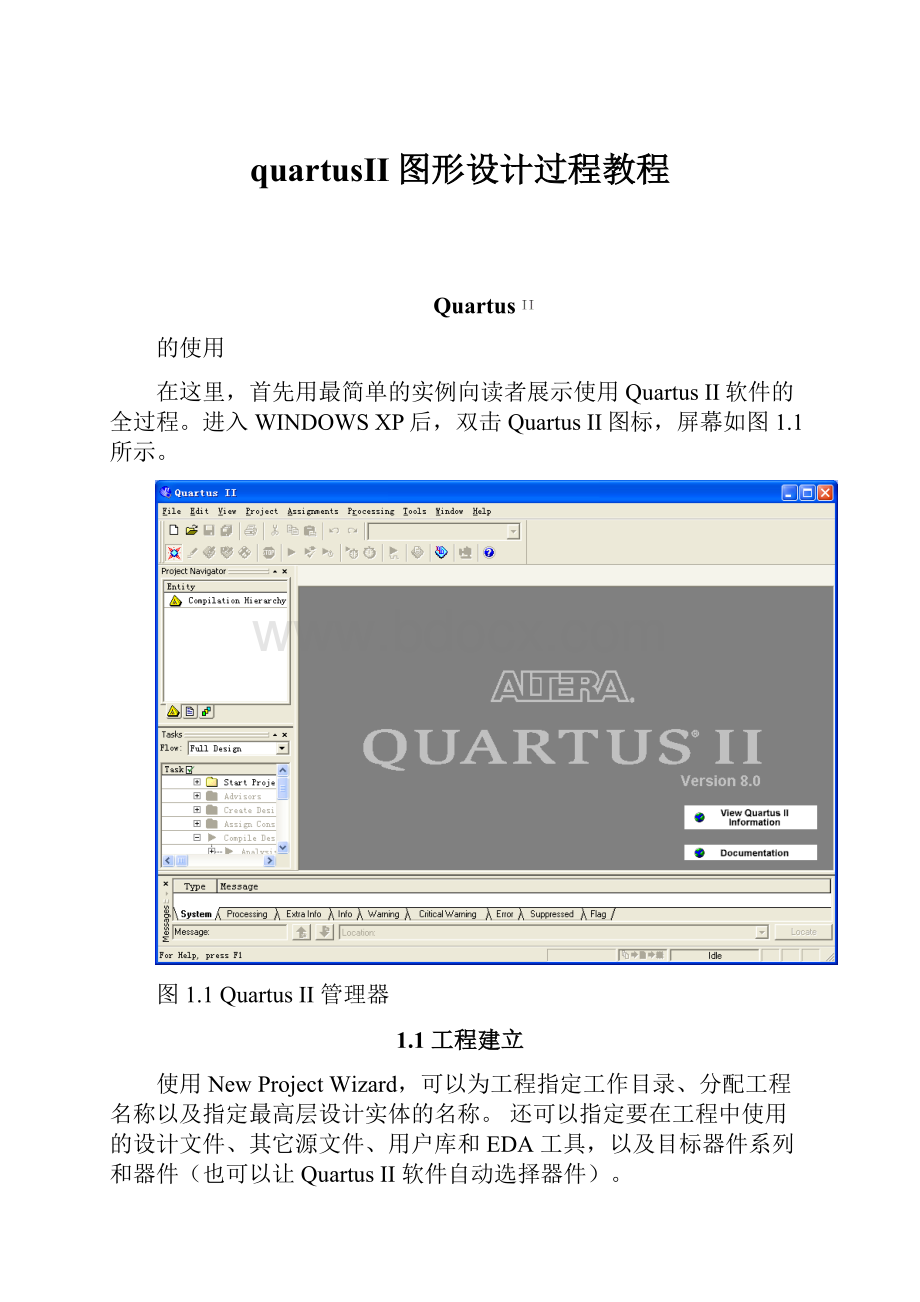

在这里,首先用最简单的实例向读者展示使用QuartusII软件的全过程。

进入WINDOWSXP后,双击QuartusII图标,屏幕如图1.1所示。

图1.1QuartusII管理器

1.1工程建立

使用NewProjectWizard,可以为工程指定工作目录、分配工程名称以及指定最高层设计实体的名称。

还可以指定要在工程中使用的设计文件、其它源文件、用户库和EDA工具,以及目标器件系列和器件(也可以让QuartusII软件自动选择器件)。

建立工程的步骤如下:

(1)选择File菜单下NewProjectWizard,如图1.2所示。

图1.2建立项目的屏幕

(2)输入工作目录和项目名称,如图1.3所示。

可以直接选择Finish,以下的设置过程可以在设计过程中完成。

图1.3项目目录和名称

(3)加入已有的设计文件到项目,可以直接选择Next,设计文件可以在设计过程中加入,如图1.4所示。

图1.4加入设计文件

(4)选择设计器件,如图1.5所示。

图1.5选择器件

(5)选择第三方EDA综合、仿真和时序分析工具,如图1.6所示。

图1.6选择EDA工具

(6)建立项目完成,显示项目概要,如图1.7所示。

图1.7项目概要

1.2原理图的输入

原理图输入的操作步骤如下:

(1)选择File菜单下New,新建图表/原理图文件,如图1.8

所示。

图1.8新建原理图文件

(2)在图1.9的空白处双击,屏幕如图1.10所示:

(3)在图1.10的SymbolName输入编辑框中键入dff后,单击

ok按钮。

此时可看到光标上粘着被选的符号,将其移到合适的位置(参考图1.11)单击鼠标左键,使其固定;

(4)重复

(2)、(3)步骤,给图中放一个input、not、output

符号,如图1.11所示;在图1.11中,将光标移到右侧input右侧待连线处单击鼠标左键后,再移动到D触发器的左侧单击鼠标左键,即可看到在input和D触发器之间有一条线生成;

图1.9空白的图形编辑器

图1.10选择元件符号的屏幕

图1.11放置所有元件符号的屏幕

(5)重复(4)的方法将DFF和output连起来,完成所有的连

线电路如图1.12所示;

(6)在图1.12中,双击input_name使其衬低变黑后,再键入

clk,及命名该输入信号为clk,用相同的方法将输出信号定义成Q;如图1.13所示。

(7)在图1.13中单击保存按钮,以默认的try1文件名保存,

文件后缀为bdf。

图1.12完成连线后的屏幕

图1.13完成全部连接线的屏幕

(8)在图1.8中,单击编译器快捷方式按钮,完成编译后,弹

出菜单报告错误和警告数目,并生成编译报告如图1.14所示;

图1.14完成编译的屏幕

(9)若需指定器件,选择Assignments菜单下Device选项,屏

幕如图1.15所示;

图1.15器件设置

(10)完成如图1.15所示的选择后,单击OK按钮回到工作

环境;

(11)根据硬件接口设计,对芯片管脚进行绑定。

选择

Assignments菜单下Pins选项;

(12)双击对应管脚后Location空白框,出现下拉菜单中选

择要绑定的管脚,如图1.16所示;

图1.16管脚指定

(13)在图1.16中完成所有管脚的分配,并把没有用到的引

脚设置为Asinputtri-stated,Assignments—Device—DeviceandPinOptions–UnusedPins,然后重新编译项目;

(14)对目标版适配下载,(此处认为实验板已安装妥当,有

关安装方法见实验板详细说明)单击按钮,屏幕显示如图1.17所示;

图1.18适配下载界面

(15)选择HardwareSetup,如图1.19所示;

图1.19下载硬件设置

(16)在图1.19中选择添加硬件ByteBlasteMVorByteBlasterII,如图1.20所示;

图1.20添加下载硬件

(17)可以根据需要添加多种硬件于硬件列表中,双击可选列表中需要的一种,使其出现在当前选择硬件栏中(本实验板采用ByteBlasterII下载硬件),如图1.21所示;

图1.21选择当前下载硬件

(18)选择下载模式,本实验板可采用两种配置方式,AS模式对配置芯片下载,可以掉电保持,而JTGA模式对FPGA下载,掉电后FPGA信息丢失,每次上电都需要重新配置,如图1.22所示;

图1.22选择下载模式

(19)选择下载文件和器件,JTAG模式使用后缀为sof的文

件,AS模式使用后缀为pof的文件,选择需要进行的操作,分别如图1.23,图1.24所示;使用AS模式时,还要设置Assignments菜单下Device,如图1.25,选择图1.25中Device&PinOptions,如图1.26,选择使用的配置芯片,编译;

图1.23JTAG下载模式

图1.24AS下载模式

图1.25器件选项

图1.25配置芯片选择

(20)点击Start按键,开始下载。

1.3文本编辑(verilog)

这一节中将向读者简单介绍如何使用QuartusII软件进行文本编辑。

文本编辑(verilog)的操作如下:

(1)建立我们的project2项目如下图:

图1.26建立项目project2

(2)在软件主窗口单击File菜单后,单击New选项,选择VerilogHDLFile选项,如图1.27所示:

图1.27新建VerilogHDL文件

(3)单击OK进入空白的文本编辑区,进行文本编辑,本节列举一个D触发器的例子,其完成后的屏幕如图1.28所示;

图1.28完成编辑后的屏幕

(4)V文件名必须与模块面相同,将dff1.v文件设置为顶层文

件,Project—SetasTop-levelEntity

(5)完成编辑后的步骤与完成原理图编辑的步骤相同,请参考

1.1节有关容。

(6)利用v文件生成原理图模块。

在v文件编辑界面中,

File—Creat/Update—CreatSymbolFilesforCurentFile.

1.4波形仿真

下面以1.2节中project2为例,介绍使用QuartusII软件自带的仿真器进行波形仿真的步骤。

(1)打开project2项目,新建波形仿真文件,如图1.29;

图1.29新建矢量波形文件

(2)在建立的波形文件左侧一栏中,点击鼠标右键,在弹出菜单中选择InsertNodeorBus,如图1.30所示;

图1.29矢量波形文件节点加入

(3)在出现的图1.30中,选择NodeFinder,将打开NodeFinder对话框,本试验对输入输出的管脚信号进行仿真,所以在Filter中选择Pins:

all,点击List按钮,如图1.31所示;

图1.30节点加入工具框

图1.31NodeFinder对话框

(4)在图1.31左栏中选择需要进行仿真的端口通过中间的按钮加入到右栏中,点击OK,端口加入到波形文件中,如图1.32;

图1.32加入仿真节点后的波形图

(5)在图1.32中,选择一段波形,通过左边的设置工具条,给出需要的值,设置完成激励波形,保存后如图1.33所示;

图1.33设置好激励波形的波形文件

(6)设置为功能仿真:

Assignment—TimingAnalysisSettings--

SimulatorSettings—Simulationmode选择Functional,生成网络表Processing—GenerateFunctionalSimulationNetlist;

(7)点击快捷按钮,开始仿真,完成后得到波形如图1.34所示,根据分析,功能符合设计要求。

图1.33波形仿真结果