基于QUARTUSII的FPGA波形发生器.docx

《基于QUARTUSII的FPGA波形发生器.docx》由会员分享,可在线阅读,更多相关《基于QUARTUSII的FPGA波形发生器.docx(12页珍藏版)》请在冰豆网上搜索。

基于QUARTUSII的FPGA波形发生器

正弦波、不同占空比矩形波信号发生器设计

一、设计目的

1、掌握正弦波、不同占空比矩形波信号发生的设计方法。

2、掌握QUARTUSII软件VHDL语言输入设计的全过程。

3、掌握数据存储及传递的过程。

二、设计要求

本实验要求基于EDA/SOPC实验平台上的FPGA及DAC,产生一定频率的正弦波、不同占空比矩形波信号,能通过键盘控制输出信号,并测量输出信号的频率和输出电压,计算输出频率与原设计频率的误差。

三、方案设计

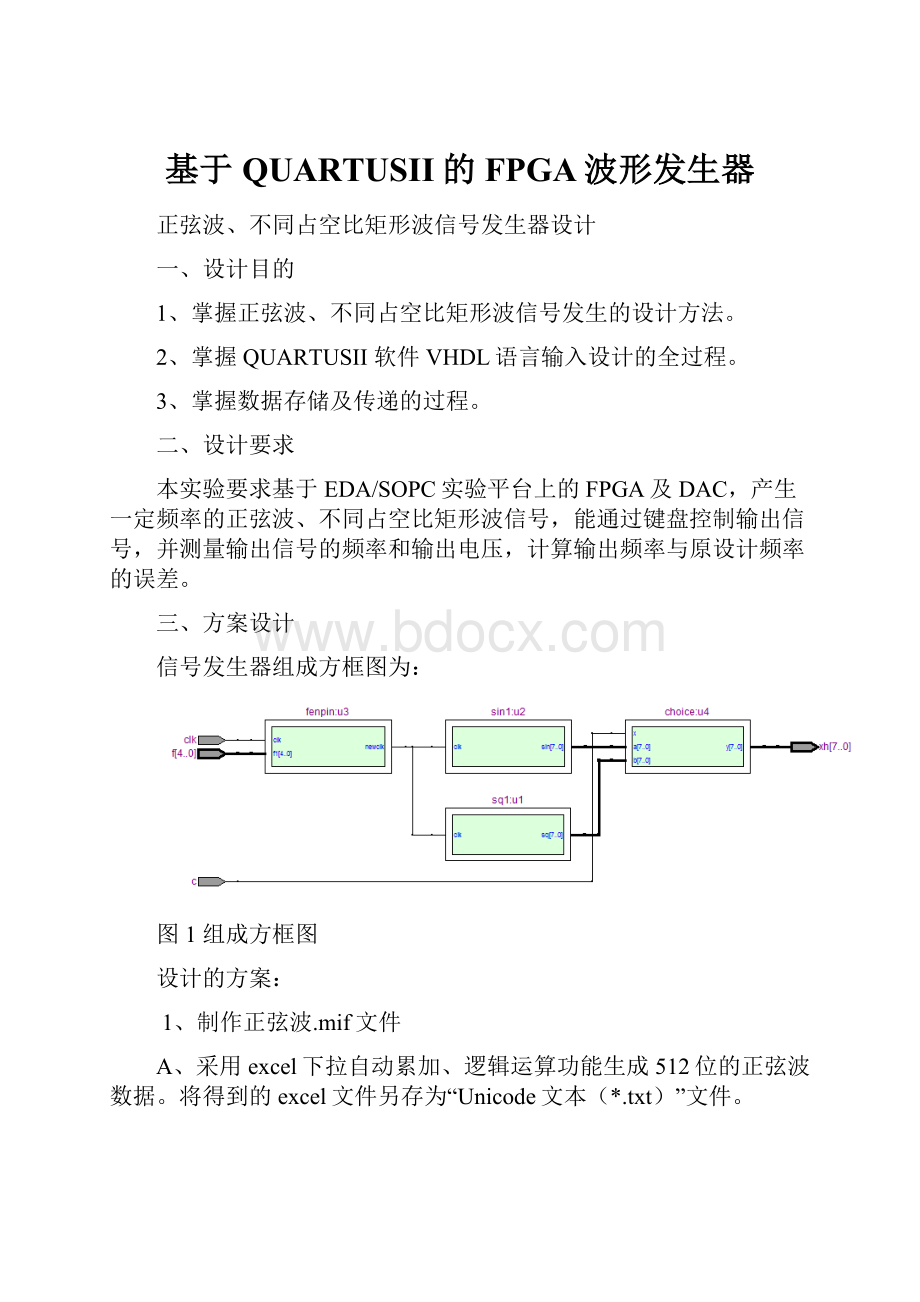

信号发生器组成方框图为:

图1组成方框图

设计的方案:

1、制作正弦波.mif文件

A、采用excel下拉自动累加、逻辑运算功能生成512位的正弦波数据。

将得到的excel文件另存为“Unicode文本(*.txt)”文件。

B、打开quartus2,新建一个TXT文件(file-new-otherfile-txt文件),将MIF文件的格式说明拷贝过来,再得到的TXT文本文件中的数据全部复制到begin与end中间,另存为“.mif”。

下面是mif文件的格式:

WIDTH=8;

DEPTH=512;

ADDRESS_RADIX=UNS;

DATA_RADIX=UNS;

CONTENTBEGIN

.

.

.

End;

2、将电路分为4大模块,第一个模块是分频电路;第二、三个模块是正弦波和方波产生电路;第四个模块是选择输出模块。

3、输出波形理论值:

A、每个时钟信号上升沿,分频电路自动累加一。

当分频输入为“11111”时吗,输出频率最大,为外部时钟频率的1/2。

图2分频电路仿真图

B、储存一个周期的信号的储存器是512位,每来一个时钟信号从一个储存单位取一个数据。

所以输出的最大的频率为fin(输入频率)/512*2;同理可知输出的最小频率为fin(输入频率)/512*32*2。

本实验时钟信号输入采用1.5mhz时钟信号,理论频率值为:

最大频率

1464.84hz

最小频率

45.78hz

表1输出频率理论值

四、设计原理和电路图

(1)分频电路

该电路的根本任务是对输入的时钟信号进行分频。

实现这一功能可用累加器、锁存器和比较器等。

在时钟信号上升沿时立即对锁存器的数据(cnt5)进行累加。

同时还必须注意,检查cnt5是否为“11111”。

当cnt5为“11111”时,对输出频率进行取反。

同时对cnt5进行更新。

分频电路Vhdl设计

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityfenpinis

port(clk:

instd_logic;

f1:

instd_logic_vector(4downto0);

newclk:

outstd_logic

);

endfenpin;

architectureoneoffenpinis

signalabc:

std_logic;

begin

process(clk,f1)-----对时钟进行分频,控制信号频率。

variablecnt5:

std_logic_vector(4downto0);

begin

if(clk'eventandclk='1')then

ifcnt5="11111"thencnt5:

=f1;abc<=(notabc);

elsecnt5:

=cnt5+1;

endif;

endif;

newclk<=abc;

endprocess;

end;

图2分频电路

F1五个输入为分频控制键。

Clk为外电路输入时钟信号,newclk为输出时钟信号。

(2)方波和正弦波lpm_rom元件

该电路的根本任务是读取波形8位数字量。

可由累加器、锁存器和储存器组成。

累加器对9位地址进行累加,使电路能够逐级读取储存器单位数据。

当地址累加到511时,将其制0。

A、定制lpm_rom文件

新建一个block文件,搜索lpm_rom文件,然后根据设计向导完成lpm_rom元件定制。

B、正弦波8为数字量取址vhdl设计

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entitysin1is

port(clk:

instd_logic;

sin:

outstd_logic_vector(7downto0)

);

end;

architectureoneofsin1is

componentlpm_rom0

port(address:

instd_logic_vector(8downto0);

clock:

instd_logic;

q:

outstd_logic_vector(7downto0)

);

endcomponent;

signalq1:

std_logic_vector(8downto0);

begin

process(clk)-----逐步选取rom地址。

begin

if(clk'eventandclk='1')thenq1<=q1+1;

endif;

endprocess;

u1:

lpm_rom0portmap(address=>q1,q=>sin,clock=>clk);

end;

图4正弦波lpm_rom元件

Clk为时钟信号输入(接分频器的输出端口newclk),sin为正弦波信号8为数字量输出。

图5方波lpm_rom元件

Clk为时钟信号输入(接分频器的输出端口newclk),sq为方波信号8为数字量输出

(3)该电路是简单的数据选择电路,由数据选择器构成。

当输入x为高电平时,选择正弦波输出;x为低电平时,选择方波输出。

选择电路vhdl设计:

libraryieee;

useieee.std_logic_1164.all;

entitychoiceis

port(

x:

instd_logic;

a:

instd_logic_vector(7downto0);

b:

instd_logic_vector(7downto0);

y:

outstd_logic_vector(7downto0)

);

endchoice;

architectureoneofchoiceis

begin

process(x,a,b)

begin

ifx='1'theny<=a;

elsey<=b;

endif;

endprocess;

end;

图6数据选择电路

A为信号输入,b为信号输入,x为选择信号输入,y为信号输出。

再将输出y与数模转换器相连接得出模拟信号输出。

(4)顶层设计

顶层设计将调用上面的各个模块,进行元件例化完成电路设计。

顶层vhdl设计

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entitykcsjis

port(clk:

instd_logic;

c:

instd_logic;

f:

instd_logic_vector(4downto0);

xh:

outstd_logic_vector(7downto0)

);

end;

architectureoneofkcsjis

componentsq1

port(clk:

instd_logic;

sq:

outstd_logic_vector(7downto0)

);

endcomponent;

componentchoice

port(a:

instd_logic_vector(7downto0);

b:

instd_logic_vector(7downto0);

x:

instd_logic;

y:

outstd_logic_vector(7downto0)

);

endcomponent;

componentfenpin

port(f1:

instd_logic_vector(4downto0);

clk:

instd_logic;

newclk:

outstd_logic

);

endcomponent;

componentsin1

port(clk:

instd_logic;

sin:

outstd_logic_vector(7downto0)

);

endcomponent;

signala1,b1:

std_logic_vector(7downto0);

signalclk1:

std_logic;

begin

u1:

sq1portmap(clk=>clk1,sq=>b1);

u2:

sin1portmap(clk=>clk1,sin=>a1);

u3:

fenpinportmap(clk=>clk,f1=>f,newclk=>clk1);

u4:

choiceportmap(x=>c,a=>a1,b=>b1,y=>xh);

end;

五、仿真、实验结果与现象

(1)完成设计,进行编译,修改错误的地方。

对设计进行仿真。

图7仿真图

Clk为时钟信号输入端口,c为方波、正弦波信号输出选择输入端口,f为分频控制输入端口,xh为信号输出端口。

当输入端口c为高电平时,端口xh输出为正弦波信号;当c为低电平时,端口xh输出为方波信号。

F为5位的信号输入端口,是对输入信号clk进行不同倍数的分频。

从而控制正弦波与方波的频率。

Xh输出端口将读取的正弦波与方波的8为数字量输出。

(2)进行管脚配置

表2管脚分配表

再次进行编译,使管脚生效。

选择模式5,进行下载。

选择1.5mhz时钟信号,使用示波器观察输出波形,记录实验数据。

波形

正弦波

方波

最大频率

1.46khz

1.47khz

最小频率

45.66hz

45.66hz

峰峰值

8.64v

8.72v

表3实验数据记录

实验现象

图8正弦波

图9方波

六、设计总结与心得

在本次实验设计首次采用了lpm_rom模块,对于lpm_rom模块使用的“.mif”文件,在制作该文件有很多方法,使用c程序的循环运算、使用matlab软件、使用excel表格等等,很多工具都可以制作出。

在未来的设计中,我相信将会更多的运用到我们在大学所学的知识,而这些知识总是被急功近利的我们认为是没用。

实验只是在gw48实验箱进行下载,测试。

如果是制作成品,对我们来说将是更大的挑战。