第7章中断及中断控制器长江大学计算机科学学院.docx

《第7章中断及中断控制器长江大学计算机科学学院.docx》由会员分享,可在线阅读,更多相关《第7章中断及中断控制器长江大学计算机科学学院.docx(27页珍藏版)》请在冰豆网上搜索。

第7章中断及中断控制器长江大学计算机科学学院

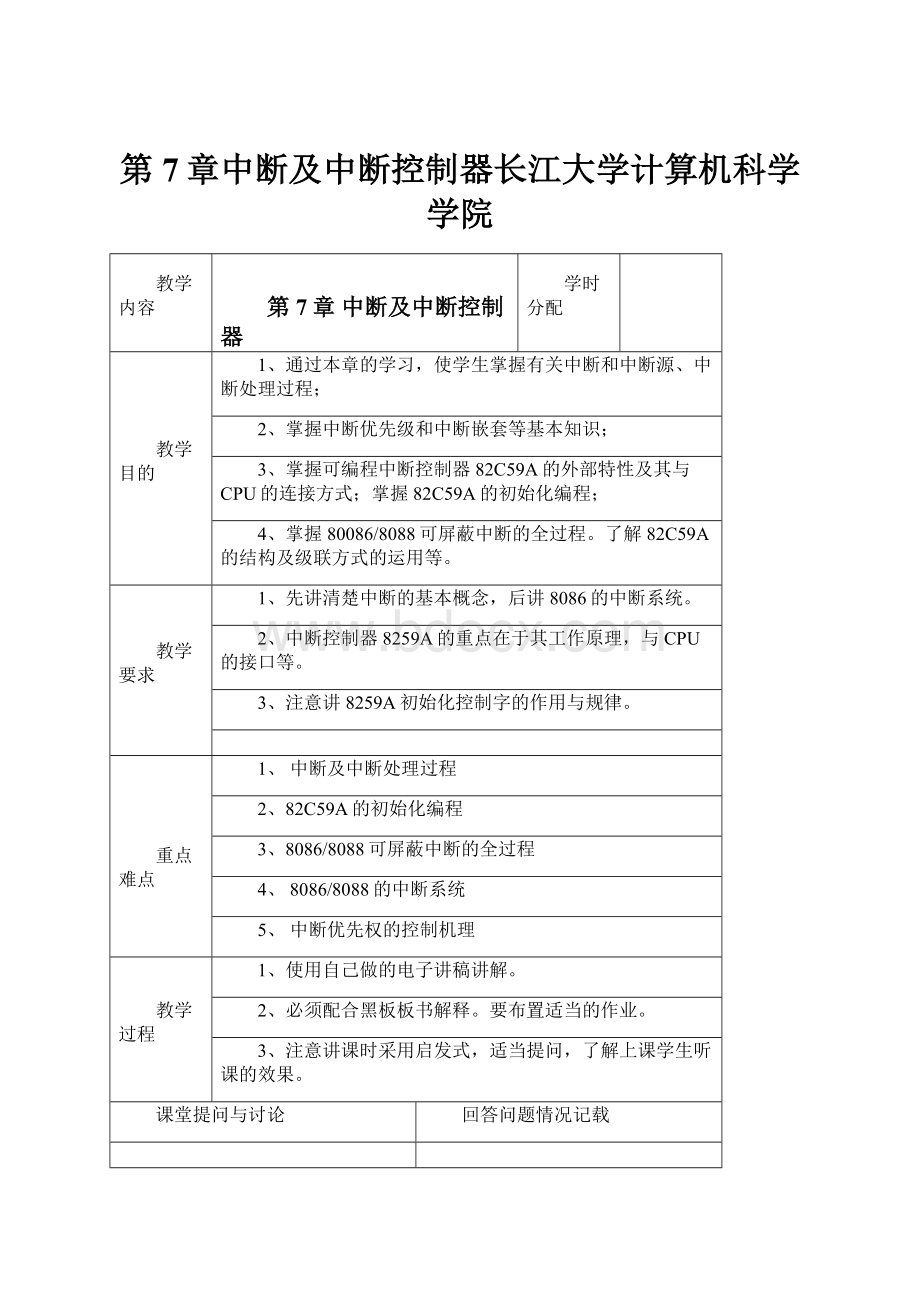

教学内容

第7章中断及中断控制器

学时分配

教学目的

1、通过本章的学习,使学生掌握有关中断和中断源、中断处理过程;

2、掌握中断优先级和中断嵌套等基本知识;

3、掌握可编程中断控制器82C59A的外部特性及其与CPU的连接方式;掌握82C59A的初始化编程;

4、掌握80086/8088可屏蔽中断的全过程。

了解82C59A的结构及级联方式的运用等。

教学要求

1、先讲清楚中断的基本概念,后讲8086的中断系统。

2、中断控制器8259A的重点在于其工作原理,与CPU的接口等。

3、注意讲8259A初始化控制字的作用与规律。

重点难点

1、中断及中断处理过程

2、82C59A的初始化编程

3、8086/8088可屏蔽中断的全过程

4、8086/8088的中断系统

5、中断优先权的控制机理

教学过程

1、使用自己做的电子讲稿讲解。

2、必须配合黑板板书解释。

要布置适当的作业。

3、注意讲课时采用启发式,适当提问,了解上课学生听课的效果。

课堂提问与讨论

回答问题情况记载

7.1概述

除了用电子稿讲之外,还要补充数字逻辑的知识,一定要为讲8259打好基础

7.1.1中断、中断源及中断系统

1.中断、中断源

(1)“中断”:

是指在CPU正常运行程序时,由于内、外部事件引起CPU暂时中止正在运行的程序,转而去执行请求CPU暂时中止的内、外部事件的服务程序,服务程序处理完毕后又返回到被中止的程序。

(2)能够向CPU发出中断请求的中断来源称为“中断源”。

2.中断系统的功能

(1)中断处理:

包括发现中断请求、响应中断请求、中断处理与中断返回。

(2)中断控制:

主要是实现中断优先级的排队和中断嵌套。

3.中断的主要用途

(1)实现输入/输出操作;

(2)电源掉电或其他情况的报警等。

4.可屏蔽中断与不可屏蔽中断

凡是微处理器内部能够“屏蔽”的中断,称为可屏蔽中断;

凡是微处理器内部不能“屏蔽”的中断,称为不可屏蔽中断。

7.1.2中断处理过程

1.CPU响应中断的条件

设置中断请求触发器

设置中断屏蔽触发器

CPU内部设置中断允许触发器的状态

CPU在现行指令结束后响应中断

具有中断屏蔽的接口电路:

2.CPU对中断的响应过程

进入中断周期后,中断响应的过程如下:

(1)关中断:

CPU在响应中断后,发出中断响应信号

,同时内部自动地关中断,以禁止接受其他的中断请求。

(2)保护断点:

把断点处的标志寄存器F的内容、段寄存器CS值和指令指针IP值依次压入堆栈保存,以便中断处理完后能正确地返回到主程序的断点地址,接着执行被中断的程序。

(3)识别中断源:

CPU要对中断请求进行处理,必须要找到相应中断服务程序(处理中断的程序)的入口地址,这就是中断源的识别。

(4)保护现场:

为了不使中断服务程序的运行影响主程序的状态,必须把断点处有关寄存器(指在中断服务程序中要使用的寄存器)内容压入堆栈保护。

(5)执行中断服务程序

(6)恢复现场:

即把中断服务程序压入堆栈的现场信息从堆栈中弹出来,并存入到原寄存器中,这是在中断服务程序中用POP指令来实现的。

(7)开中断与返回:

开放中断在返回之前,目的是返回主程序后能继续响应新的中断请求。

从中断返回到断点处,有一条专门的中断返回指令,该指令的隐操作是将堆栈栈顶处连续的3个字依次弹出给指令指针IP、段寄存器CS以及标志寄存器F。

7.1.38086/8088的中断系统

8086/8088的中断源:

1.外部中断

8086/8088有两条中断信号线——INTR和NMI

要结合PC机中断系统原理讲

(1)可屏蔽中断INTR

*可屏蔽中断请求线INTR通常由中断控制器82C59A驱动,该控制器又与需要中断服务的外部设备相连;

*CPU通过向82C59A写命令字来控制82C59A的工作;

*82C59A负责管理多个外设以中断方式与CPU交换数据;

*82C59A接收与其相连接的外部设备送来的中断请求,并判断提出中断请求的哪一个外部设备的优先级最高;

*82C59A向CPU提出中断申请。

*CPU对INTR中断请求的响应过程是执行两个

(中断响应)总线周期,

*在第一个中断响应周期内

信号通知82C59A,中断请求已被接受;

在第二个中断响应周期内

信号有效时,

*82C59A必须把请求服务的那个设备的中断类型码(0~255)送到数据总线,

*该中断类型码是在82C59A的初始化过程中由8086/8088写入的。

中断响应周期:

(2)不可屏蔽中断NMI

不可屏蔽中断请求信号NMI用来通知CPU发生了“灾难性”的事件,如电源掉电、存储器读写出错、总线奇偶位出错等。

NMI线上中断请求是不可屏蔽的,而且立即被CPU锁存,因此NMI是边沿触发的,不需要电平触发。

NMI的优先级比INTR高。

由于不可屏蔽中断的类型号预定为2,在CPU响应NMI时,不必由中断源提供中断类型码,因此,NMI响应也不需要执行中断响应总线周期。

2.内部中断

内部中断是通过软件调用的不可屏蔽中断,包括溢出中断、除法出错中断、

单步中断、INTn指令中断以及单字节INT3指令中断(断点中断)。

(1)溢出中断

如果上一条指令使溢出标志OF置“1”,那么在执行溢出中断指令(INTO)

时,立即产生一个4型中断(中断类型码为4)。

(2)除法出错中断

8086/8088的指令系统中有一条INT指令,当执行完这条指令就立即产生中

断。

CPU根据该指令中的中断类型码n,确定调用哪个服务程序来处理这个中断。

(3)INTn指令中断

8086/8088的指令系统中有一条INT指令,当执行完这条指令就立即产生中

断。

CPU根据该指令中的中断类型码n,确定调用哪个服务程序来处理这个

中断。

(4)断点中断(BreakpointInterrupt)

断点中断即单字节INT3指令中断,中断类型码为3,该中断是专供调试程序

设置断点所使用的,断点一般可以处于程序中的任何位置。

在断点处,停止当

前程序的执行,CPU按中断类型码为3来响应中断。

(5)单步(陷阱)中断

当陷阱标志TF置“1”时,8086/8088处于单步工作方式。

在单步工作时,每执行完一条指令,CPU就自动产生一个类型号为1的中断。

∆把标志寄存器和断点值(CS:

IP)压入堆栈

∆清除TF和IF

∆能逐条指令地观察系统操作的一个“窗口”

∆从堆栈中弹出原来的断点值(CS:

IP)及标志寄存器F的内容

∆使CPU返回单步方式

内部中断的特点

(1)中断类型码或者包含在指令中,或者是预先规定的;

(2)不执行响应外部中断的中断响应周期;

(3)除单步中断外,任何内部中断都无法禁止;

可以照讲义上讲

可以临时画一个简单的示意图

参考电子讲稿的图解释

黑板板书解释

(4)除单步中断外,任何内部中断的优先级都比外部中断的优先级高。

表7-1中断优先级

中断

优先级

除法出错、INTn、INTO

最高

NMI

…

INTR

…

单步

最低

3.中断向量表

∆中断向量表又称中断指针表,是存放中断服务程序入口地址(即“中断向

量”)的表格。

∆在存储器的最低端(0000H:

0000H~0000H:

03FFH)

∆可以存放256个中断服务程序的入口地址

∆共1024个字节,IP存放低地址,CS存放高地址

∆中断向量表示意图:

4.中断过程

∆当进入中断过程时,CPU把标志寄存器、CS和IP压入堆栈

∆清除TF和IF

∆执行中断服务内容

∆在执行中断服务内容之前,可以用STI指令重新开放外部中断,使INTR线上的中断请求能中断这个中断过程

∆所有的中断程序都应该以IRET指令结尾

∆IRET指令将栈顶的3个字分别弹出到IP、CS和标志寄存器中

7.2可编程中断控制器82C59A

*Inter82C59A是一种可编程中断控制器,

*一个82C59A可以管理8级中断

*每一级中断都可以屏蔽或允许

*82C59A在中断响应周期可提供相应的中断类型号,

*与所有Intel系列微处理机兼容;

*8级中断,通过级连可扩展至64级;

*单5V供电电压;

7.2.182C59A内部结构

1.数据总线缓冲器

8位的双向三态缓冲器,与CPU数据总线D7~D0直接连接,完成命令、状态信息的传送

2.读写控制逻辑

要结合多片级联使用的情况解释

该部件接收来自CPU的读写命令,完成规定的读写操作

3.中断请求寄存器IRR

IRR(InterruptRequestRegister)是与外部接口的中断请求线相连的寄存器

4.中断屏蔽寄存器IMR

IMR(InterruptMaskRegister)是—个8位寄存器,用来设置中断请求的屏蔽信息

IMR中第i位被屏蔽时(即IMRi=1),禁止IRi引脚发出的中断请求信号

5.中断服务寄存器ISR

ISR(InterruptServiceRegister)用于存放当前正在进行处理的中断源。

6.优先权电路

优先权电路(PriorityPR)负责检查中断源的中断请求的优先级,并与“正在服务中的中断”进行比较,确定是否将这个中断请求送给处理器

7.控制逻辑

控制逻辑按初始化设置的工作方式控制82C59A的全部工作

7.2.2中断处理过程

(1)当一条或多条中断请求线IR0~IR7变高时,设置相应的IRR位。

(2)PR对中断优先权和中断屏蔽寄存器的状态进行判断之后,如果某中断优先权最高且为允许中断状态,就向CPU发高电平中断申请信号INT。

(3)CPU响应中断时,送出中断响应信号

。

(4)82C59A接到来自CPU的第一个

信号时,当前中断服务寄存器(ISR)中相应位置位,并把IRR中相应位复位。

同时,82C59A准备向数据总线发送中断类型码。

(5)在82C59A发送中断类型码的最后—个

负脉冲期间,如果是在AEOI(自动结束中断)方式下,在这个

负脉冲结束时复位ISR的相应位。

在非自动中断结束方式下,ISR相应位要由中断服务程序结束时发出的EOI命令来复位。

7.2.382C59A引脚信号

1.与CPU的接口信号

(1)D0~D7、三态和8位双向数据线。

(2)

,写控制输入信号。

(3)

,读控制输入信号。

(4)A0,地址选择信号。

(5)

,片选输入信号,低电平有效。

(6)INT,由82C59A向CPU输出的中断请求信号。

(7)

,输入信号,接收CPU送来的中断响应信号。

引脚图:

2.与外部设备的接口信号

IR0~IR7共有8个中断请求输入信号,高电平或上升沿有效

用于接收外设接口的中断请求

3.级联时的接口信号

级联时的接口信号包括CAS0~CAS2

82C59A级联时使用,用来构成82C59A的主从式级联控制结构

7.2.4工作方式

4个初始化命令字(ICW1~ICW4)

三个操作命令字(OCW0~OCW4)

1.引入中断请求的方式

边沿触发方式:

以上升沿向82C59A请求中断,上升沿后可一直维持高电平,不会再产生中断。

电平触发方式:

以高电平申请中断,但在响应中断后必须及时清除高电平,以免引起第2次误中断。

中断查询方式:

外部设备通过82C59A申请中断,但82C59A却不使用INT信号向CPU申请中断,CPU用软件查询确定中断源,并为其服务。

2.连接系统总线的方式

在大系统中,要求数据总线有总线缓冲器

3.屏蔽中断源的方式

(1)普通屏蔽方式

利用操作命令字OCWl,使屏蔽寄存器IMR中的一位或数位置1来屏蔽一个或

数个中断源的中断请求。

若要开放某一个中断源的中断请求,则将IMR中相应

的位清0。

(2)特殊屏蔽方式

在某些场合,执行一个中断服务程序时,要求允许另一个优先级比它低的中断

请求被响应,此时可采用特殊屏蔽方式。

它可通过OCW3的D6D5=11来设定。

4.优先级排队的方式

(1)全嵌套方式

.在此种方式下,中断优先级按IR0~IR7顺序进行排队,只允许中断级别高的中断源去中断级别低的中断服务程序,但不能相反。

.这是82C59A最常用的方式。

若在对82C59A进行初始化以后,没有设置其他优先级方式,则自动按此方式工作。

(2)特殊全嵌套方式

.与全嵌套方式基本相同

.当执行某一级中断服务程序时,可响应同级的中断请求

.特殊全嵌套方式用于多片级联

(3)优先级自动循环方式

.优先级顺序不是固定不变的,一个设备得到中断服务后其优先级自动降为最低。

.其初始的优先级顺序规定为IR0,IR1,IR2,...IR7。

.该方式用于系统中多个中断源优先级相等的场合。

(4)优先级特殊循环方式

这种方式与优先级自动循环方式惟一的区别是,其初始的优先级顺序不是固定IR0为最高,然后开始循环,而是由程序指定IR0~IR7中任意一个为最高优先级,然后再按顺序自动循环,决定优先级。

5.结束中断的处理方式

(1)自动中断结束方式

.在中断服务程序中,中断返回之前,不需要发出中断结束命令就会自动清除该中断源所对应的ISR位

.在CPU发出第2个

信号时,82C59A即自动清除ISR中的对应位

.用于多个中断源不会产生嵌套的系统中

.不需要发EOC结束命令

(2)非自动中断结束方式

在中断服务程序返回之前,必须发出中断结束命令才能使ISR中的当前服务位清除:

.不指定中断源结束命令,即设置操作命令字OCW2=00100000B。

.指定中断结束命令,即设置OCW2=00100L2L1L0,其中的最低3位L2L1L0的编码,表示被指定要结束的中断。

7.2.5命令字和初始化编程

82C59A的输入输出端口地址:

1.初始化命令字

4个初始化命令字ICW1~ICW4:

(1)中断请求触发方式的设置及芯片数量选择的命令字(ICW1)

.A0=0

.D4=1

.D3(LTIM),设定中断请求信号的触发方式。

D3=1为电平触发,D3=0为边沿触发

.D2,在8086/8088系统中无意义,总是为0

.D1,单片使用或级联使用。

D1=1表示单片82C59A,D1=0表示多片级联

.D0,指出初始化程序中是否需要ICW4。

D0=1表示需要ICW4

例【7-1】

板书例子

(2)设置中断类型码高5位的初始化命令字(ICW2)

.中断响应总线周期向CPU提供的8位中断类型码。

.高5位T7~T3是由用户通过编程确定

.低3位,由82C59A内部电路自动产生,分别对应于8个中断源的中断请求信号IR0~IR7的编号,即IR0为000,IR1为001,……,IR7为111

.ICW2的格式--------------A0=1

(3)标识主片/从片初始化命令字(ICW3)

只有当系统中有多片82C59A级联时才需要设置ICW3

A0=1

主片ICW3格式:

举例解释

从片ICW3的格式:

举例解释

(4)方式控制初始化命令字(ICW4)

.当ICW1中的D0=1时,初始化82C59A时才需要写入ICW4

.ICW4也是写入奇地址

.ICW4的格式:

.D7~D5,ICW4的标志位,这3位为0。

.D4(SFNM),SFNM=1,当前82C59A工作于特殊全嵌套方式;SFNM=0,表示当前82C59A工作于普通全嵌套方式。

.D3(BUF),设置82C59A与系统的连接方式。

D3=1,表示采用缓冲方式。

.D2(M/

),级联方式设置:

当M/

=1时,表示该片为主片,M/

=0时,表示该片为从片。

.D1(AEOI),中断结束方式设置位。

当AEOI=l,82C59A设置为中断自动结束方式。

.D0(PM),PM=1,表示当前82C59A用于8位机以上的系统;PM=0,表示当前所在系统为8位机系统。

2.82C59A初始化编程逻辑

82C59A进入正常工作之前,系统必须对每个82C59A进行初始化设置。

初始化是通过编程将初始化命令字按顺序写入82C59A的端口实现的,82C59A的初始化流程:

例【7-2】某8086微机系统中有一片82C59A,中断请求信号为电平触发,中断类型码为40H~47H,中断优先级管理采用普通全嵌套方式,中断结束方式采用自动结束方式,系统中未使用数据缓冲器,系统分配给82C59A的端口地址为20H和21H,试对该82C59A进行初始化编程。

解:

单片82C59A

不需要ICW3

非缓冲方式

/

接+5V

对82C59A的初始化程序如下:

MOVAL,00011011B;设置ICW1初始化命令字

OUT20H,AL;将ICW1输出到偶地址端口

MOVAL,01000000B;ICW2中断类型号基值

OUT21H,AL;将ICW2送入奇地址端口

MOVAL,00000011B;ICW4

OUT21H,AL;将ICW4送入奇地址瑞口

3.操作命令字OCW

操作命令字是在82C59A工作过程中,根据某些操作要求,要改变82C59A的工作状态,对其进行控制的操作命令

(1)中断屏蔽操作命令字OCWl

OCWl用来实现对中断源的屏蔽功能,OCWl的内容被直接置入IMR屏蔽寄存器,其格式如下:

(2)优先级循环方式和中断结束方式操作命令字OCW2

OCW2有两个功能:

设置中断结束方式和优先级循环方式,要求写入偶地址端口,其格式如下图:

.D7(R),用于规定中断优先级是否设置为循环方式。

D7=1,为优先权循环方式;D7=0,为非循环方式。

.D6(SL),用于规定OCW2中的L2L1L0是否有效。

D6=l,表示D2~D0(L2L1L0)有效;D6=0,表示无效。

.D5(EOI),中断结束命令位。

D5=1,使中断服务寄存器中的对应位复位。

如前所述,如果ICW4中D1(AEOI)位为l,表示中断采用自动结束方式。

在中断自动结束方式下,当CPU第2个

负脉冲结束时,中断服务寄存器ISR中相应位会自动清除。

但如果AEOI为0,则ISRi位就要用EOI命令来消除。

EOI命令是通过OCW2中的D5位设置的。

.D4、D3,D4D3=00,OCW2的标志位。

.D2~D0(L2L1L0),有两个用途:

当OCW2给出特殊的中断结束命令时(即EOI=1,SL=1,R=0),L2、L1和L0指出具体应清除中断服务寄存器中的哪一位;当OCW2给出特殊的优先级循环方式命令时(即EOI=0,SL=1,R=1),L2、L1和L0指出循环开始时哪个中断的优先级最低

.下表归纳了对D7~D5位在各种编码下OCW2完成的功能

教材中将2写成1,两处错

举例解释:

(3)特殊屏蔽方式和中断查询方式操作命令OCW3

了解内容

OCW3有3个功能:

设置和撤消特殊屏蔽方式

设置中断查询方式

设置读出ISR或IRR寄存器的内容

OCW3的格式:

(1)用OCW3设置和撤消特殊屏蔽方式

(2)OCW3的中断查询功能

7.3习题

主要习题:

1.什么是中断向量?

中断向量位于存储器中的什么位置?

2.什么是中断类型码?

什么是中断响应周期?

3.8086CPU有哪几种中断?

简要说明8086中断的特点?

4.简述8086可屏蔽中断的响应过程。

5.82C59A芯片初始化的流程如何?

6.某一8086CPU系统中,采用一片82C59A进行中断管理。

设定82C59A工作在普通全嵌套方式,发送EOI命令结束中断,采用边沿触发方式请求中断,IR0对应的中断向量码为90H。

另外,82C59A在系统中的I/O地址是300H(A0=0)和301H(A0=1)。

请编写82C59A的初始化程序段。