最新EDA16x16点阵滚动+动画显示.docx

《最新EDA16x16点阵滚动+动画显示.docx》由会员分享,可在线阅读,更多相关《最新EDA16x16点阵滚动+动画显示.docx(9页珍藏版)》请在冰豆网上搜索。

最新EDA16x16点阵滚动+动画显示

EDA16x16点阵滚动+动画显示

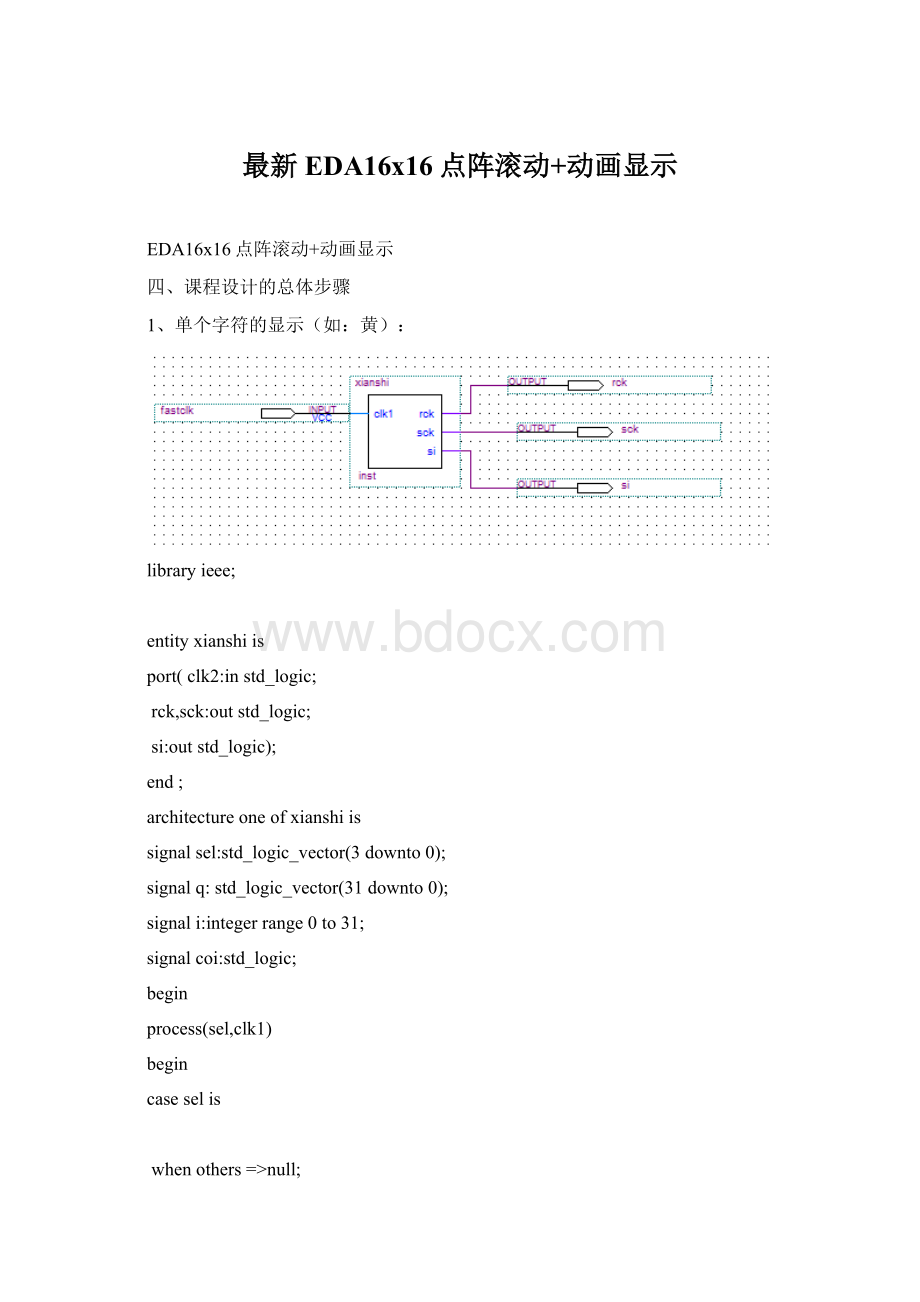

四、课程设计的总体步骤

1、单个字符的显示(如:

黄):

libraryieee;

entityxianshiis

port(clk2:

instd_logic;

rck,sck:

outstd_logic;

si:

outstd_logic);

end;

architectureoneofxianshiis

signalsel:

std_logic_vector(3downto0);

signalq:

std_logic_vector(31downto0);

signali:

integerrange0to31;

signalcoi:

std_logic;

begin

process(sel,clk1)

begin

caseselis

whenothers=>null;

endcase;

ifclk1'eventandclk1='1'then

si<=q(i);i<=i+1;coi<='0';

ifi=31theni<=0;coi<='1';sel<=sel+'1';

endif;

rck<=notcoi;

endif;

endprocess;

sck<=clk1;

end;

时序仿真:

从图中可以看出,当clk1在第32个上升沿rck变为低电频,sck与clk1是同一电频,故此程序满足要求。

2、多个字符的跳动显示(如:

黄小红):

libraryieee;

entityxianshiis

port(clk1:

instd_logic;

clk2:

instd_logic;

rck,sck:

outstd_logic;

si:

outstd_logic);

end;

architectureoneofxianshiis

signallie:

std_logic_vector(3downto0);

signalsel:

std_logic_vector(3downto0);

signalq:

std_logic_vector(31downto0);

signali:

integerrange0to31;

signalcoi:

std_logic;

begin

process(sel,clk1,clk2)

begin

ifclk2'eventandclk2='1'then

lie<=lie+'1';

endif;

caselieis

when"0000"=>

caseselis

whenothers=>null;

endcase;

when"0001"=>

caseselis

whenothers=>null;

endcase;

when"0010"=>

caseselis

whenothers=>null;

endcase;

whenothers=>null;

endcase;

ifclk1'eventandclk1='1'then

si<=q(i);i<=i+1;coi<='0';

ifi=31theni<=0;coi<='1';sel<=sel+'1';

endif;

rck<=notcoi;

endif;

endprocess;

sck<=clk1;

end;

时序仿真:

从上图看出,当clk1在第32个上升沿rck变为低电频,sck与clk1是同一电频,故此程序满足要求。

3、汉字的滚动和动画显示(如:

黄小红+笑脸):

libraryieee;

entityxianshiis

port(clk1:

instd_logic;

clk2:

instd_logic;

rck,sck:

outstd_logic;

si:

outstd_logic);

end;

architectureoneofxianshiis

signallie:

std_logic_vector(3downto0);

signalsel:

std_logic_vector(3downto0);

signalq:

std_logic_vector(31downto0);

signali:

integerrange0to31;

signalcoi:

std_logic;

begin

process(sel,clk1,clk2)

begin

ifclk2'eventandclk2='1'then

lie<=lie+'1';

endif;

caselieis

when"0000"=>

caseselis

whenothers=>null;

endcase;

when"0001"=>

caseselis

whenothers=>null;

endcase;

when"0010"=>

caseselis

whenothers=>null;

endcase;

when"0011"=>

caseselis

whenothers=>null;

endcase;

when"0100"=>

caseselis

whenothers=>null;

endcase;

when"0101"=>

caseselis

whenothers=>null;

endcase;

when"0110"=>

caseselis

whenothers=>null;

endcase;

when"0111"=>

caseselis

whenothers=>null;

endcase;

when"1000"=>

caseselis

whenothers=>null;

endcase;

when"1001"=>

caseselis

whenothers=>null;

endcase;

when"1010"=>

caseselis

whenothers=>null;

endcase;

when"1011"=>

caseselis

whenothers=>null;

endcase;

when"1100"=>

caseselis

whenothers=>null;

endcase;

when"1101"=>

caseselis

whenothers=>null;

endcase;

when"1110"=>

caseselis

whenothers=>null;

endcase;

when"1111"=>

caseselis

whenothers=>null;

endcase;

whenothers=>null;

endcase;

ifclk1'eventandclk1='1'then

si<=q(i);i<=i+1;coi<='0';

ifi=31theni<=0;coi<='1';sel<=sel+'1';

endif;

rck<=notcoi;

endif;

endprocess;

sck<=clk1;

end;

时序仿真:

从上图看出,当clk1在第32个上升沿rck变为低电频,sck与clk1是同一电频,si为输出电频,故此程序满足要求。

五、结论与收获

在三周的EDA课程设计过程中,我对VHDL语言有了更加深刻的认识。

VHDL是超高速集成电路的硬件描述语言,它能够描述硬件的结构、行为与功能。

另外,VHDL具有并发性,采用自上而下的结构式设计方法,适合大型设计工程的分工合作。

在编写程序的时候,我才发现能看懂程序和能自己写程序是两个完全不同的概念,自己一开始写程序时,即便是一个很简单的功能模块,在编译时也可能产生很多错误,在不断的改错过程中,自己对VHDL语言的语法结构有了深刻的理解,对编译过程中常见的错误也有了全面的认识。

通过这十三周的课程设计,我在熟悉了基于FPGA设计的同时,也学到了很多在学习课本知识时所体会不到的东西。

完成此次设计后,我不仅能对QuartusII开发仿真软件熟练操作,能达到学以致用,同时还掌握了矩阵键盘和16×16点阵的工作原理。

经过这一过程,我发现平常的学习在注重理论知识的掌握同时,要加强实验环节,只有通过不断地实践,我们才能把知识掌握的更牢固,理解的更透彻。

通过这次课程设计使我懂得了理论与实际相结合是很重要的,只有理论知识是远远不够的,只有把所学的理论知识与实践相结合起来,从理论中得出结论,才能真正为社会服务,从而提高自己的实际动手能力和独立思考的能力。

在设计的过程中遇到问题,可以说得是困难重重,这毕竟第一次做的,难免会遇到过各种各样的问题,同时在设计的过程中发现了自己的不足之处,对以前所学过的知识理解得不够深刻,掌握得不够牢固。