verilog串并转换并串转换.docx

《verilog串并转换并串转换.docx》由会员分享,可在线阅读,更多相关《verilog串并转换并串转换.docx(35页珍藏版)》请在冰豆网上搜索。

verilog串并转换并串转换

1.

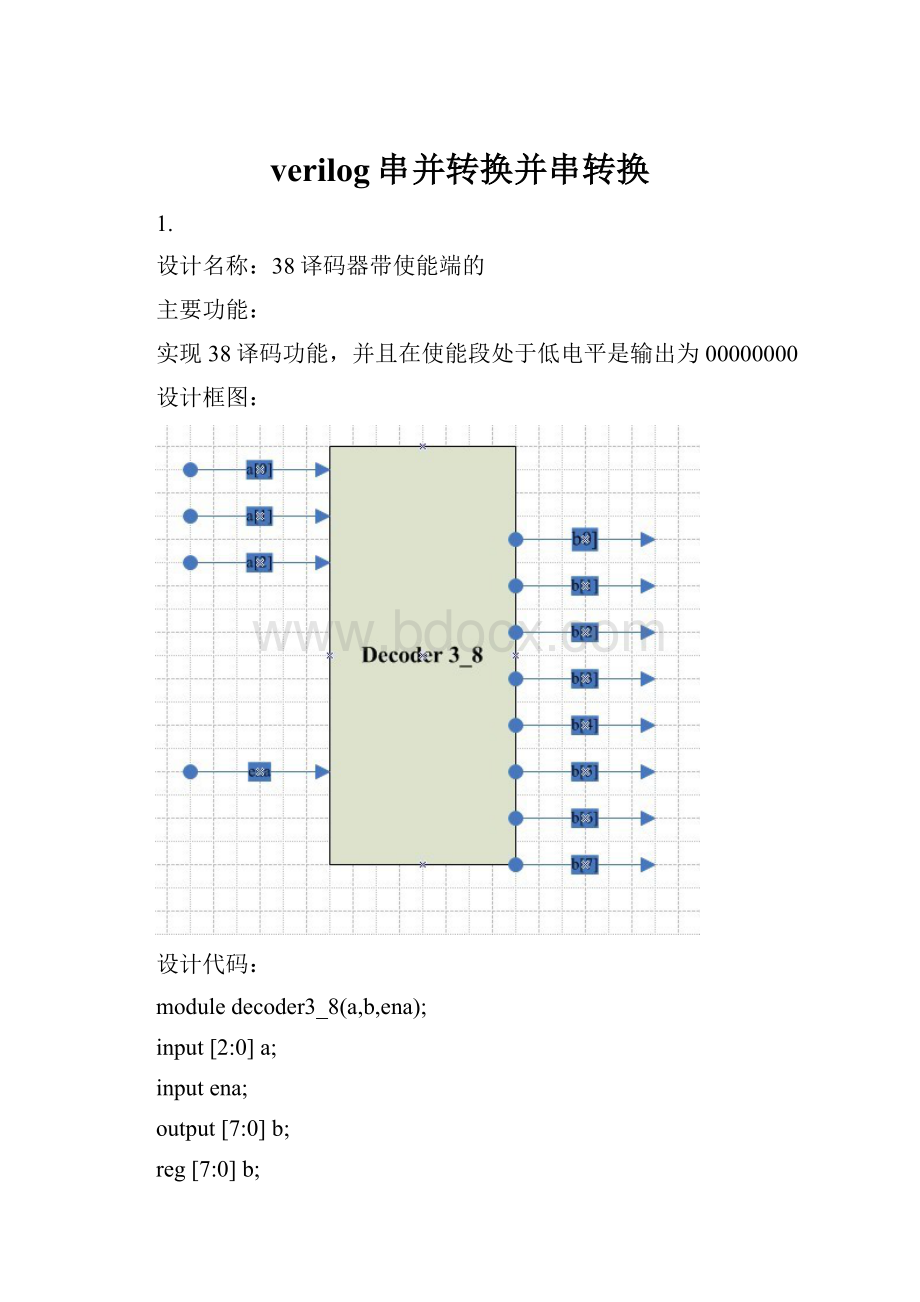

设计名称:

38译码器带使能端的

主要功能:

实现38译码功能,并且在使能段处于低电平是输出为00000000

设计框图:

设计代码:

moduledecoder3_8(a,b,ena);

input[2:

0]a;

inputena;

output[7:

0]b;

reg[7:

0]b;

always@(ena,a)

if(!

ena)

begin

b=8'b00000000;

end

else

begin

case(a)

3'b000:

b=8'b00000001;

3'b001:

b=8'b00000010;

3'b010:

b=8'b00000100;

3'b011:

b=8'b00001000;

3'b100:

b=8'b00010000;

3'b101:

b=8'b00100000;

3'b110:

b=8'b01000000;

3'b111:

b=8'b10000000;

default:

b=8'b00000000;

endcase

end

endmodule

仿真代码:

`timescale1ns/1ns

moduletb;

reg[2:

0]a;

regena;

wire[7:

0]b;

initialbegin

a=3'b000;

ena=1'b0;

#50;

ena=1'b1;

#50;

a=3'b001;

#50;

a=3'b010;

#50;

a=3'b011;

#50;

a=3'b100;

#50;

a=3'b101;

#50;

a=3'b110;

#50;

a=3'b111;

#50;

$stop;

end

decoder3_8udecoder3_8(

.a(a),

.ena(ena),

.b(b)

);

endmodule

仿真结果:

辅助说明:

当ena为低电平时,无论a为何值,总是输出00000000,当ena为高电平时,输出即随a的数值变化而变化,当a为001时,b的值变为00000010;当a为010时,b的值变为00000100,这与设计时的功能是一致的。

_______________________________________________________________________________

2.

设计名称:

83编码器带使能端的和优先级

主要功能:

实现83编码功能,并且在使能段处于低电平是输出为000,同时最高位的优先级最高

设计框图:

设计代码:

moduleundecoder8_3(a,b,ena);

input[7:

0]a;

inputena;

output[3:

0]b;

reg[3:

0]b;

always@(ena,a)

if(!

ena)

begin

b=3'b000;

end

else

if(a[7])b=3'b111;

else

if(a[6])b=3'b110;

else

if(a[5])b=3'b101;

else

if(a[4])b=3'b100;

else

if(a[3])b=3'b011;

else

if(a[2])b=3'b010;

else

if(a[1])b=3'b001;

else

if(a[0])b=3'b000;

elseb=3'b000;

endmodule

仿真代码:

moduletb;

reg[7:

0]a;

regena;

wire[2:

0]b;

initialbegin

a=8'b10000000;

ena=1'b0;

#50;

ena=1'b1;

#50;

a=8'b01000000;

#50;

a=8'b00100000;

#50;

a=8'b00010000;

#50;

a=8'b00001000;

#50;

a=8'b00000010;

#50;

a=8'b00000001;

#50;

a=8'b10100000;

#50;

$stop;

end

undecoder8_3unit1_undecoder8_3(

.a(a),

.ena(ena),

.b(b)

);

endmodule

仿真结果:

辅助说明:

当ena为低电平时,无论a为何值,总是输出000,当ena为高电平时,输出即随a的数值变化而变化,当a为01000000时,b为110,当a为00100000是,b为101以此类推,同时最后一个波形为,当a为10100000时,b为111,体现了优先译码的功能,此结果和当初设计的功能一致的。

_______________________________________________________________________________

3.

设计名称:

设计一个1:

1的3分频器

主要功能:

实现3分频,同时高低电平比为1:

1

设计框图:

设计代码:

这个设计可以利用模三计数器分别在时钟的上升和下降沿设计一个高低电平为1:

2的3分频,然后将两个波形相或即能得到结果。

代码一:

moduleDevider2_1(

//inputs

clk,

rst_n,

//outputs

opt1,

opt2,

opt);

inputclk;

inputrst_n;

outputopt;

outputopt1;

outputopt2;

regopt1;

reg[1:

0]temp1;

regopt2;

reg[1:

0]temp2;

always@(posedgeclk)

begin

if(!

rst_n)

begin

temp1<=2'd0;

opt1<=1'b0;

end

elseif(temp1==1)

begin

opt1<=1'b1;

temp1<=temp1+2'd1;

end

elseif(temp1==2'd2)

begin

opt1<=1'b0;

temp1<=2'd0;

end

else

begin

temp1<=temp1+2'd1;

end

end

always@(negedgeclk)

begin

if(!

rst_n)

begin

temp2<=2'd0;

opt2<=1'b0;

end

elseif(temp2==1)begin

opt2<=1'b1;

temp2<=temp2+2'd1;

end

elseif(temp2==2'd2)

begin

opt2<=1'b0;

temp2<=2'd0;

end

else

begin

temp2<=temp2+2'd1;

end

end

assignopt=opt1||opt2;

endmodule

同时也可以用同样的方法设计一个在上升和下降沿高低电平2:

1的3分频器,将两个波形相与即可。

代码二:

moduleDevider2_1(

//inputs

clk,

rst_n,

//outputs

opt1,

opt2,

opt);

inputclk;

inputrst_n;

outputopt;

outputopt1;

outputopt2;

regopt1;

regopt2;

reg[1:

0]temp1;

reg[1:

0]temp2;

always@(posedgeclk)

begin

if(!

rst_n)

begin

temp1<=2'd0;

opt1<=1'b0;

end//reset

elseif(temp1==2'd0)

begin

opt1<=1'b1;

temp1<=temp1+2'd1;

end

elseif(temp1==2'd1)

begin

opt1<=1'b1;

temp1<=temp1+2'd1;

end

elseif(temp1==2'd2)

begin

opt1<=1'b0;

temp1<=2'd0;

end

end

always@(negedgeclk)

begin

if(!

rst_n)

begin

temp2<=2'd0;

opt2<=1'b0;

end//reset

elseif(temp2==2'd0)

begin

opt2<=1'b1;

temp2<=temp2+2'd1;

end

elseif(temp2==2'd1)

begin

opt2<=1'b1;

temp2<=temp2+2'd1;

end

elseif(temp2==2'd2)

begin

opt2<=1'b0;

temp2<=2'd0;

end

end

assignopt=opt1&&opt2;

endmodule

仿真代码:

上面两个代码的仿真代码是一样的。

`timescale1ns/1ns

moduletb;

//inputs

regclk;

regrst_n;

//outputs

wireopt1;

wireopt2;

wireopt;

//generateclk

always#10clk=~clk;

//tbstarts

Initial

begin

clk=1'b0;

rst_n=1'b0;

#100;

rst_n=1'b1;

#500;

$stop;

end

//InstantDUT

Devider2_1uDevider2_1(

//inputs

.clk(clk),

.rst_n(rst_n),

//outputs

.opt1(opt1),

.opt2(opt2),

.opt(opt)

);

endmodule

仿真结果:

(a)高低电平为1:

2设计的

(b)高低电平为2:

1设计的

辅助说明:

(a)中opt1为上升沿触发的高低电平1:

2的3分频,opt2为下降沿触发的高低电平为1:

2的3分频,可以看出在rst_n为0进行清复位,之后在rst_n为1是进行分频,最后所得opt结果为1:

1的3分频,符合设计要求。

(b)中opt1为上升沿触发的高低电平2:

1的3分频,opt2为下降沿触发的高低电平为2:

1的3分频,可以看出在rst_n为0进行清复位,之后在rst_n为1是进行分频,最后所得opt结果为1:

1的3分频,符合设计要求。

_______________________________________________________________________________

4.

设计名称:

七人表决器

主要功能:

7个人进行表决,人数过4则LED灯亮,否则灯灭

设计框图:

设计代码:

modulev(vote,rst,Q);

input[6:

0]vote;

inputrst;

outputQ;

regQ;

reg[2:

0]c;

always@(voteorrst)

begin

c=0;

if(rst)

c=3'b000;

else

begin

c=c+vote[0];

c=c+vote[1];

c=c+vote[2];

c=c+vote[3];

c=c+vote[4];

c=c+vote[5];

c=c+vote[6];

end

if(c>3)Q=1;

elseQ=0;

end

endmodule

仿真代码:

`timescale1ns/1ns

moduleq;

regrst;

reg[6:

0]vote;

wireQ;

initialbegin

rst=0;

vote=7'b111111;

#50;rst=1;

#50;rst=0;

#50;vote=7'b0110101;

#50;vote=7'b0100101;

#50;vote=7'b0111101;

#50;vote=7'b1111001;

#50;vote=7'b0100001;

#50;vote=7'b0000001;

#50;$stop;

end

vv_unit(

.vote(vote),

.rst(rst),

.Q(Q));

endmodule

仿真结果:

辅助说明:

第一个表决为0111111,有6人同意,于是显示通过,Q为高电平,第二个单位是,rst复位信号显示为1,此时对表决器复位,于是Q清0,后面当rst为低电平时又可以开始表决,当最后一个表决信号只有1个人同意时,由于人数少于4,所以Q为0,不通过,结果与设计相仿。

_______________________________________________________________________________

5

设计名称:

十进制计数器的设计

主要功能:

使能端为高电平且复位信号为低电平是,进行模十同步计数,同时满10的时候清0并且进位co置1,在一个始终后默认高位已经接受完进位信号将其清0。

使能端为低电平时计数器保持输出不变,当使能端为高电平,且复位信号为高电平时,将计数器异步清0.

设计框图:

设计代码:

moduleten(clk,rst_tong,rst_yi,a,co,ena);

inputclk;

inputrst_tong;

inputrst_yi;

inputena;

output[3:

0]a;

outputco;

reg[3:

0]a;

regco;

always@(posedgeclkorposedgerst_yi)

begin

co<=0;

if(rst_yi)

begin

a<=4'b0000;

co<=0;

end

if(!

ena)

begin

co<=0;

end

else

begin

if(rst_tong)

begin

a<=4'b0000;

co<=0;

end

else

if(a<4'b1001)

a<=a+4'b0001;

else

if(a==4'b1001)

begin

a<=4'b0000;

co<=1;

end

end

end

endmodule

仿真代码:

`timescale1ns/1ns

moduletb;

regclk;

regrst_yi;

regena;

regrst_tong;

wire[3:

0]a;

wireco;

always#10clk=~clk;

initialbegin

ena=0;

clk=1'b0;

rst_yi=1'b1;

rst_tong=1'b0;

#10;

ena=1;

#14;

rst_yi=1'b0;

#230;

rst_yi=1'b1;

#20;

rst_yi=1'b0;

#20;

ena=0;

#30;

rst_tong=1'b1;

#500;

$stop;

end

tenten_unit(.clk(clk),

.rst_yi(rst_yi),

.rst_tong(rst_tong),

.ena(ena),

.a(a),

.co(co)

);

endmodule

仿真结果:

辅助说明:

这个十进制计数器里面我设计了两个复位端口,一个是同步复位端口rst_tong,一个是异步复位端口rst_yi,从仿真图形中可以看出,在使能端ena为低是计数器保持数值不变,输出全是0,当使能端ena为高电平的时候,当异步复位rst_yi为高电平是实现异步清零,这个可以在rst_yi的第二个高电平处看清楚,当rst_yi为低电平时,若rst_tong为低电平,实现正常计数,此时从0000计数到1001,在下一个时钟周期产生一个半个周期的进位高电平co,在并且计数a重新变为0,当rst-tong为高电平时,在时钟的上升沿进行同步置数此功能和当初的设计目标一致。

_______________________________________________________________________________

6:

设计名称:

4路抢答器

主要功能:

完成抢答功能,并且在抢答结束的时候清0,在下一次抢答开始之前按抢答键无效。

设计框图:

设计代码:

moduleqiang(a,b,start);

input[3:

0]a;

inputstart;

output[3:

0]b;

reg[3:

0]b;

reg[3:

0]temp;

always@(aorstart)

begin

if(!

start)

begin

temp=0;

b=0;

end

else

if(temp==4'b0000)

begin

temp=a;

b=temp;

end

end

endmodule

仿真代码:

`timescale1ns/1ns

moduletb;

reg[3:

0]a;

regstart;

wire[3:

0]b;

initialbegin

start=0;

a=4'b0000;

#10;

start=1;

#10;

a=4'b0100;

#10;

a=4'b0110;

#50;start=0;

#10;a=4'b0100;

#30;a=4'b0000;

#50;start=1;

#50;a=4'b1000;

#50;

$stop;

end

qiangqiang_unit(

.a(a),

.start(start),

.b(b)

);

Endmodule

仿真结果:

辅助说明:

可以看出,当start为0,抢答器未启动时,输出为0000,当start为1时,此时a=0010,表明第二个人已经先按下抢答器,这是输出为0010,之后a=0110,又有人再次之后按下抢答器,但是由于a【1】已经先按下,所以a【2】按下后还是只能显示0010,这就实现了抢答功能,当start=0是,这是输出清零,这是输入0100,由于抢答器未工作,所以输出还是0000,后面当start又是1的时候,这时候a【3】抢答成功,所输出又为1000,符合当初的设计功能。

7.

设计名称:

并串转换

主要功能:

在没有数据输出时,输出为x,此时ready信号为高,若load信号也为高时,则将输入的数据传输给中间寄存器temp,然后resdy信号变为低电平,ready信号有temp【7】决定,当

temp【7】中还有数据时,表明还没有全部转换完,则ready为低,当temp【7】没有数据显示为x时,则ready为高,表明可以接收数据了。

当接收完数据之后,在8个时钟周期将信号输出。

设计框图:

设计代码:

modulebcc(clk,ain,rst,bout,load,ready);

inputclk;

input[7:

0]ain;

inputrst;

inputload;

outputbout;

outputready;

regbout;

reg[7:

0]temp;

regready;

always@(posedgerstorposedgeclk)

begin

if(rst)

begin

bout<=1'bx;

temp<=8'bxxxxxxxx;

ready<=1;

end

else

if(load&&ready)

temp<=ain;//ifloadishighleveandtempisempty,then,transportdata

if(temp[7]||!

temp[7])//temp[7]hasdata

begin

bout<=temp[7];

//tempshiftleft,andtemp[0]equalx

temp[7:

1]<=temp[6:

0];

temp[0]<=1'bx;

ready<=0;

end

else

begin

bout<=1'bx;

ready<=1;

end

end

endmodule

仿真代码:

`timescale1ns/1ns

modulebcc_tb;

regclk;

reg[7:

0]ain;

regrst;

regload;

wireready;

wirebout;

always#10clk=~clk;

initial

begin

clk=0;

rst=1;

load=0;

ain=11;

#10;

rst=0;

#10;

load=1;

#20;

load=0;

#20;

ain=8;

#40;

load=1;

#20;

load=0;

#100;

load=1;

#20;

load=0;

#200;

rst=1;

#10;

$stop;

end

bccbcc_unit(

.clk(clk),

.ain(ain),

.rst(rst),

.load(load),

.bout(bout),

.ready(ready)

);

Endmodule

仿真结果:

辅助说明:

可以从仿真图形中看出,在rst为高时,进行复位,当rst为低时,由于temp里面没有数据,所以ready信号为高,此时表明temp可以接受数据,若load信号为高,之后temp则接收到ain的信号,此时temp里面有了数据,则ready信号为0,不能再传输数据,此时后8个时钟周期输出为00001011,完成串并转换,期间就算load为高电平,但是ready信号为低,所以不会传输下一个数据00001000,只有当之后ready为高电平时,此时财货执行下一个数据的传输。

此仿真