数字电子技术期末考试试题含答案.docx

《数字电子技术期末考试试题含答案.docx》由会员分享,可在线阅读,更多相关《数字电子技术期末考试试题含答案.docx(15页珍藏版)》请在冰豆网上搜索。

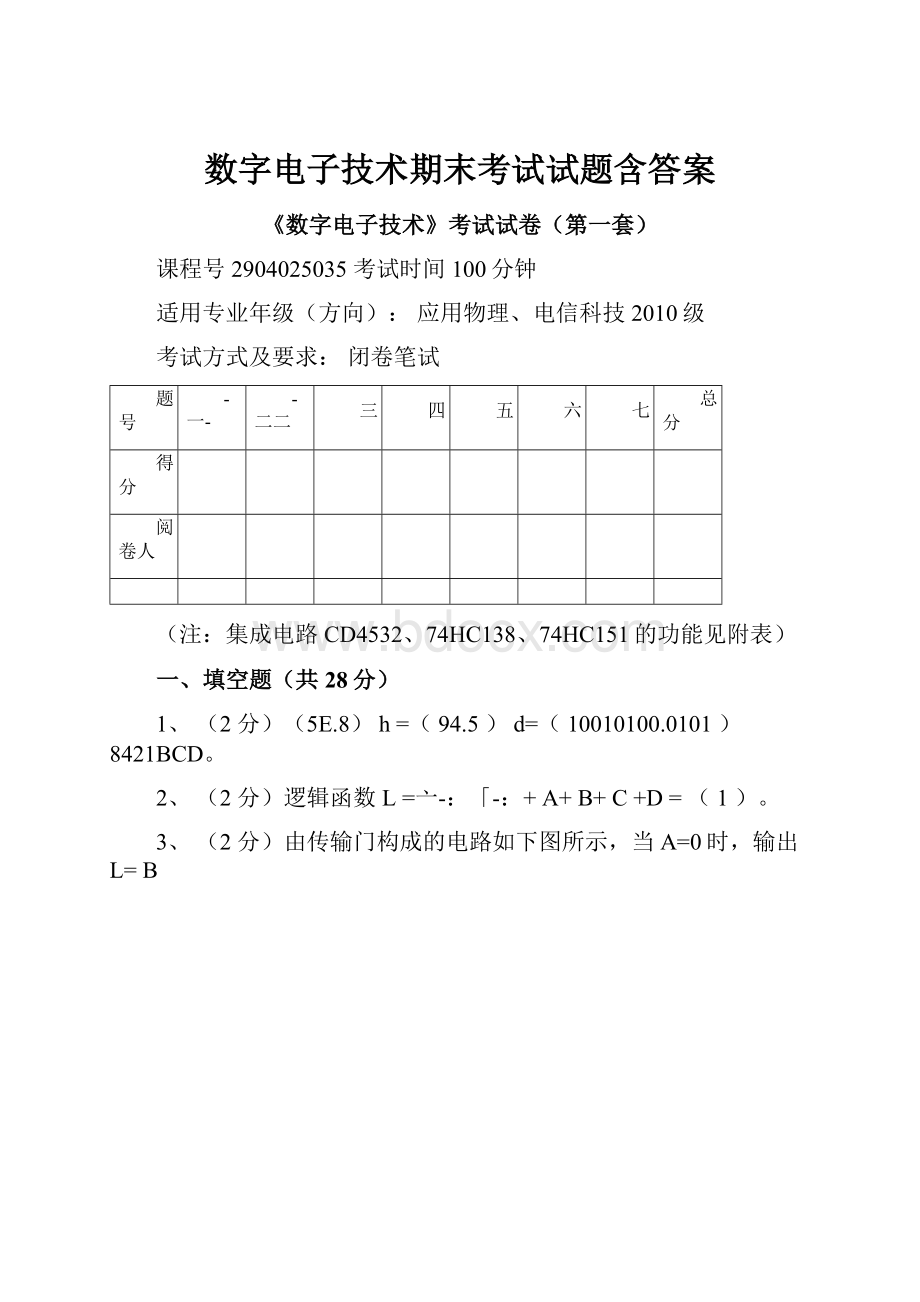

数字电子技术期末考试试题含答案

《数字电子技术》考试试卷(第一套)

课程号2904025035考试时间100分钟

适用专业年级(方向):

应用物理、电信科技2010级

考试方式及要求:

闭卷笔试

题号

-一-

-二二

三

四

五

六

七

总分

得分

阅卷人

(注:

集成电路CD4532、74HC138、74HC151的功能见附表)

一、填空题(共28分)

1、(2分)(5E.8)h=(94.5)d=(10010100.0101)8421BCD。

2、(2分)逻辑函数L=亠-:

「-:

+A+B+C+D=

(1)。

3、(2分)由传输门构成的电路如下图所示,当A=0时,输出L=B

4、(2分)三态门可能输出的三种状态是低电平、高电平和高阻态_。

5、(3分)A/D转换器一般要经过_采样_、保持、量化和_编码—这4

个步骤,A/D转换器的转换速度主要取决于转换类型。

对双积分型A/D1

i转换器、并行比较型A/D转换器和逐次比较型A/D转换器的相对速度进|行比较,转换速度最快的是―并行比较型A/D转换器__。

I

6、(2分)集成优先编码器CD4532(功能表见后)正常接电源和地,且|待编码信号输入端Io=I2=I6=I7=1,输入使能端EI=1,其余输入端为0,其输出丫2丫1丫0为111。

I

7、(3分)集成数据选择器74HC151构成的电路如下图所示,则其输I出I

I

Y=ABCABCABC。

(注:

不需化简)

丫

1

0T

E

丫

A—

S2

74HC151

B—

S1

S0

D

0

D1D2D

3D4D5D6D7

0—

JLU

1i

J

(

•

8、(3分)某PLA电路如下图所示,其输出逻辑函数表达式X=|

ABCABCABC。

ABC

XY

9、(2分)某单极性输出的8位D/A转换器正常工作,当输入数字量为

(10101010)B时,其输出电压为3.4V,当输入数字量为(10101100)

b时,其输出电压为3.44V。

10、(2分)一个存储容量为4KX4

的存储器有

214个存储单

元,若用该存储器构成32KX8

的存储系统,则需

16片4KX4

的存储器。

11、(3分)对于JK触发器,当JK

1时,Qn+1=

1,当JK1

时,Qn+1=Qn,当J

K0时,Qn+1=

Qn。

(12分)

一、用公式法将卜列逻辑函数化简为最简与或式

F(A,B,C,D)ABCDABD

BCBCDABC

F=AB(C+D)+B(C+D)+ABC

2分

=ABC+ABD+BD+BC+AbC

2分

=ABC+ABD+BD+BC

2分

=B(AC+C+AD+D)

2分

=B(A+C+D)

2分

=AB+BC+BD

2分

三、用卡诺图法将下列逻辑函数化简为最简与或式(10分)

L(A,B,C,D)=Xm(0,1,3,5,7,9)+刀d(10~15)

\CD

AB'

00

01

11

10

00

J1

*

1

01

1

1

11

X

X

X

X

10

1

X

X

LDABC

四、(16分)在举重比赛中有A、B、C三名裁判,A为主裁判,B、C为副裁判。

当两名或两名以上裁判(且必须包括A在

内)认为运动员上举杠铃合格时,按动电钮可发出裁决合格信号(即输出Z为1)。

请设计该三输入的组合逻辑电路。

要求:

(1)列出真值表;

(2)写出逻辑函数的最简与或式;

(3)用与非门实现该电路,画出电路图;

(4)用3线8线译码器74HC138实现该电路,画出电路图。

74HC138的符

O123456Y

YYYYYYYY

E3

E2

E1

74HCL38

A2

A1

A0

解:

(1)真值表见表1,设输入为A、B、C,输出为F

(2)逻辑函数的最简与或式;

FABCABCABCABAC

(3)用与非门实现

FABACABAC

用与非门实现该电路的逻辑图如图(a)所示。

(4)用74HC138实现

A、B、C从A、Ai、Ao输入,令E31,E2Ei0

FABCABCABCm^m6m7m6m7Y5Y6Y7

用74HC138实现该电路的逻辑图如图(b)所示。

表1真值表

ABC

F

000

0

001

0

010

0

011

0

100

0

101

1

五、(20分)分析下图所示时序电路,写出其驱动方程、状态方程和输

出方程,画出其状态转换表、状态转换图,检查电路能否自启动,

并说明电路实现的逻辑功能。

CP—»

输出方程:

ZXQinQ;

状态表:

Q;Q;

Q?

1Q01/Z

X=0

X=1

00

00/0

01/0

01

01/0

10/0

10

10/0

11/0

11

11/0

00/1

状态图:

0/0

自启动能力:

具有自启动能力

逻辑功能:

X=0时,电路处于维持状态;

X=1时,电路为四进制加法计数器

六、(10分)使用4位同步二进制加计数器74LVC161构成模值为10的计

数器,要求画出接线图和状态转换图。

注:

D3、Q3为高位,Do、Qo为低位。

解:

N=10,N<16,所以只需一片74LVC161。

方法一:

反馈清零法,计数状态为0000-1009;

方法二:

反馈置数法,计数状态为0000-1009;

状态转换图:

CRD0D1D2D3

CETTC

cep74LVC161

PE

,CPQ0Q1QpQ3

方法

1111

1110

1101

coon

OOOil

0011

OlOO

1100

1011

1010

1001

mm

100C

0111

方法

七、(10分)请绘制由555定时器构成的施密特触发器的电路图。

若输入U的波形如下图所示,又知Vcc=15V,5脚不外加

控制电压。

求正向閾值电压Vt+,负向閾值电压Vt-,并画出

该电路输出Uo的波形

555定时器的符号

555定时器构成的施密特触发器的电路及输出Uo的波形如下图。

I

1

V«'

附表

附表1:

集成优先编码器CD4532功能表

输入

输出

i

EI

|7

|6|5

|4|3

|2|1

|o

丫2

Yi

Yo

GS

EO

i

L

X

X

X

XX

XX

X

L

L

L

L

L

1

i

H

L

L

L

LL

LL

L

L

L

L

L

H

i

H

H

X

X

XX

XX

X

H

H

H

H

L

i

1

H

L

H

X

XX

XX

X

H

H

L

H

L

II

i

H

L

L

H

XX

XX

X

H

L

H

H

L

i

H

L

L

L

HX

XX

X

H

L

L

H

L

1

i

H

L

L

L

LH

XX

X

L

H

H

H

L

i

H

L

L

L

LL

HX

X

L

H

L

H

L

i

1

H

L

L

L

LL

LH

X

L

L

H

H

L

II

i

HLLLLLLLH

LLLHL

附表1:

集成8选1数据选择器74HC151的功能表

输入

输出

使能E

选择

S2S1SO

YY

H

XXX

LH

L

LLL

DODO

L

LLH

D1D1

L

LHL

D2D2

L

LHH

D3D3

L

HLL

D4D4

L

HLH

D5D5

L

HHL

D6D6

L

HHH

D7D7

附表2集成3线8线译码器74HC138的功能表

西

南石油

大

学

试

卷

第12页

共13

输

入

输

出

E3

E

2El

A2

Ai

Ao

Yo

Yi

丫2

丫3

丫4

丫5

丫6

丫7

X

H

X

X

X

X

H

H

H

H

H

H

H

H

X

X

H

X

X

X

H

H

H

H

H

H

H

H

L

X

X

X

X

X

H

H

H

H

H

H

H

H

H

L

L

L

L

L

L

H

H

H

H

H

H

H

H

L

L

L

L

H

H

L

H

H

H

H

H

H

H

L

L

L

H

L

H

H

L

H

H

H

H

H

H

L

L

L

H

H

H

H

H

L

H

H

H

H

H

L

L

H

L

L

H

H

H

H

L

H

H

H

H

L

L

H

L

H

H

H

H

H

H

L

H

H

H

L

L

H

H

L

H

H

H

H

H

H

L

H

H

L

L

H

H

H

H

H

H

H

H

H

H

L

附表3集成同步四位二进制加计数器74LVC161的功能表

清零

CR

预置

PE

使能

时钟

CP

预置数据输入

Q3

Q2

Qi

Qo

进位

TC

CEP

CET

D3

D2

Di

Do

L

X

X

X

X

X

X

X

X

L

L

L

L

L

H

L

X

X

D3*

*

D2

*

Di

*

Do

D3

D2

Di

Do

#

H

H

L

X

X

X

X

X

X

保

持

#

H

H

H

L

X

X

X

X

X

保

持

L

H

H

H

H

X

X

X

X

计

数

#

输出

输入

注:

Dn*表示CP脉冲上升沿之前瞬间Dn的电平,#表示只有当CET为高电平且计数器状态为HHHH时输出为高电平,其余均为低电平。

附表4555定时器的功能表

输入

输出

阈值输入(6脚)

触发输入(2脚)

复位(4脚)

输出(3脚)

放电管T

X

X

0

0

导通

v2Vcc

3

vVCC

3

1

1

截止

2Vcc

>

3

VCC

>

3

1

0

导通

2Vcc

<

3

VCC

>

3

1

不变

不变

注:

5脚悬空(或经电容接地)时