数电研讨用CMOS传输门和CMOS非门设计边沿D触发器.docx

《数电研讨用CMOS传输门和CMOS非门设计边沿D触发器.docx》由会员分享,可在线阅读,更多相关《数电研讨用CMOS传输门和CMOS非门设计边沿D触发器.docx(14页珍藏版)》请在冰豆网上搜索。

数电研讨用CMOS传输门和CMOS非门设计边沿D触发器

数字电子技术研究性学习报告

用CMOS传输门和CMOS非门设计边沿D触发器

第一章基本器件结构图以及功能

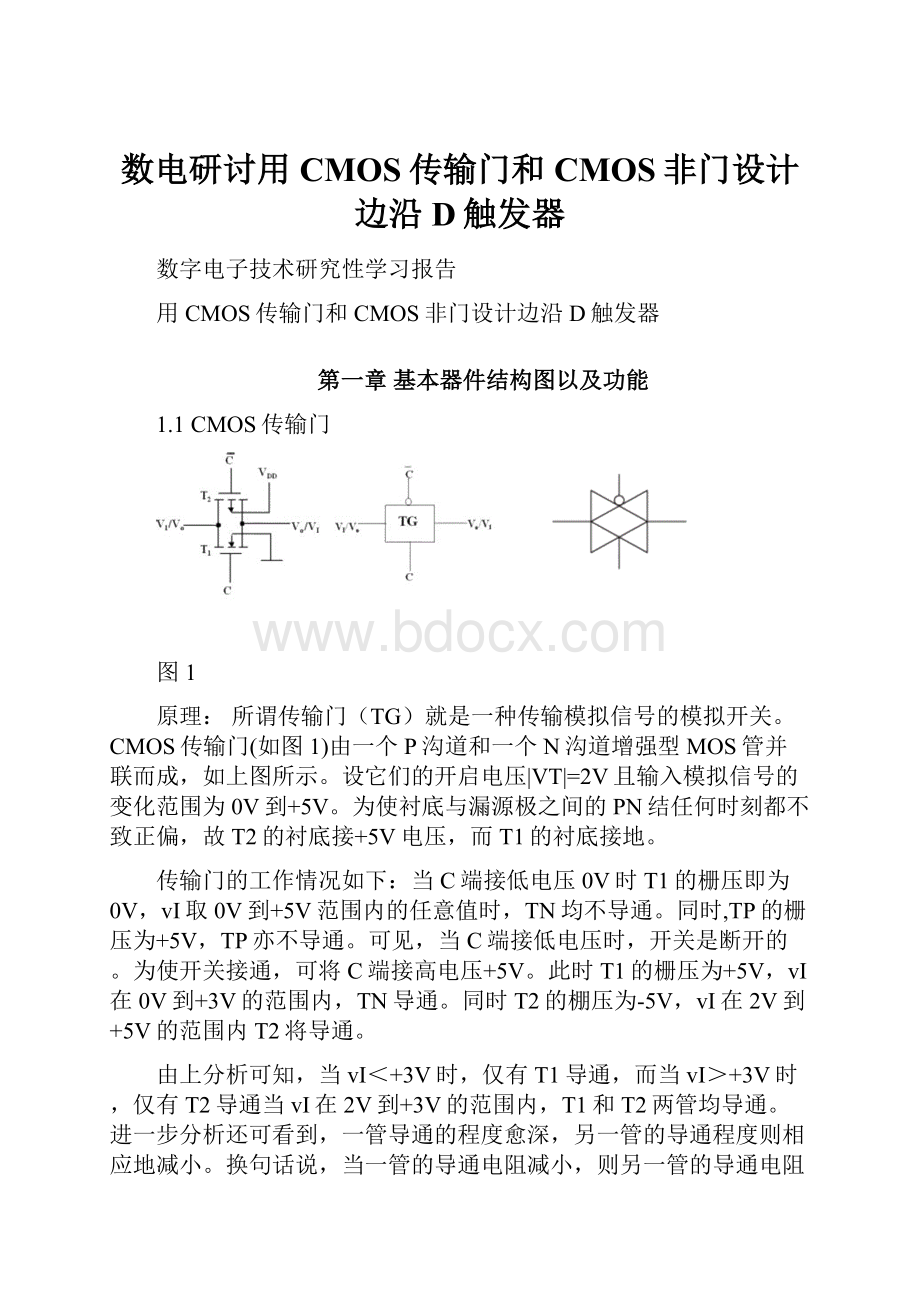

1.1CMOS传输门

图1

原理:

所谓传输门(TG)就是一种传输模拟信号的模拟开关。

CMOS传输门(如图1)由一个P沟道和一个N沟道增强型MOS管并联而成,如上图所示。

设它们的开启电压|VT|=2V且输入模拟信号的变化范围为0V到+5V。

为使衬底与漏源极之间的PN结任何时刻都不致正偏,故T2的衬底接+5V电压,而T1的衬底接地。

传输门的工作情况如下:

当C端接低电压0V时T1的栅压即为0V,vI取0V到+5V范围内的任意值时,TN均不导通。

同时,TP的栅压为+5V,TP亦不导通。

可见,当C端接低电压时,开关是断开的。

为使开关接通,可将C端接高电压+5V。

此时T1的栅压为+5V,vI在0V到+3V的范围内,TN导通。

同时T2的棚压为-5V,vI在2V到+5V的范围内T2将导通。

由上分析可知,当vI<+3V时,仅有T1导通,而当vI>+3V时,仅有T2导通当vI在2V到+3V的范围内,T1和T2两管均导通。

进一步分析还可看到,一管导通的程度愈深,另一管的导通程度则相应地减小。

换句话说,当一管的导通电阻减小,则另一管的导通电阻就增加。

由于两管系并联运行,可近似地认为开关的导通电阻近似为一常数。

这是CMOS传输出门的优点。

1.2CMOS反相器

1.2.1电压传输特性和电流传输特性

CMOS反相器的电压传输特性曲线可分为五个工作区。

(如图2)

图2

工作区Ⅰ:

由于输入管截止,故vO=VDD,处于稳定关态。

工作区Ⅲ:

PMOS和NMOS均处于饱和状态,特性曲线急剧变化,vI值等于阈值电压Vth。

工作区Ⅴ:

负载管截止,输入管处于非饱和状态,所以vO≈0V,处于稳定的开态。

CMOS反相器的电流传输特性曲线如图3,只在工作区Ⅲ时,由于负载管和输入管都处于饱和导通状态,会产生一个较大的电流。

其余情况下,电流都极小。

图3

1.2.2CMOS反相器特点

静态功耗极低。

在稳定时,CMOS反相器工作在工作区Ⅰ和工作区Ⅴ,总有一个MOS管处于截止状态,流过的电流为极小的漏电流。

抗干扰能力较强。

由于其阈值电平近似为0.5VDD,输入信号变化时,过渡变化陡峭,所以低电平噪声容限和高电平噪声容限近似相等,且随电源电压升高,抗干扰能力增强。

电源利用率高。

VOH=VDD,同时由于阈值电压随VDD变化而变化,所以允许VDD有较宽的变化范围,一般为+3~+18V。

输入阻抗高,带负载能力强。

第二章设计方案一

2.1设计思路

最初拿到这个题,感觉有些难度,相比直接由CMOS传输门和S反相器设计出D触发器,我感觉由以上两种器件设计出与非门较简单。

设计出的与非门如图4。

2.2性能评估

1.构成较复杂:

由于一个两输入的与非门就需要8个传输门以及10个非门,若需要三输入的与非门则需要更多的传输门以及与非门,所以电路构成复杂。

图4

2.电路利用率较低:

当一条支路通路时,其他之

路处于闲置状态,所以电路的利用率低。

第三章设计方案二

3.1电路结构图

图5

3.2工作原理

如图5。

当cp低电平时,TG1导通、TG2截止,D信号经过传输门输入,_Q=_D、Q=D,电路输出Q跟随D信号变化。

当cp上升沿时,TG1截止、TG2导通,D信号不能传输,D信号的改变对输出不会产生影响,输出端的两个非门首尾相连,保持上升沿时刻的状态不变。

。

此方案由手动开启和关闭传输门来体现D触发器的特性。

波形如图6。

由图6可知,若CP上升前,即D触发器关闭前,输入D发生突变,输出会有影响。

3.3性能评估

1.元件数量少:

整个电路只需要5个元件,包括两个传输门以及三个非门。

2.传输时间短:

信号经过电路时,只需要通过三个非门和一个传输门即可输出。

传输时间大概为40ns。

3.功耗小:

组成电路的元器件都为CMOS元器件,功耗小。

4.人性化:

可人为手动控制。

若输入了错误信号,则可在时钟上升沿到来前进行改正。

5.抗干扰能力不强:

在时钟上升沿到来之前,传输门一直处于开启状态。

如果在时钟上升沿到来前,信号发生了突变,则导致输出了错误的信号,所以抗干扰能力有待提高。

图6

第四章设计方案三

4.1电路结构图

图7

4.2工作原理

如图7。

当CP的上升沿到达时,TG1截止,TG2导通,切断了D信号的输入,由于G1的输入电容存储效应,G1输入端电压不会立即消失,于是Q、-Q在TG1截止前的状态被保存下来;同时由于TG3导通、TG4截止,主触发器的状态通过TG3和G3送到了输出端,使Q=D(CP上升沿到达时D的状态),而-Q=-D。

在CP高电平期间,Q=D,-Q=-D的状态一直不会改变,直到CP下降沿到达时,TG2、TG3又截止,TG1、TG4又导通,主触发器又开始接收D端新数据,从触发器维持已转换后的状态。

可见,这种触发器的动作特点是输出端的状态转换发生在CP的上升沿,而且触发器所保持的状态仅仅取决于CP上升沿到达时的输入状态。

正因为触发器输出端状态的转换发生在CP的上升沿(即CP的上升沿),所以这是一个CP上升沿触发的边沿触发器,CP上升沿为有效触发沿,或称CP上升沿为有效沿(下降沿为无效沿)。

4.3性能评估

1.传输时间较短:

信号经过电路时,需要通过三个非门和三个传输门即可输出。

传输时间大概为60ns。

2.功耗较小:

组成电路的元器件都为CMOS元器件,功耗小。

3.抗干扰能力强:

传输门只于上升沿到来前后几十纳秒内处于开启状态,其他时间都处于关闭状态,此时信号无法输入。

因此只要保证信号在上升沿到来前后20ns内保持不变即可将信号准确地传输。

所以抗干扰能力强。

4.电子元器件较多,成本略高:

一个触发器需要9个原件,其中包括4个传输门以及5个非门。

所以成本略高。

4.4方案对比

方案二

方案三

元件数量少,成本较低

电路较复杂,成本较高

传输时间短

传输时间较短

功耗小

功耗较小

抗干扰能力不强

抗干扰能力强

可人为手动控制,输入错误后可以改正

表4-1

通过两种方案(表4-1)的对比可以根据其性能以及自身需求对此两种方案进行合理选择。

第五章激励信号D的保持时间和时钟CP的最大频率

5.1分析与结论

假设,信号通过传输门及反相器的时间为t1。

D信号的保持时间需大于3t1,才能保证D信号能够存储下来。

如果CP下降沿后,D信号才被锁存,在此期间如果D信号有突变,将影响输出结果,所以电路需保证D信号存储后CP再变为低电平,也就是说CP高电平的时间需大于3t1,设CP周期为TCP,则推出的解释即为CP需满足0.5TCP大于3t1,即fCP小于1/6t1。

第六章写出特征方程,画出特征表,激励表与状态图

6.1特征方程

6.2特征表(如表5-1)

CP

D

Qn+1

X

X

Qn

0

0

1

1

表5-1特征表

6.3激励表(如表5-2)

Qn

Qn+1

D

0

0

0

0

1

1

1

0

0

1

1

1

表5-2激励表

6.4状态转换图(如图8)

图8

第七章设计拓展

7.1思想启发

本次研究性学习主要是使用CMOS传输门和CMOS反相器设计D触发器。

但为了加深我对电子元器件的理解并充分锻炼我的设计能力,我想到用CMOS传输门和CMOS反相器设计一个抢答器。

7.2功能简述

此电路中有N个输入和N个输出,每个人对应各自的一个输出,每个输出端各连接一个灯。

先按下的人会使其他人的抢答器失效,同时该人的信号输出,灯亮起,表示该人抢答成功。

7.3电路结构

7.3.1由CMOS传输门和CMOS反相器构成的异或门

工作原理:

如图9,此与非门由三个反相器和一个传输门构成。

A=B=0:

TG断开,则C=—B=1,F=—C=0;A=B=1:

TG导通,C=B=1,反相器2的两只MOS管都截止,输出F=0;A=1,B=0:

TG导通,F=1;A=0,B=1:

TG断开,F=1。

图9

7.3.2抢答器结构图如图10

图10

7.3.3工作原理

如图11,当A先闭合开关时,高电平通过传输门A1输出,LED1亮起。

图11

如图12,与此同时使异或门U6的两个输入都为1,异或门U6输出0,使得传输门A2关闭,B的信号无法传递到输出灯LED2。

反之亦然。

图12

7.4电路的改进

7.4.1改进的原因

由原电路可知,如果有N个输入则有N个输出,每个输出都回对应一个灯,这样一来,如果输入很多,则需要更多的灯,导致成本变高,而且电路多变,不利于集成量产。

而如果最后由数码管显示出数字,则可降低成本。

改进后的电路图如图13。

图13

第八章将设计的D触发器转换成JK触发器和T触发器

8.1D触发器转换成JK触发器(如图14)

D触发器的状态方程是:

Qn+1=D;

jk触发器的状态方程是:

Qn+1=J—Qn+—KQn。

让两式相等

可得:

D=J—Qn+—KQn。

用门电路实现上述函数即可转换成为JK触发器

图14

8.2D触发器转成T触发器(如图15)

图15

第九章收获与感想

本次数电研究性学习,大大加深了我对触发器的理解,也充分地锻炼了我的设计能力,我感到这次研讨对我有意义深远的作用,因此我做出了如下总结。

1.通过本次研究性学习,让我明白对于一个课题来说,什么叫研究,通过什么研究,怎样研究。

不仅要表达出原理,画出电路图,进行仿真,而且还要讨论其性能。

除此以外,还要和其他方案进行横向比较,在不同需求下选择不同方案。

2.认识到理论知识与实际相结合的重要性。

在课本上学习内容远远不够,当我亲手去设计一些东西的时候才感觉到理论与实践的差异。

这让我明白只有把理论与实践相结合才能学好这门课。

3.熟练了对于MULTISM软件的使用。

刚刚使用这个软件时,大部分元件需要上网查找资料才能在软件中找到。

本次研究性学习需要多次使用此软件进行操作。

我从磕磕绊绊地查找元器件到在短时间内就能够制作出完整的电路。

这对于我来说是一个飞跃。

4.注重哲学思想(从局部到整体,再从整体到局部,辨证思想)的运用。

哲学是知识中的知识,首先应用局部到整体的思想,分析构成D触发器的门电路:

传输门和与非门,再从整体到局部分析其性能。

紧接着用辩证的思想对74HC74和74LS74进行分析,分析其优缺点。

坦白地说,由于这学期学生工作比较繁重,我对于本学科学的并不是很透彻,所以最初做出来的报告不太详尽,自己的东西也比较少,再加上格式的问题,给老师看了几分钟就被打了回来,我深表惭愧。

但我没有灰心,而是回去认真阅读课本,加深了解后进行设计,不仅如此,我还通过自己的反复琢磨进行了拓展,设计出了由CMOS传输门和CMOS反相器构成的抢答器,希望没有辜负老师的期望,也对得起这个优秀的专业,以及作为一名交大学子的本分。

可以说,如果没有老师的高标准严要求,我无法做出这样完整的报告,也不可能对本学科进行如此深入地研究。

我也深知,老师的批评意味着对我还有希望,所以我更要尽力去证明自己。

最后我想感谢老师的耐心教导,让我懂得认真能把事情多对,用心能把事情做好。