DSP输入输出课件.docx

《DSP输入输出课件.docx》由会员分享,可在线阅读,更多相关《DSP输入输出课件.docx(49页珍藏版)》请在冰豆网上搜索。

DSP输入输出课件

1.系统控制和状态寄存器1(SCSR1)—地址7018H

位15保留位

位14CLKSRC。

CLKOUT引脚源选择位

0CLKOUT引脚输出CPU时钟

1CLKOUT引脚输出WDCLK时钟

位13—12LPM(1:

0)。

低功耗模式选择位,这两位声明了CPU在执行IDLE指令时进入哪一种低功耗方式。

01CPU进入IDLE1(LPM0)

02CPU进入IDLE2(LPM1)

1xCPU进入HALT(LPM2)

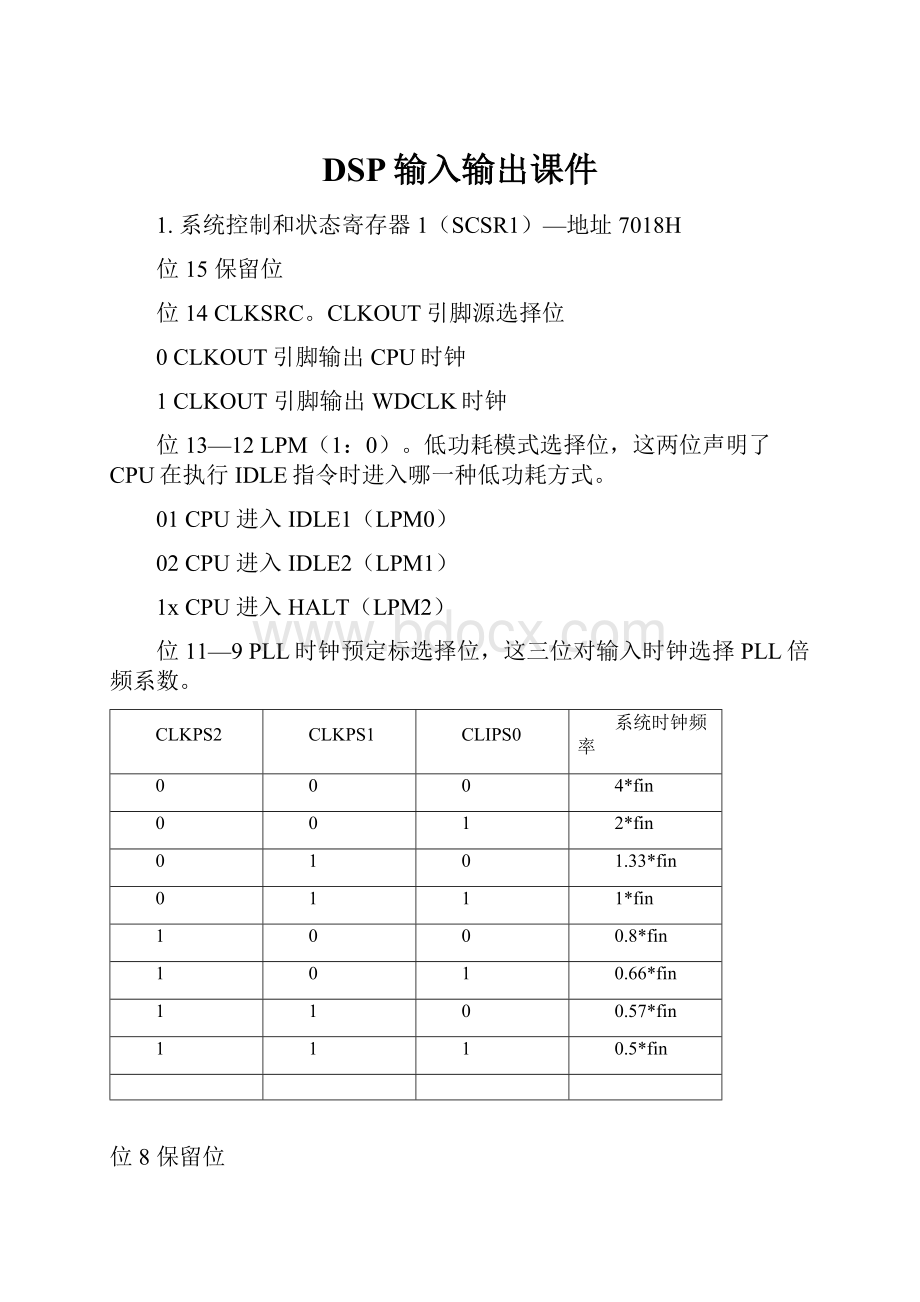

位11—9PLL时钟预定标选择位,这三位对输入时钟选择PLL倍频系数。

CLKPS2

CLKPS1

CLIPS0

系统时钟频率

0

0

0

4*fin

0

0

1

2*fin

0

1

0

1.33*fin

0

1

1

1*fin

1

0

0

0.8*fin

1

0

1

0.66*fin

1

1

0

0.57*fin

1

1

1

0.5*fin

位8保留位

位7ADCCLKEN。

ADC模块时钟使能控制位。

0禁止ADC模块的时钟(即:

关断ADC模块以节约能量)

1使能ADC模块的时钟,且正常运行

位6SCICLKEN。

SCI模块时钟使能控制位。

0禁止SCI模块的时钟(即:

关断SCI模块以节约能量)

1使能SCI模块的时钟,且正常运行

位5SPICLKEN。

SPI模块时钟使能控制位。

0禁止SPI模块的时钟(即:

关断SPI模块以节约能量)

1使能SPI模块的时钟,且正常运行

位4CANCLKEN。

CAN模块时钟使能控制位。

0禁止CAN模块的时钟(即:

关断CAN模块以节约能量)

1使能CAN模块的时钟,且正常运行

位3EVBCLKEN。

EVB模块时钟使能控制位。

0禁止EVB模块的时钟(即:

关断EVB模块以节约能量)

1使能EVB模块的时钟,且正常运行

位2EVACLKEN。

EVA模块时钟使能控制位。

0禁止EVA模块的时钟(即:

关断EVA模块以节约能量)

1使能EVA模块的时钟,且正常运行

位1保留位

位0ILLADR位。

无效地址检测位。

2中断标志寄存器(IFR)

位15~6保留位。

这些位读出时始终为0。

位5INT6flag中断6标志位。

该位用作连至第6级中断INT6的所有中断标志。

0无INT6级的中断挂起

1至少一个INT6级的中断挂起,向该位写1可将该位清除为0,即清除中断请求。

位4INT5FLAG中断5标志位。

位该用作连至第5级中断INT5的所有中断标志。

0无INT5级的中断挂起

1至少一个INT5级的中断挂起,向该位写1可将该位清除为0,即清除中断请求。

位3INT4FLAG中断4标志位。

该位用作连至第4级中断INT4的所有中断标志。

0无INT4级的中断挂起

1至少一个INT4级的中断挂起,向该位写1可将该位清除为0,即清除中断请求。

位2INT3FLAG中断3标志位。

该位用作连至第3级中断INT3的所有中断标志。

0无INT3级的中断挂起

1至少一个INT3级的中断挂起,向该位写1可将该位清除为0,即清除中断请求。

位1INT2FLAG中断2标志位。

该位用作连至第2级中断INT2的所有中断标志。

0无INT2级的中断挂起

1至少一个INT2级的中断挂起,向该位写1可将该位清除为0,即清除中断请求。

位0INT1FLAG中断1标志位。

该位用作连至第1级中断INT1的所有中断标志。

0无INT1级的中断挂起

1至少一个INT1级的中断挂起,向该位写1可将该位清除为0,即清除中断请求。

3中断屏蔽寄存器(IMR)

位15~6保留位。

这些位读出时始终为0。

位5INT6mask中断6的屏蔽位。

0中断INT6级被屏蔽

1中断INT6级被使能

位4INT5mask中断5的屏蔽位。

。

0中断INT5级被屏蔽

1中断INT5级被使能

位3INT4mask中断4的屏蔽位。

0中断INT4级被屏蔽

1中断INT4级被使能

位2INT3mask中断3的屏蔽位。

0中断INT3级被屏蔽

1中断INT3级被使能

位1INT2mask中断2的屏蔽位。

0中断INT2级被屏蔽

1中断INT2级被使能

位0INT1mask中断1的屏蔽位。

0中断INT1级被屏蔽

1中断INT1级被使能

4.清除控制位指令CLRC

C状态寄存器ST1的进位位

CNF存器ST1的RAM配置控制位

INTM存器ST1的中断方式位

OVM寄存器ST1的溢出方式位

SXM状态寄存器ST1的符号扩展位

TC状态寄存器ST1的测试/控制标志位

XF状态寄存器ST1的XF引脚状态位

5I/O复用控制寄存器

5.1I/O口复用控制寄存器A(MCRA)

MCRA.15

MCRA.14

MCRA.13

MCRA.12

MCRA.11

MCRA.10

MCRA.9

MCRA.8

MCRA.7

MCRA.6

MCRA.5

MCRA.4

MCRA.3

MCRA.2

MCRA.1

MCRA.0

表I/O复用控制寄存器A(MCRA)配置

位

位的名称

功能选择

基本功能(MCRA.n=1)

一般I/O口

(MCRA.n=0)

0

MCRA.0

SCITXD

IOPA0

1

MCRA.1

SCIRXD

IOPA1

2

MCRA.2

XINT1

IOPA2

3

MCRA.3

CAP1/QEP1

IOPA3

4

MCRA.4

CAP2/QEP2

IOPA4

5

MCRA.5

CAP3

IOPA5

6

MCRA.6

PWM1

IOPA6

7

MCRA.7

PWM2

IOPA7

8

MCRA.8

PWM3

IOPB0

9

MCRA.9

PWM4

IOPB1

10

MCRA.10

PWM5

IOPB2

11

MCRA.11

PWM6

IOPB3

12

MCRA.12

T1PWM/T1CMP

IOPB4

13

MCRA.13

T2PWM/T2CMP

IOPB5

14

MCRA.14

TDIRA

IOPB6

15

MCRA.15

TCLKINA

IOPB7

5.2I/O口复用控制寄存器B(MCRB)

MCRB.15

MCRB.14

MCRB.13

MCRB.12

MCRB.11

MCRB.10

MCRB.9

MCRB.8

MCRB.7

MCRB.6

MCRB.5

MCRB.4

MCRB.3

MCRB.2

MCRB.0

MCRB.0

表I/O复用控制寄存器B(MCRB)配置

位

位的名称

功能选择

基本功能(MCRB.n=1)

一般I/O口

(MCRB.n=0)

0

MCRB.0

W/R

IOPC0

1

MCRB.1

BIO

IOPC1

2

MCRB.2

SPISIMO

IOPC2

3

MCRB.3

SPISOMI

IOPC3

4

MCRB.4

SPICLK

IOPC4

5

MCRB.5

SPISTE

IOPC5

6

MCRB.6

CANTX

IOPC6

7

MCRB.7

CANRX

IOPC7

8

MCRB.8

XINT2/ADCSOC

IOPD0

9

MCRB.9

EMU0

保留位

10

MCRB.10

EMU1

保留位

11

MCRB.11

TCK

保留位

12

MCRB.12

TDI

保留位

13

MCRB.13

TDO

保留位

14

MCRB.14

TMS

保留位

15

MCRB.15

TMS2

保留位

5.3I/O口复用控制寄存器C(MCRC)

MCRC.15

MCRC.14

MCRC.13

MCRC.12

MCRC.11

MCRC.10

MCRC.9

MCRC.8

MCRC.7

MCRC.6

MCRC.5

MCRC.4

MCRC.3

MCRC.2

MCRC.1

MCRC.0

表I/O复用控制寄存器C(MCRC)配置

位

位的名称

功能选择

基本功能(MCRC.n=1)

一般I/O口

(MCRC.n=0)

0

MCRC.0

CLKOUT

IOPE0

1

MCRC.1

PWM7

IOPE1

2

MCRC.2

PWM8

IOPE2

3

MCRC.3

PWM9

IOPE3

4

MCRC.4

PWM10

IOPE4

5

MCRC.5

PWM11

IOPE5

6

MCRC.6

PWM12

IOPE6

7

MCRC.7

CAP4/QEP3

IOPE7

8

MCRC.8

CAP5/QEP4

IOPF0

9

MCRC.9

CAP6

IOPF1

10

MCRC.10

T3PWM/T3CMP

IOPF2

11

MCRC.11

T4PWM/T4CMP

IOPF3

12

MCRC.12

TDIRB

IOPF4

13

MCRC.13

TCLKINB

IOPF5

14

MCRC.14

IOPF6

IOPF6

15

MCRC.15

保留位

保留位

6.I/O口数据和方向寄存器

6.1端口A数据和方向控制寄存器A(PADATDIR)——地址7098H

A7DIR

A6DIR

A5DIR

A4DIR

A3DIR

A2DIR

A1DIR

A0DIR

RW_0RW_0RW_0RW_0RW_0RW_0RW_0RW_0

IOPA7

IOPA6

IOPA5

IOPA4

IOPA3

IOPA2

IOPA1

IOPA0

RW_+RW_+RW_+RW_+RW_+RW_+RW_+RW_+

注:

_+复位后的值和相应的引脚的状态有关,R=可读,W=可写,_0=复位后的值

位15~8AnDIR

1配置相应的引脚为输入方式

2配置相应的引脚为输出方式

位7~0IOPAn

如果AnDIR=0,即引脚为输入方式

0读相应的引脚为低电平

1读相应的引脚为高电平

如果AnDIR=1,即引脚为输出方式

1置相应的引脚使其输出为低电平

2设置相应的引脚使其输出为高电平

6.2端口B数据和方向控制寄存器B(PBDATDIR)——地址709AH

B7DIR

B6DIR

B5DIR

B4DIR

B3DIR

B2DIR

B1DIR

B0DIR

RW_0RW_0RW_0RW_0RW_0RW_0RW_0RW_0

IOPB7

IOPB6

IOPB5

IOPB4

IOPB3

IOPB2

IOPB1

IOPB0

RW_+RW_+RW_+RW_+RW_+RW_+RW_+RW_+

注:

_+复位后的值和相应的引脚的状态有关,R=可读,W=可写,_0=复位后的值

位15~8BnDIR

1配置相应的引脚为输入方式

2配置相应的引脚为输出方式

位7~0IOPBn

如果BnDIR=0,即引脚为输入方式

0读相应的引脚为低电平

1读相应的引脚为高电平

如果BnDIR=1,即引脚为输出方式

1置相应的引脚使其输出为低电平

2设置相应的引脚使其输出为高电平

6.3端口C数据和方向控制寄存器C(PCDATDIR)——地址709CH

C7DIR

C6DIR

C5DIR

C4DIR

C3DIR

C2DIR

C1DIR

C0DIR

RW_0RW_0RW_0RW_0RW_0RW_0RW_0RW_0

IOPC7

IOPC6

IOPAC5

IOPC4

IOPC3

IOPC2

IOPC1

IOPC0

RW_+RW_+RW_+RW_+RW_+RW_+RW_+RW_X

注:

_+复位后的值和相应的引脚的状态有关,R=可读,W=可写,_0=复位后的值,_X未定义

位15~8CnDIR

1配置相应的引脚为输入方式

2配置相应的引脚为输出方式

位7~0IOPCn

如果CnDIR=0,即引脚为输入方式

0读相应的引脚为低电平

1读相应的引脚为高电平

如果CnDIR=1,即引脚为输出方式

1置相应的引脚使其输出为低电平

2设置相应的引脚使其输出为高电平

6.4端口D数据和方向控制寄存器D(PDDATDIR)——地址709EH

保留位

D0DIR

RW_0

保留位

IOPD0

RW_+

6.5端口E数据和方向控制寄存器E(PEDATDIR)——地址7094H

E7DIR

BE6DIR

E5DIR

E4DIR

E3DIR

E2DIR

E1DIR

E0DIR

RW_0RW_0RW_0RW_0RW_0RW_0RW_0RW_0

IOPE7

IOPE6

IOPE5

IOPE4

IOPE3

IOPE2

IOPE1

IOPE0

RW_+RW_+RW_+RW_+RW_+RW_+RW_+RW_X

注:

_+复位后的值和相应的引脚的状态有关,R=可读,W=可写,_0=复位后的值,X未定义

6.6端口F数据和方向控制寄存器F(PFDATDIR)——地址7096H

E7DIR

E6DIR

E5DIR

E4DIR

E3DIR

E2DIR

E1DIR

E0DIR

RW_0RW_0RW_0RW_0RW_0RW_0RW_0RW_0

IOPE7

IOPE6

IOPE5

IOPE4

IOPE3

IOPE2

IOPE1

IOPE0

RW_+RW_+RW_+RW_+RW_+RW_+RW_+RW_X

注:

_+复位后的值和相应的引脚的状态有关,R=可读,W=可写,_0=复位后的值,X未定义

DSP外设存储器映射图

Memory-MappedRegistersandReserved

On-chipDARAMB2

Illegal

Reserved

On-chipDARAMB0

On-chipDARAMB1

Reserved

Illegal

SARAM(2K)

Illegal

PeripheralFrame1(PF1)

PeripheralFrame2(PF2)

Illegal

PeripheralFrame3(PF3)

Illegal

External

Reserved

Interrupt-maskRegister

Reserved

InterruptFlagRegister

EmulationRegistersandReserved

Illegal

SystemConfigurationandControlRegisters

WatchdogTimerRegisters

lllegal

SPI

SCI

Illegal

External-InterruptRegisters

Illegal

DigitalI/OControlRegisters

ADCcontrolregisters

Illegal

CANcontrolregisters

Illegal

CANMailbox

Illegal

General-purposeTimerRegisters

Compare,PWMandDeadbandRegisters

CaptureandQEPRegisters

InterruptMask,VectorandFlagRegisters

Illegal

General-purposeTimerRegisters

Compare,PWM,andDeadbandRegisters

CaptureandQEPRegisters

InterruptMask,VectorandFlagRegisters

Illegal

ADC控制寄存器1(ADCTRL1)

保留位

RESET

SOFT

FREE

ACQPS3

ACQPS2

ACQPS1

ACQPS0

RW_0RW_0RW_0RW_0RW_0RW_0RW_0RW_0

CPS

CONTRUN

INTPR1

SEQCASC

CALENA

BRGENA

HI/LO

STESTENA

RW_0RW_0RW_0RW_0RW_0RW_0RW_0RW_0

位15保留位

位14复位位。

ADC模块软件复位位。

这一位对ADC模块的主动复位,所有的寄存器和排序器指针都复位到器件上电时的初始状态

0无影响

1复位整个ADC模拟

位13~12SOFT位和FREE位。

这两位决定仿真悬挂时ADC模块的工作情况。

在自由运行模式下。

ADC模块的运行不受仿真影响,在停止模式下,仿真悬挂时,ADC模块可立即停止或者完成当前操作之后停止。

SOFTFREE

00一旦仿真悬挂,ADC模块立即停止

10仿真悬挂时,ADC模块完成当前转换后停止

X1自由运行,继续运行而不管仿真悬挂

11~8位采样时间选择位ACQPS3—ACQPS0。

这几位决定了ADC时钟的预定标系数。

见表8.7。

CPU时钟为30MHZ时ADC模块的预定标系数

#

ACQPS3

ACQPS2

ACQPS1

ACQPS0

预定标因子(除以)

采样窗口时间

信号源阻抗(CPS=0)

信号源阻抗(CPS=1)

0

0

0

0

0

1

2*TCLK

67

385

1

0

0

0

1

2

4*TCLK

385

1020

2

0

0

1

0

3

6*TCLK

702

1655

3

0

0

1

1

4

8*TCLK

1020

2290

4

0

1

0

0

5

10*TCLK

1337

2925

5

0

1

0

1

6

12*TCLK

1655

3560

6

0

1

1

0

7

14*TCLK

1972

4194

7

0

1

1

1

8

16*TCLK

2290

4829

8

1

0

0

0

9

18*TCLK

9

1

0

0

1

10

20*TCLK

10

1

0

1

0

11

22*TCLK

11

1

0

1

1

12

24*TCLK

12

1

1

0

0

13

26*TCLK

13

1

1

0

1

14

28*TCLK

14

1

1

1

0

15

30*TCLK

15

1

1

1

1

16

32*TCLK

1)TCLK的周期取决于“转换时钟预定标因子”位(BIT7),例如:

2)CPS=0:

TCLK=1/CLK(例对于CLK=40MHZ,TCLK=25ns)

3)CPS=0:

TCLK=1/CLK/2对于CLK=40MHZ,TCLK=50ns)

位7CPS位。

转换时钟预定标位。

这一位决定了ADC转换逻辑时钟的预定标

0FCLK=CLK/1

1FCLK=CLK/2

其中CLK为CPU时钟频率。

位6连续转换位CONTRUN。

这一位决定排序器工作在连续转换模式或者启动/停止模式。

用户可以在当前转换序列正被执行时向这一位写数,但是只有在当前转换序列完成之后才生效,在连续模式下,用户不用对排序器复位,而在启动/停止模式下,排序器必须被复位以使排序器指针指到CONV00。

1启动/停止模式

2连续转换模式。

位5ADC中断请求优先级位INTPRI。

0高优先级

1低优先级

位4级连排序器工作方式位SEQACSC。

0双排序器工作模式。

SEQ1和SEQ2作为两个最多可选择8个转换通道的排序器

1级连模式。

SEQ1和SEQ2级连起来作为一个最多可选择16个转换通道的排序器SEQ

位3偏差校准使能位CALENA

0禁止校准模式

1使能校准模式

位2桥使能位BRGENA。

见表8.8。

BRGENA

HI/LO

CALENA=1

(参考电压(V)

STESTENA=1

(参考电压(V)

0-

0

VREFLO

VREFLO

0

1

VREFHI

VREFHI

1

0

|(VREFHI-VREFLO)/2|

VREFLO

1

1

|(VREFLO-VREFHI)/2|

VREFHI

0满的参考电压被接到ADC输入

1参考的中点电压被接到ADC输入

位1VREFHI和VREFLO选择位HI/LO,见表8.8。

0用VREFLO作为ADC输入的值

1用VREFHI作为ADC输入的值

位0自测试使能位STESTENA

1禁止自测试模式

2使能自测试模式

ADC控制寄存器2(ADCTRL2)

EVBSOCSEQ

RSTSEQ1/STRTCAL

SOCSEQ1

SEQ1BSY

INTENASEQ1(Mode1)

INTENASEQ1(Mode0)

INTFLAGSEQ1

EVASOCSEQ1

EXTSOC

SEQ1

RSTSEQ2

SOCSEQ2

SEQ2

BSY

INTENASEQ2{Mode1}

INTENASEQ2(Mode0)

INTFLAGSEQ2

EVB

SOCSEQ2

位15EVBSOCSEQ。

EVB的SOC信号为级连排序器使能位。

0不起作用

1允许级连的排序器SEQ被事件管理器B的信号启动

位14RSTSEQ1/STRTCAL。

复位排序器1/启动校准转换方式位。

在校准转换方式被禁止的情况下:

0不起作用

1启动校准转换方式