数字逻辑第5章习题参考解答.docx

《数字逻辑第5章习题参考解答.docx》由会员分享,可在线阅读,更多相关《数字逻辑第5章习题参考解答.docx(20页珍藏版)》请在冰豆网上搜索。

数字逻辑第5章习题参考解答

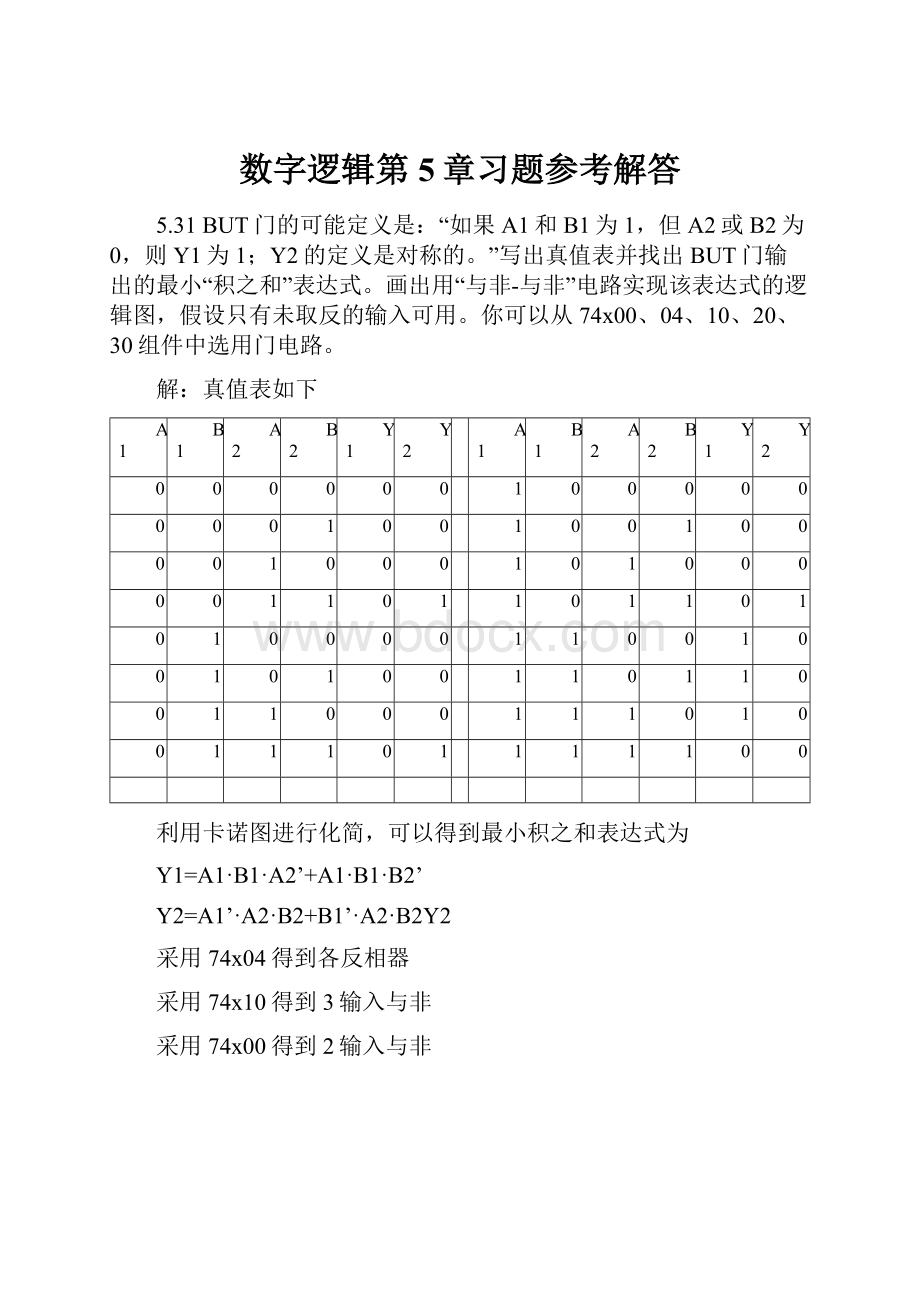

5.31BUT门的可能定义是:

“如果A1和B1为1,但A2或B2为0,则Y1为1;Y2的定义是对称的。

”写出真值表并找出BUT门输出的最小“积之和”表达式。

画出用“与非-与非”电路实现该表达式的逻辑图,假设只有未取反的输入可用。

你可以从74x00、04、10、20、30组件中选用门电路。

解:

真值表如下

A1

B1

A2

B2

Y1

Y2

A1

B1

A2

B2

Y1

Y2

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

1

0

0

1

0

0

1

0

0

0

0

1

0

0

0

1

0

1

0

0

0

0

0

1

1

0

1

1

0

1

1

0

1

0

1

0

0

0

0

1

1

0

0

1

0

0

1

0

1

0

0

1

1

0

1

1

0

0

1

1

0

0

0

1

1

1

0

1

0

0

1

1

1

0

1

1

1

1

1

0

0

利用卡诺图进行化简,可以得到最小积之和表达式为

Y1=A1·B1·A2’+A1·B1·B2’

Y2=A1’·A2·B2+B1’·A2·B2Y2

采用74x04得到各反相器

采用74x10得到3输入与非

采用74x00得到2输入与非

定义的BUT门的门级设计,要求以cmos实现时使用的晶体管数目最少,可以从74x00、04、10、20、30组件中选用门电路.写出输出表达式(不一定是二级“积之和”)并画出逻辑图。

解:

cmos晶体管用量:

反相器2个2输入与非门4个3输入与非门6个

为了尽量减少晶体管用量,可以采用下列表达式,以便实现器件的重复使用:

F1=(A1·B1)·(A2’+B2’)=(A1·B1)·(A2·B2)’=[(A1·B1)’+(A2·B2)’’]’

F2=[(A2·B2)’+(A1·B1)’’]’

电路图:

晶体管用量:

20只(原设计中晶体管用量为40只)

BUT门和单个二输入或门实现F.

解:

BUT门输出采用最小项和的形式表达为

,

将两个输出相或就可以得到要求实现的函数。

5.19指出用一块或多块74x138或74x139二进制译码器以及与非门,如何构建下面每个单输出或多输出的逻辑功能(提示:

每个实现等效于一个最小项之和)。

解:

a)

b)

c)

假设要求设计一种新的组件:

优化的十进制译码器,它只有十进制输入组合。

与取消6个输出的4-16译码器相比,怎样使这样的译码器价格降至最低?

写出价格最低译码器的全部10个输出的逻辑等式。

假设输入和输出高电平有效且没有使能输入。

解:

取消6个输出所对应的与非门,将6个输入组合作为无关项以化简其余输出的乘积项:

设输入为:

a,b,c,d

ab

cd

×

×

×

×

×

×

Y0=a’·b’·c’·d’Y1=a’·b’·c’·dY2=b’·c·d’Y3=b’·c·dY4=b·c’·d’

Y5=b·c’·dY6=b·c·d’Y7=b·c·dY8=a·c’·d’Y9=a·d

设计10-4编码器,输入用10中取1码,输出用BCD码。

解:

简化真值表为:

Y3

Y2

Y1

Y0

Y3

Y2

Y1

Y0

0

0

0

0

0

5

0

1

0

1

1

0

0

0

1

6

0

1

1

0

2

0

0

1

0

7

0

1

1

1

3

0

0

1

1

8

1

0

0

0

4

0

1

1

1

9

1

0

0

1

可得:

Y3=I9+I8

Y2=I7+I6+I5+I4

Y1=I7+I6+I3+I2

Y0=I9+I7+I5+I3+I1

5.46只用4个8输入与非门画出16-4编码器的逻辑图。

在你的设计中,输入和输出的有效电平是什么?

解:

Y3=I15+I14+I13+I12+I11+I10+I9+I8

Y2=I15+I14+I13+I12+I7+I6+I5+I4

Y1=I15+I14+I11+I10+I7+I6+I3+I2

Y0=I15+I13+I11+I9+I7+I5+I3+I1

输入和输出都采用高电平有效。

如果希望提高电路效率,可以采用输入低电平有效,设计函数如下:

Y3=(I15·I14·I13·I12·I11·I10·I9·I8)’

Y2=(I15·I14·I13·I12·I7·I6·I5·I4)’

Y1=(I15·I14·I11·I10·I7·I6·I3·I2)’

Y0=(I15·I13·I11·I9·I7·I5·I3·I1)’

图X5-21电路有什么可怕的错误?

提出消除这个错误的方法。

解:

该电路中两个2-4译码器同时使能,会导致2个3态门同时导通,导致逻辑电平冲突。

为解决这一问题,可将使能端分开,进行反相连接,各自使能,电路连接如下:

(图略)

或采用多路复用器74X151实现该电路。

LS组件的信息,确定在图5-66所示的32-1多路复用电路中,从任何输入到任何输出的最大传播延迟。

你可以使用“最坏情况”分析方法。

解:

图5-66所用器件及最大延迟为:

74X13938ns

74X15130ns(使能→Y’)

14X2015ns

最长路径应为:

从74X139选择端到74X139输出,再进入74X151使能端到74X151Y’端,再通过74X20。

总延迟为83ns。

IC封装的3输入,5位多路复用器,写出真值表并画出逻辑图和逻辑符号。

解:

设数据输入A(4..0),B(4..0),C(4..0),数据输出Y(4..0)选择端S1,S0

则Y=S1·S0·A+S1·S0’·B+S1’·S0·C

真值表:

S1

S0

Y

0

0

X

0

1

C

1

0

B

1

1

A

逻辑图:

逻辑符号:

X5-55所示CMOS电路实现的逻辑功能,写出真值表并画出逻辑图(电路包含3.7.1节介绍的传输门)。

解:

S

A

B

Z

S

A

B

Z

0

0

0

0

1

0

0

0

0

0

1

0

1

0

1

1

0

1

0

1

1

1

0

0

0

1

1

1

1

1

1

1

Z=AS’Z=SB

Z=AS’+BS为2选1多路器

逻辑图为:

补充习题:

1设计每次处理2位的相等比较器迭代单元,该单元有1个输出Y和5个输入C,A1,A0,B1,B0;当A与B不相等时输出为1,相等时输出与C相同;写出输出函数的最小积之和表达式。

解:

Y=A1B1’+A1’B1+A0B0’+A0’B0+C

2设计每次处理2位的加法器迭代单元,该单元有3个输出S1,S0,CO,5个输入CI,A1,A0,B1,B0;S为相加的本位和,CO为向高位的进位,CI为来自低位的进位;写出各输出函数的最小积之和表达式。

解:

根据二进制运算规则,可写出卡诺图如下:

A1A0CI=0CI=1

B1B000011110

00

01

11

10

分解化简:

S0

A1A0

CI=0CI=1

B1B0

S0=A0·B0’·CI’+A0’·B0·CI’+A0·B0·CI+A0’·B0’·CI

分解化简S1:

A1A0

CI=0CI=1

B1B0

S1=A1’A0’B1CI’+A1’B1B0’CI’+A1B1’B0’CI’+A1A0’B1’CI’+A1’B1’B0CI+

+A1’A0B1’CI+A1A0B1CI+A1B1B0CI+A1’A0B1’B0+A1A0B1B0+A1’A0’B1B0’+

A1A0’B1’B0’

分解化简CO:

A1A0

CI=0CI=1

B1B0

CO=A1B1+A0B1C1+A1B0C1+A1A0C1+B1B0C1+A0B1B0+A1A0B0

3利用74x138和与非门设计全加器;写出各输出函数的最小项和表达式,画出电路连接图。

解:

设输入变量为X,Y,CIN,输出为S,COUT

则S=X·Y’·CIN’+X’·Y·CIN’+X’·Y’·CIN+X·Y·CIN=

COUT=X·Y+X·CIN+Y·CIN=

第6章习题参考解答

6-3画出74x27三输入或非门的德摩根等效符号。

解:

图形如下

74AHCT00替换74LS00,利用表6-2的信息,确定从输入端到输出端的最大时间延迟。

解:

该图中从输入到输出需要经过6个NAND2;

每个NAND2(74AHCT00)的最大时间延迟为9ns;

所以从输入端到输出端的最大时间延迟为:

54ns。

6-31BUT门的可能定义是:

“如果A1和B1为1,但A2或B2为0,则Y1为1;Y2的定义是对称的。

”写出真值表并找出BUT门输出的最小“积之和”表达式。

画出用反相门电路实现该表达式的逻辑图,假设只有未取反的输入可用。

你可以从74x00、04、10、20、30组件中选用门电路。

解:

真值表如下

A1

B1

A2

B2

Y1

Y2

A1

B1

A2

B2

Y1

Y2

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

1

0

0

1

0

0

1

0

0

0

0

1

0

0

0

1

0

1

0

0

0

0

0

1

1

0

1

1

0

1

1

0

1

0

1

0

0

0

0

1

1

0

0

1

0

0

1

0

1

0

0

1

1

0

1

1

0

0

1

1

0

0

0

1

1

1

0

1

0

0

1

1

1

0

1

1

1

1

1

0

0

利用卡诺图进行化简,可以得到最小积之和表达式为

Y1=A1·B1·A2’+A1·B1·B2’

Y2=A1’·A2·B2+B1’·A2·B2Y2

采用74x04得到各反相器

采用74x10得到3输入与非

采用74x00得到2输入与非

实现的逻辑图如下:

6-32做出练习题6-31定义的BUT门的CMOS门级设计,可以采用各种反相门逻辑的组合(不一定是二级“积之和”),要求使用的晶体管数目最少,写出输出表达式并画出逻辑图。

解:

CMOS反相门的晶体管用量为基本单元输入端数量的2倍;

对6-31的函数式进行变换:

利用圈-圈逻辑设计,可以得到下列结构:

此结构晶体管用量为20只(原设计中晶体管用量为40只)

6-20采用一片74x138或74x139二进制译码器和NAND门,实现下列单输出或多数出逻辑函数。

解:

a)

b)

c)

d)

e)EMBEDEquation.3

f)

6-38假设要求设计一种新的组件:

优化的十进制译码器,它只有十进制输入组合。

与取消6个输出的4-16译码器相比,怎样使这样的译码器价格降至最低?

写出价格最低译码器的全部10个输出的逻辑等式。

假设输入和输出高电平有效且没有使能输入。

解:

设输入为:

A,B,C,D,将6个输入组合作为无关项以化简其余输出的乘积项,输出函数卡诺图如下:

利用无关项进行最小成本设计,可以得到下列输出函数:

与4-16译码器的前10个输出的实现相比,减少了10个与门输入端,减少了20只晶体管的用量。

6-43采用一片SSI器件(4xNand2)和一片74x138,实现下列4个逻辑函数。

解:

电路有什么可怕的错误?

提出消除这个错误的方法。

解:

该电路中74x139两个2-4译码器同时使能,会导致2个3态门同时导通,导致输出逻辑电平冲突。

为解决这一问题,可将使能端分开,进行反相连接,各自使能,即可消除该错误。

6-63设计适合于24引脚IC封装的3输入,5位多路复用器,写出真值表并画出逻辑图和逻辑符号。

解:

设数据输入A(4..0),B(4..0),C(4..0),数据输出Y(4..0)选择端S1,S0

则Y=S1·S0·A+S1·S0’·B+S1’·S0·C

真值表:

S1

S0

Y

0

0

d

0

1

C

1

0

B

1

1

A

其中Y,A,B,C均为5位总线,S1,S2为单线,加上电源和接地,可以采用24引脚IC封装。

逻辑图和逻辑符号如下:

6-68对于图X所示CMOS电路实现的逻辑功能,写出真值表并画出逻辑图(电路包含3.7.1节介绍的传输门)。

解:

S

A

B

Z

S

A

B

Z

0

0

0

0

1

0

0

0

0

0

1

0

1

0

1

1

0

1

0

1

1

1

0

0

0

1

1

1

1

1

1

1

Z=AS’Z=SB

Z=AS’+BS为2选1多路器

逻辑图为:

6-24采用奇数块XNOR门,用图6-70(a)的形式构成某种校验电路,该电路实现什么功能?

解:

XNOR为XOR增加一个反相圈构成;对于偶数块的连接,利用圈到圈设计可以看到,功能与XOR的连接相同(如下图所示);

所以,对于奇数块连接时,输出与对应XOR连接电路正好相反,即得到偶校验电路。

6-96采用3块74x682和必要的门电路设计一个24位比较器,将2个24位的无符号数P和Q进行比较,产生2位输出表达P=Q和P>Q。

解:

利用3块74x682(8位数值比较器)分别进行高中低3个8位段的比较;

将各段的PEQQ_L进行NAND运算,可以得到PEQQ(P=Q);

利用下式可以得到PGTQ(P>Q):

电路连接图如下所示:

6-97设计一个3位相等检测器,该器件具有6个输入端:

SLOT[2..0]和GRANT[2..0],一个低电平有效的输出端MATCH_L。

利用表6-2,6-3提供的SSI和MSI器件,设计出最短时间延迟的器件。

解:

采用表6-3的74FCT682,延迟时间为11ns。

器件连接图如下: