电子琴实验报告乐曲硬件演奏电路设计本科论文.docx

《电子琴实验报告乐曲硬件演奏电路设计本科论文.docx》由会员分享,可在线阅读,更多相关《电子琴实验报告乐曲硬件演奏电路设计本科论文.docx(22页珍藏版)》请在冰豆网上搜索。

电子琴实验报告乐曲硬件演奏电路设计本科论文

武夷学院实验报告

课程名称:

逻辑设计与FPGA项目名称:

乐曲硬件演奏电路设计

姓名:

专业:

微电子学班级:

14微电子学号:

04实验日期

、实验预习部分:

1.实验目的:

学习利用数控分频器设计硬件乐曲演奏电路。

2.实验原理:

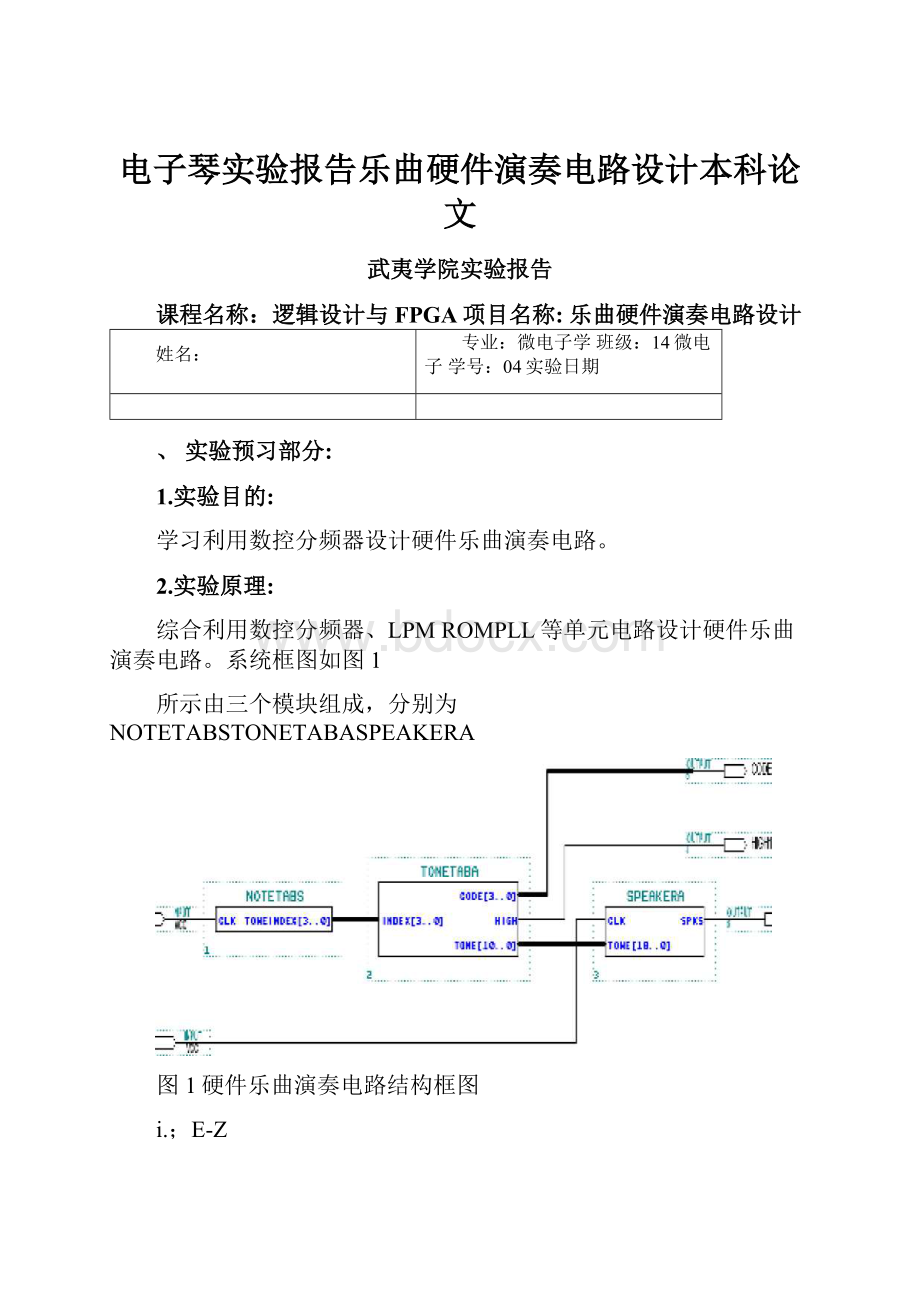

综合利用数控分频器、LPMROMPLL等单元电路设计硬件乐曲演奏电路。

系统框图如图1

所示由三个模块组成,分别为NOTETABSTONETABASPEAKERA

图1硬件乐曲演奏电路结构框图

i.;E-Z

NOTETAB模块(把教材图9-4中的CNT138T和MUSIC模块合在一起即为此模块)类似于弹琴人的手指;TONETAB模块类似于琴键;SPEAKER类似于琴弦或音调发生器。

音符的频率由SPEAKER模块(与教材图9-4中的SPKEF模块对应)获得,这是一个数控分频器。

由其CLK端输入一具有较高频率(12MHZ的信号,通过SPEAKER分频后由SPKOU输出。

SPEAKER对CLK输入信号的分频比由11位预置数TONE[10..0]决定。

SPKOU的输出频率将决定每一音符的音调,这样,分频计数器的预置值TONE[10..0]与SPKOU的输出频率就有了对应关

系。

例如在TONETAB模块(与教材图9-4中的F_COD模块对应)中若取TONE[10..0]=1036,将发出音符“3”音的信号频率。

音符的持续时间需根据乐曲的速度及每个音符的节拍数来确定,TONETAB模块的功能首先

是为SPEAKER提供决定所发音符的分频预置数,而此数在SPEAKER输入口停留的时间即为此音符的节拍值。

TONETAB模块是乐曲简谱码对应的分频预置数查表电路,其中需设置“梁祝”乐曲全部音符所对应的分频预置数,共13个,每一音符的停留时间由音乐节拍和音调发生器模块NOTATAB的CLK的输入频率决定,在此为4HZ这13个值的输出由对应于TONETAB的4位输入值INDEX[3..O]确定。

在NOTETAB中设置了一个8位二进制计数器(计数最大值为138),作为音符数据ROM的地址发生器。

这个计数器的计数频率选为4HZ即每一计数值的停留时间为0.25秒,恰为当全音符设为1秒时,四四拍的4分音符持续时间。

例如,“梁祝”乐曲的第一个音符为“3”,此音在逻辑中停留了4个时钟节拍,即1秒时间,相应地,所对应的“3”音符分频预置值为1036,在SPEAKER的输入端停留了1秒。

随着NOTETAB中的计数器按4HZ的时钟频率作加法计数时,即随地址递增时,音符数据ROM中的音符数据将从ROM通过TONEINDEX[3..0]端口输向TONETAB,模块,乐曲就开始连续自然地演奏起来了。

具体参考教材实验9-1中说明。

3.实验仪器:

PC机1台QuartusII系统

开发板1块开发板外接扬声器

4.实验步骤及方法:

分模块设计和仿真测试,通过后联合仿真测试,最后下载到硬件中测试。

5.注意事项:

所有实验数据放入一个文件夹内,并且不要把文件夹放在系统盘上,实验结束后备份好实验数据,以备教师随时查阅。

实验预习成绩(百分制)实验指导教师签字:

实验过程记录部分:

1实验过程记录:

1.1输入信号锁相环PLLO调节:

Clk

Ratio

=1-F

DC(%)

€0

1JS7

cco

cl

-

飞00

50.00

df>clkDfrequency:

50.D00MlHz

Uode:

IMcrmal

dncIkD

图2.1锁相环

管脚clk_50m(设置为B12)接入FPGA内部的50mhz的时钟信号,CO口为得到数控分屏器

模块的输入时钟750KHZ将分频比设置为1/67,即50000000HZ/67=74.6K约等于75K;cl口为2KHZ(配合下级的500分频模块),设置为:

c仁50000000HZ/25000=2KHZ

1.2500分频模块count500(即500进制的计数器):

图2.2分频电路程序设计

如图2.2,因为梁祝歌曲只用低音和中音来演奏,为1/4拍,即四分之一拍,每个音符持续0.25秒的时间。

因为前级电路已经实现了从50MHZ到2KHZ的转换,要得到4HZ的频率,则用500进制的计数器(0到499的计数)产生的进位信号对2KHZ实现500分频(输出波形分析见后)。

1.3乐曲长度控制计数器cnt138设计:

hd|宦]rmjsic.bdP

1libraryleeej

2useicee:

■兰cd_lc3giLQ_L:

l£4・目1丄;

3useleee・std_logxc^tmsi.gneci■日丄丄;

4SentitycntlSSis

5Bport(elk:

instd_logic;

6cntS:

口口匸xntegezrange0to139}j

7endcntl38;

BEarehiteetuEe:

bhvafent13Bis

9^xgnalql:

xncegerrange0co138;

10Hbegin

11Sprocess(elk)begin

12Bifelk1eventand匚丄k=Vthen

13Eifql=138tlienql<=0;

.14EelaieqlC"ql+lj

15endif;

16endxf;

17endprocess;

IBcnt6<=19endbhvr

图2.3乐曲长度控制计数器程序及元件图

经查阅《EDA技术实用教程(第五版)》可知,《梁祝》这首歌曲总共有139个音符,其中包含末尾的3个休止符。

如图2.3,因此为了产生这139音符,因此想到开发一个139进制的计数器(计数值:

0到138),实现用139状态代表139个音符。

又因为要配合下一级音符谱码存储模块的输入(ROM的输入一般为偶数位),因此将原本用7路线就可以表示完成的输出端cnt8

增加一位线宽。

注:

在本程序中,输出端cnt8由于定义成integer整型,在Quartus中被自动分

配成了7根;也可以定义成vector型,而此时需要注意配合下级电路的权位最好写成cnt8:

out

std_logic_vector(7downto0).

1.4音符谱码存储模块设计构建:

1.4.1ROM的设置:

图2.4音符谱码存储模块ROM

音符谱码存储模的主体构想,是为了让前级模块所产生的139个状态与实际音符(DoReMi

FaSoLaSi)构成映射。

因此需要构建一个包含《梁祝》乐谱的mif文件。

1.4.2构建《梁祝》乐谱.mif文件:

文件(町

锚(E)

式(O〕fe(V)K

Idepth=

256;

WIDTH二

I;

ADDRESS

RADIX

=UNS;

DATA_RADIX=UNS.

CONTENT

BEGIN

00

3;

01

3;

02

3;

03

3:

04

5;

05

5;

06

5;

07

6.

08

8;

09

8;

10

8;

11

9;

12

6.

13

8;

14

5;

15

5;

16

12:

17

12;

图2.5《梁祝》乐谱(部分截取)

因此综上所述,结合1.3的分析,音符谱码存储ROM即输入为8位数据线,含256bit数据(实际只用了139bit);输出为4根线,这是由于《梁祝》这首歌曲只有低音的123567,以及中音的12356合高音部分的1,加上休止符一共13个状态,因此用4根数据线完全足够。

出于简化电路设计原则以及综合考虑电路测试的难易程度,我将高音部分的1当做中音的7

来处理,将13个状态音符分为低音音符,中音音符和休止符;这样的好处是:

在测试时候,只需用一个LED的亮灭并结合七段数码管来具体表示播放的音符,此时若灯亮且七段数码管显示为“7”,实际代表输出为高音的“DO'。

注:

在以下的段落中,若出现“中音”,则用以表示“中

音”的1235和“高音”的1.

lUsEaryle-ee;

usqiee«BBtd_logic_lL64・all?

Hentityf=e^«leIs

BpD^t-(TNX:

i?

ii;t.d_.l.ag'ic_v»ctigEi3dpvFitiQ0)iCODE:

Qutstd_logie_veetordownto0];

Si:

cutJtd_Lagic1;

TOO;cutc^vectcix(10damtci0))

endp

@aE-chitecxuzrsoneaff_c&deis

Dbe:

g±nsearchTprocassCTNX)bagin

wh»n.11Q00O,T

=>

TOO

<-rF11X11111111"

CODE<-,rOOOD

wh&n^OOOl1-

TOO

31100000101"

F

CODE<=,,OOCI1

whBEL^OOlO^

«>

TOO

w^OLHODlOOOO"

CCDE«

GOLD

when^Oll11

=>

TOO

^"LOOOQGOllM"

CODE<='

0011

whetinOlOln,

TOO

CODEC-'

01<31

«hsnnG110ra

=>

TOO

<=rBLD100Q01G10r,

CODE<='

0110

whe-n^Olll*

=■>

TOO

<-'"10101011100**

«•

CQDE'L-'

0111

whsnn1000""

=>

TOQ

^-ra101IQ000010"

CQDE<^'

0001

=>

TOO

<=ifcL01110Q1000ifc

•

CODE<=i

0010

■a

too

^-^LLOaQQOOllO"

CDDE<-'

0011

whenH1100"

TOO

<=,kLlDD1010110"

F

CODE<=*

Olfil

wheEi^HOl"1

TOO

<-n.LLQiaai£j(j100r»

i

CODE<«!

0110

=>

TOO

<=",liLOilOOOGOO,i

r

CODE<='

OOCil

INX卩・期CODEJ3..0]

H

TOOflO.O]

€

7呂

B

SeaseInx丄日

IE

二

;—773-;

;Hc-'Or;--llS7;iHc=*OFf—l;H*-10*■;"1372;

wheelath.ej:

sTOO<-"11111111111";CCDE«--,!

,O-DDn"j:

H<-'0r;--2Q4"rand:

j

endpzaeeaa;

«nd;

xe

13

:

L

2B

1.5分频预置查表电路fcode构建:

图2.6fcode模块代码及原理图

由前级电路可知,从mscicsionROM模块的输出端q输出了13个音符(13个状态),而扬声器发出声音的实质是通过播放不同的声音频率实现的,而要实现将统一的频率分为不同的频率则必须引入实现分频功能的模块,由《数字电子技术基础(第五版)》的“时序电路章节”知识

可知:

普通的实现分频功能的计数器实现分频的原理是当计数值达到计数器最大模值N时,跳

转到“预置数M',因此可以实现“N-M+1'分频的功能;由此,我想到,如果将原本固定的“预置数”端,用一个模块代替,进而产生可以随需求变化而变化的预置数,这样就可以实现对不同音符频率的分频功能。

因此,本级模块最主要功能是将已有音符映射成对应的预置数。

因为下级模块“数控分频器”的最大计数值为11位2进制数,因此本级模块的输出TOO也为11位线宽。

因为下级模块数控分频器的最大计数值为2047,预置数为NT,计数模值为

2047-NT+1=2048-NT,女口NT=912,那么计数模值(分频系数)为2047-912=1135,因此将十进制的912改为^一位二进制的01110010000,赋值给T0g(如图2.6),作为输出。

同时COD歸输出对应的音符(1到7),送至下级电路“谱码指示模块”;同时为了区别输出的音符为“低音”的(1到7)还是“中音”的(1到7),因此定义输出端口H,并接到FPGA的一个LED若灯不亮则表示为“低音”,若点亮则表示“高音”,再配合谱码指示模块中的“七段数码管”上显示的数值进而显示具体的音符。

library

useieee.atd_10gic_1164,all;

uselee已.5td_logic_aritti.all;

useieee,stti_logic_unsigned»all;

EentityspkerisSport(cllc:

inatd^logic;

tn:

std_logic_vector|10downto0};spks:

outSLd^lagic};

endspker;

SarchitecturetoJitofspkeiis

Hbegin

Eprocess(elk)

variableql:

stdlogicvector(IOdownto0);begin

Bifelk1eventandelk=111then

ifql二w11111111111

S|thenql:

^tn;apta<■'1';

Belseql尸ql+1;splcs^'0';

endif;

endif;

endprocess;

end;

=Delk

nstID

If

■■

t

*

*Mr**r**i***i*«c*m«*i*»*

«i■

图2.7数控分频器模块

spker代码及原理图

1.6数控分频器模块spker设计:

如图2.7,该模块主要作用是将预置数通过计数器与对应音符的频率构成映射。

由于数控分

频器所给的的输入时钟为750KHZ由之前的分析,数控分频器的最大计数值为11位2进制数,

即2X1=2047,逢2047后预置NT,为加法计数,输出为进位信号,进位信号总是取最大状态2047的译码。

不妨取1.5的假设,当NT=912时,计数模值:

2047-912=1135,数控分频器输出频率为750KHZ/1135=660HZ再由下级电路模块对数控分频输出进行2分频,则输出频率为660HZ/2=330HZ对应为低音的2(Re)。

(其余见附录一)即,对应总公式:

fo=[750KHZ/(2048-TN)]/2

其中,f0为音符频率;丁“即(TOO为预置数。

1.7谱码指示模块的设计:

1.7.1七段数码管译码转换模块的设置:

libraryieee;

use.std_logic_1164*all;useisee.std_logic_un3igned■旦11;

Sentitydecadeis

Zport(d:

instd_logic_vector(3dowuto0);sw:

outstd_logic_vector(6downto0));enddecode;

3architeatuiebhvofdecodeis

Obegin

Oprocess{d}begxn

Ssearch:

casedis

when"00DOrr=>sw<-f,1000000F,;

when"OD01rf=>sw<=,,1111001.n;

when"0010rr=>sw<=r,0100100F,;

when"0011rf=>sw<=t,01100CiOM;

when"010Drr=>sw<=f,1001100M;

whenn0101ri=>sw<=rr0010C'10M;

when"OHOrr=>sw<=T,CiOOOCHOn;

whenrT0111TT=>sw<=T,1111000";whenothers=>5W<="XXXXXXXM;

endcase;

endprocess;

endbhv;

图2.8七段数码管译码转换模块代码及原理图

如图13所示T'触发器由D触发器加非门电路组成,构成一个二分频电路,由于直接从数控分频器出来的信号是脉宽极窄的信号,为了有利于驱动扬声器而添加此电路。

由1.5分析可知,f_code模块代的输出端COD为4根线,而查阅PFGA开发板手册可知七段数码管的引脚有8个(包含一个小数点)。

因此,若想在数码管上显示对应的音符,必须开发一个模块,将4位二进

制数(13个状态音符)用七位二进制数表示,对应7个输出端。

(因为本实验中用不到小数点,所以只考虑用数码管显示数值部分的7段LED

1.7.2

七段数码管的设置:

图2.9谱码指示模块总原理图

如图2.9,因为译码电路属于组合电路,属于异步,不受CLKS制,所以本级模块不设CLK端。

结合(附录二)由于FPG/的七段数码管是共阳极接法,所以输出为0则点亮,例如音符“000T,对应输出“1111001”。

图2.10二分频模块原理图

1.8二分频模块的设计:

由1.6可知,承接数控分频器模块的输出频率,为输出真正的音符频率,还需要一个二分频模块实现,直接调用D触发器,外接非门构成T'触发器,实现二分频功能。

此外由于从数控分频器输出的某些音符的频率的占空比很小,如果不加本模块,会出现音符出现的声音非常短暂的情况,因此,本模块还起到提高占空比50%进而提升功率的作用。

2.实验现象及原始数据记录:

2.1设计电路总图:

图2.11总原理图

2.2开发板管脚设置图:

Named:

|B©丘吐X|7||荷:

Pins油、

NodeName

Direction

location

I/OBaric

VREFGroup

I/OStandard

1

EF

dk50m

Input

PINJ12

7

B7.N1

2.5V(default)

2

HLYZS

Output

PINJI

1

B1N1

2.5V(defeult)

3

spkjot

Output

PIO12

3

B3.N1

2.5V(default)

4

sw[6]

Output

PIN_F13

7

B7_N1

2.5V(defeult)

5

sw[5]

Odtput

PIN_F12

1

B7JI1

2.5¥(default)

6

sw[4|

Output

PIN_GI2

7

B7_N1

2.SV(default)

7

sw[3

Qjtput

PINHL3

7

B7_N1

2.5V(default)

3

sw[2]

Output

PINHL2

7

B7N1

2.5V(defeult)

9

sw[l]

Output

PINJU

1

B7N1

2h5V(default)

10

sw[0]

Ojtput

PINE11

7

B7N1

2.5V(defeult)

11

«kwnode>>

图2.12全体管脚映射图

附录

音符名

频率血)

分频

计数初值

音符名

频率Oh)

分频

计数

系数

系数

初值

休止符

375000]

0

2047

中音4

796.178

468

1579

师育1

291349

1274

773

屮音5

882.353

425

1622

低音2

330.396

1135

912

中音林

989.446

379

1668

低咅3

370.92

1011

1036

中音7

1136.363

330

1717

低音4

§86.598

970

1077

岛音1

1175,549

319

1728

低音5

394,737

9弓0

1197

高音2

1353,790

277

1770

低音6

嘶376

757

1290

岛音:

t

1512.097

248

1799

低音7

555.56

675

1372

爲音4

1609.442

233

1B14

中音1

588.697

637

1410

"■ti''”aV-rr冋IJ□

1802.884

20S

1839

中音2

638.84

587

1480

廿音6

2027.027

185

1862

+S3

742.574

505

1542

商音7

2272.727

165

1882

附录二

3

盘号名

FPGA号

HEXOD[O]

PINE11

■

SevenSegmentDigit0[0]

HEX0_D[1]

PIN_F11

SevenSegmentDigit0[1]

HEX0_D[2]

PIN_H12

SevenSegmentDigit0(2]

HEX0^D[3]

PINH13

Ml

SevenSegmentDigit0[3]

HEX0D[4]

PING12

■-——

SevenSegmentDigit0[4]

HEX0_D(5]

PIN_F12

SevenSegmentDigit0[5]

HEX0_D[6]

PIN_F13

SevenSegmentDigit0(6]

HEXO^DP

PIND13

SevenSegmentDecimalPoint0

HEX1_D[0]

PIN.A13

SevenSegmentDigit1[0]

HEX1_D[1]

PIN_B13

SevenSegmentDigit1[1]

HEX1_D[2]

PIN_C1S

SevenSegmentDigit1[2]

HEX1D[3]

PINA14

SevenSegmentDigit1[3|_

HEX1_D[4]

PINB14

^■l

SevenSegmentDigit1[4]

HEX1_D[5]

PIN_E14

SevenSegmentDigit1[5]

HEX1_D[6]

PIN_A15