实验五 计数器的设计实验报告.docx

《实验五 计数器的设计实验报告.docx》由会员分享,可在线阅读,更多相关《实验五 计数器的设计实验报告.docx(10页珍藏版)》请在冰豆网上搜索。

实验五计数器的设计实验报告

实验五计数器的设计——实验报告

邱兆丰15331260

一、实验目的和要求

1.熟悉JK触发器的逻辑功能。

2.掌握用JK触发器设计同步计数器。

二、实验仪器及器件

1、实验箱、万用表、示波器、

2、74LS73,74LS00,74LS08,74LS20

三、实验原理

1.计数器的工作原理

递增计数器----每来一个CP,触发器的组成状态按二进制代码规律增加。

递减计数器-----按二进制代码规律减少。

双向计数器-----可增可减,由控制端来决定。

2.集成J-K触发器74LS73

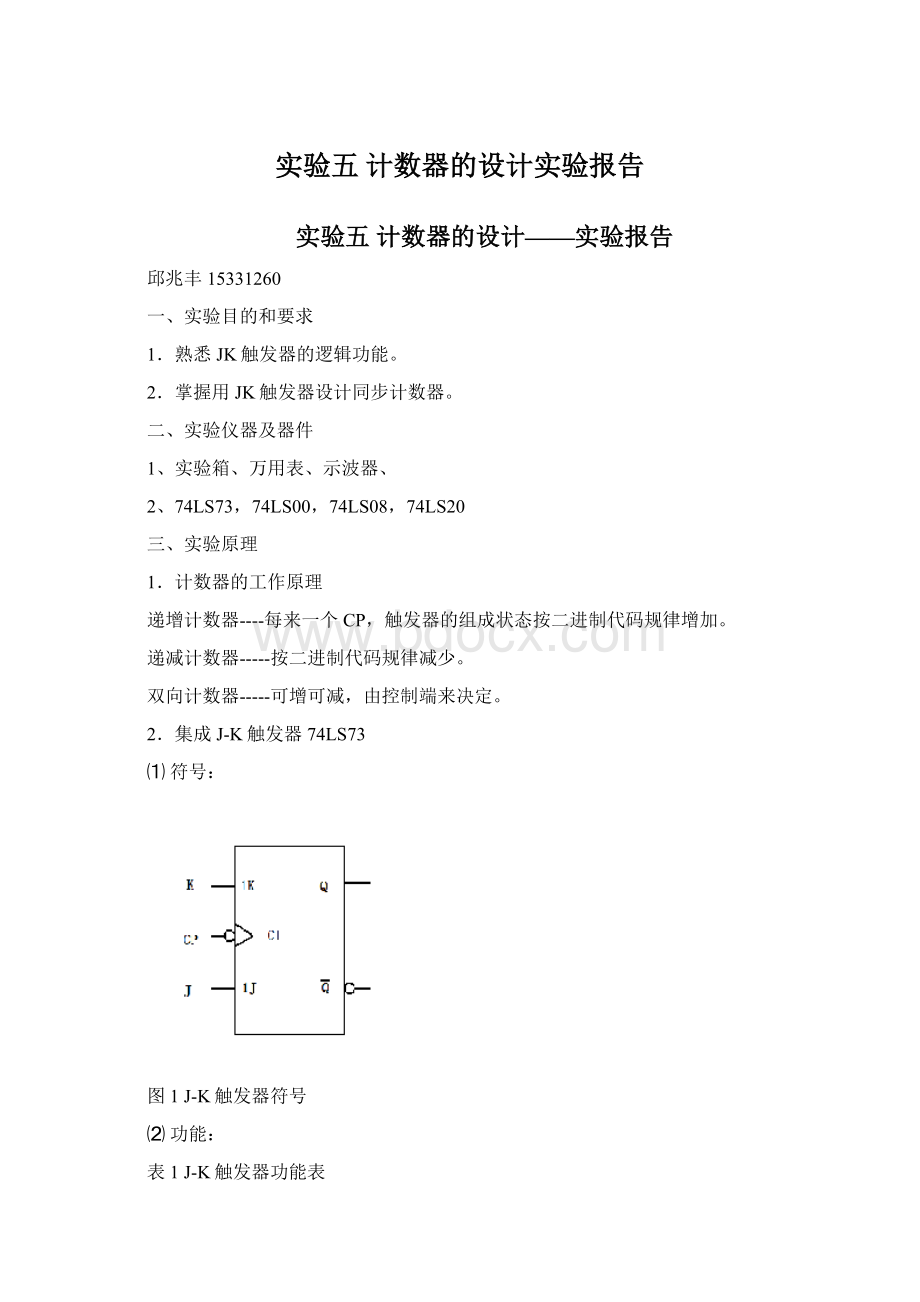

⑴符号:

图1J-K触发器符号

⑵功能:

表1J-K触发器功能表

CP

J

K

功能

↓

↓

0

0

0

0

保持

0

0

1

1

↓

↓

0

1

0

0

清零

0

1

1

0

↓

↓

1

0

0

1

置位

1

0

1

1

↓

↓

1

1

0

1

翻转

1

1

1

0

⑶状态转换图:

图2J-K触发器状态转换图

⑷特性方程:

⑸注意事项:

①在J-K触发器中,凡是要求接“1”的,一定要接高电平(例如5V),否则会出现错误的翻转。

1触发器的两个输出负载不能过分悬殊,否则会出现误翻。

2J-K触发器的清零输入端在工作时一定要接高电平或连接到实验箱的清零端子。

3.时序电路的设计步骤

内容见实验预习。

4、实验内容

1.用JK触发器设计一个16进制异步计数器,用逻辑分析仪观察CP和各输出波形。

2.用JK触发器设计一个16进制同步计数器,用逻辑分析仪观察CP和各输出波形。

3.设计一个仿74LS194

4.用J-K触发器和门电路设计一个特殊的12进制计数器,其十进制的状态转换图为:

5.考虑增加一个控制变量D,当D=0时,计数器按自定义内容运行,当D=1时,反方向运行

5、实验设计及数据与处理

实验一

16进制异步计数器

设计原理:

除最低级外,每一级触发器用上一级触发器的输出作时钟输入,JK都接HIGH,使得低一级的触发器从1变0时高一级触发器恰好接收下降沿信号实现输出翻转。

实验二

16进制同步计数器

设计原理:

除最低级外,每一级的JK输入都为所有低级的输出的“与”运算结果

实验三

仿74LS194

设计原理:

前两个开关作选择端输入,下面四个开关模仿预置数输入,再下面两个开关模仿左移、右移的输入,最后一个开关模仿清零输入。

四个触发器用同一时钟输入作CLK输入。

用2个非门与三个与门做成了一个简单译码器。

对于每一个触发器,JK输入总为一对相反值,即总是让输入值作为输出值输入。

对于每一个输入,当模式“重置”输出为1时,其与预置值结果即触发器输入;当模式“右移”、“左移”输出为1时,其值为上一位或下一位对应值;当各模式输出均为0时各触发器输入为0,使输出为0。

实验四

设计原理:

在12进制同步计数器中,输出的状态只由前一周期的状态决定,而与外来输入无关,因此目标电路为Moore型。

而数字电路只有0和1两种状态,因此目标电路要表达12种状态需要用4个变量、、、的16种组合中的12种。

现定义十进制数01~12的对应二进制数为输出状态,可得目标电路的状态转换表如下:

表212进制同步计数器状态状态转换表

CLK

1

0

0

0

1

2

0

0

1

0

3

0

0

1

1

4

0

1

0

0

5

0

1

0

1

6

0

1

1

0

7

0

1

1

1

8

1

0

0

0

9

1

0

0

1

10

1

0

1

0

11

1

0

1

1

12

1

1

0

0

13

0

0

0

1

本实验选择J-K触发器,根据状态转换表以及J-K触发器特性方程:

得到目标电路方程如下:

输出方程:

、、、

驱动方程:

Q0一个CP发生一次变化,因此

。

Q1每当Q0为1时,发生变化,因此

。

Q2在Q1Q0都为1以及12(即1100的时候)发生变化,因此

J2=K2=Q1nQ0n+Q3nQ2n

Q3在Q2Q1Q0都为1的时候,以及12的时候发生变化,因此

J3=K3=Q0nQ1nQ2n+Q3nQ2n。

状态方程:

(2)由以上三种方程可以画出逻辑图如下:

实验五

由于电脑重装原来打的文件没了,照一下实验报告里的

五、实验心得与体会

1、通过此次实验对于触发器的逻辑功能有了更深的了解,学会了用J—K触发器实现同步电路或者异步电路,并且可以用多种方法完成这次实验。

除了上述方法,也可以采用四个触发器实现1——15计数的电路,并对其进行改进,使其在13(即1101的时候),Q3Q2进行清零。

当然,达到相同目的的J和K也是不唯一的。

2、在使用触发器前,要对其进行检查。

具体方法是将J、K以及清零端接高电平,C1接CP,将Q接led灯,若灯每次状态都发生改变,则证明触发器没有问题。

在实验中若是出现了问题,要进行故障检查。

有以下的检查方法

⑴查线法

由于在实验中大部分故障都是由于布线错误引起的,因此,在故障发生时,复查电路连线为排除故障的有效方法。

应着重注意:

有无漏线、错线,导线与插孔接触是否可靠,集成电路各脚是否与插座插牢、集成电路是否插反等。

⑵观察法

用万用表直接测量各集成块的Vcc端是否加上电源电压;输入信号、时钟脉冲等是否加到实验电路上,观察输出端有无反应。

重复测试观察故障现象,然后对某一故障状态,用万用表测试各输入/输出端的直流电平,从而判断出故障是否由插座、集成块引脚连接线等原因造成的故障。

3、在此次实验中,最容易发生的错误就是弄混了Q与Q反向。

在实验前一定要观察触发器的结构,使其与功能图相对应。

作为端口输出的时候,也一定要检查,输出的是Q还是Q反。