串行中断寄存器控制.docx

《串行中断寄存器控制.docx》由会员分享,可在线阅读,更多相关《串行中断寄存器控制.docx(18页珍藏版)》请在冰豆网上搜索。

串行中断寄存器控制

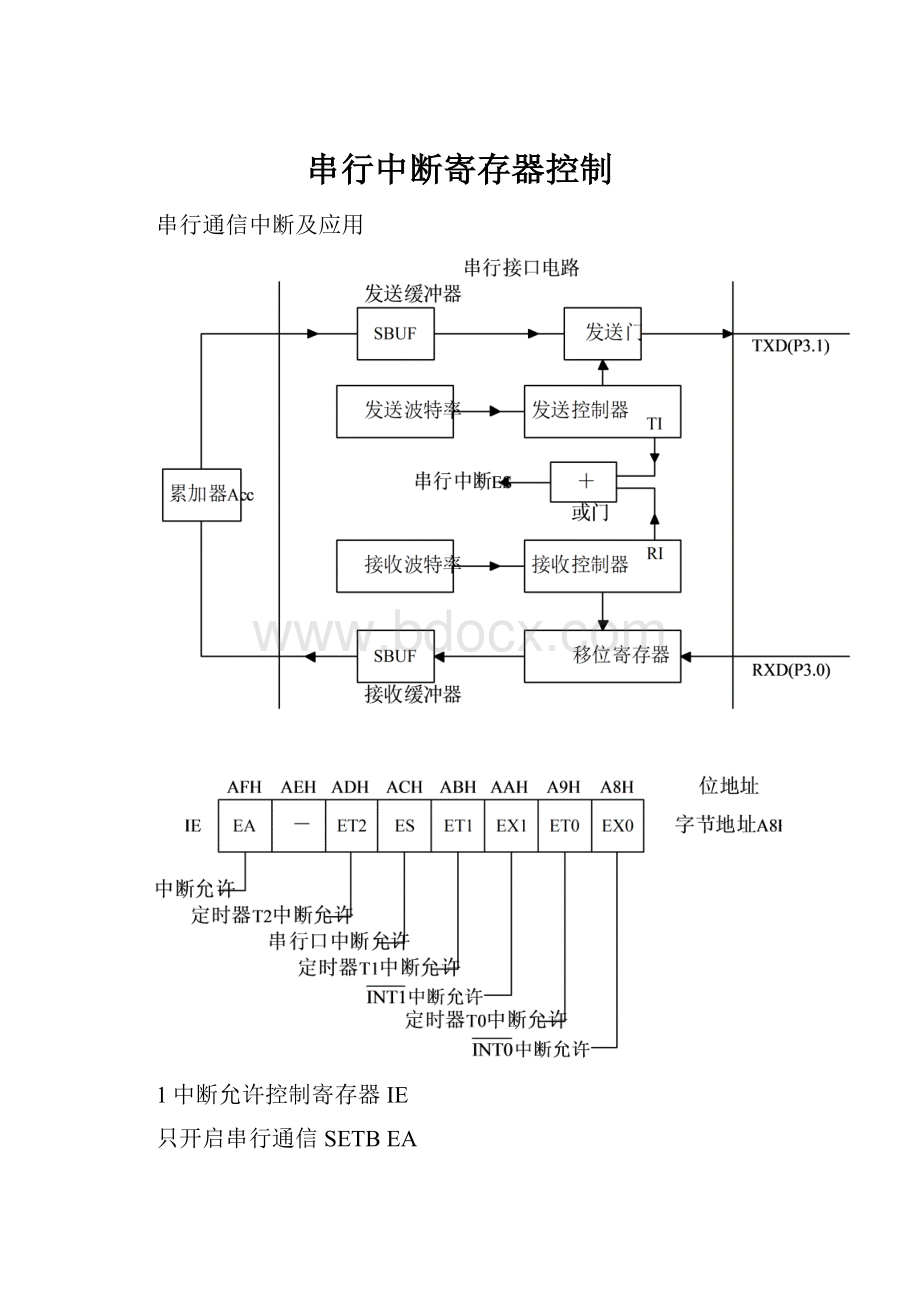

串行通信中断及应用

1中断允许控制寄存器IE

只开启串行通信SETBEA

SETBES

或者MOVIE,#90H

2设置串行中断优先级(控制寄存器IP、IPH)

中断源的中断优先级由IPH、IP对应位编码决定

IPH.X位IP.X位优先级

000级(优先级最低)

011级

102级

113级(优先级最高)

例如串行中断优先级最高MOVIP,#0C0H

MOVIPE,#0C0H

或者SETBPS

MOVIPE,#0C0H

(IPH没有位地址功能)

3入口地址

定时/计数器T1溢出中断001BH

串行口中断0023H

ORG00H

AJMP?

?

?

ORG1BH

AJMP?

?

?

ORG23H

AJMP?

?

?

4串行口控制寄存器SCON

5进入中断服务程序后,

(1)CPU能自动清除下列中断请求标志位:

定时器T0中断请求标志TF0;

定时器T1中断请求标志TF1;

边沿触发方式下外中断的中断请求标志IE0;

边沿触发方式下外中断的中断请求标志IE1。

不自动清除

串行发送结束中断标志TI、

串行接收有效中断标志RI、

定时/计数器T2

溢出中断标志TF2、

定时/计数器T2外触发标志EXF2

(2)每一次发送和接受后都要软件清零:

串行发送结束中断标志TI、

串行接收有效中断标志RI、

如CLRTI

CLRRI

可用T1,T2溢出率的(16或)32分频作为串行口发送、接收波特率

9电源控制寄存器PCON

(电源控制寄存器PCON不能对位操作)

SMOD

GF1

GF0

PD

IDL

SMOD=0SMOD=1位被称为波特率倍增位

为了避免重装初值造成的定时误差,定时器T1最好工作在可自动重装初值的方式2,并禁止定时器T1中断。

TL1=?

、TH1=TL1=?

做TL1的备份(自动重装初值,TH1和TL1初装相同的值)

串行通信系统中常用波特率衡量通信的快慢,含义是每秒中传送的二进制数码的位数,单位是位/秒(b/s或Kb/s),

方式1、方式3计算公式

串行方式1

串行数据(低位在前,高位在后)10位

0

B0

B1

B6

B7

1

起始位

低位

数据

数据

数据

数据

数据

数据

高位

停止位

串行方式3起始位(0)、9位串行数据、一位停止位

(1)共11位

例假设系统晶振频率为11.0592MHz,通信方式约定为:

波特率2400,8位数据,奇校验。

利用串行口方式3,将存放在内部RAM30H~4FH单元中32字节数据发送给串行接收设备。

如果接收方正确接收了32字节信息,则回送AAH;否则回送55H。

根据系统晶振频率及通信波特率,用定时器T1工作在方式2的溢出率作为波特率发生器(16分频器)的输入信号,参考程序如下:

;初始化定时器T1

FHbitBIT07H;07H位单元作为通信成功标志,0表示通信成功;1表示失败

MOVA,TMOD

ANLA,#0FH

ORLA,#00100000B;定时器T1工作在方式2(即自动重装初值),定时状态,由TR1控制

MOVTMOD,A

MOVTL1,#0F4H

MOVTH1,#0F4H;波特率为2400

CLRET1; T1用作波特率发生器,禁止T1中断

SETBTR1;启动定时器T1;初始化串行通信口

MOVSCON,#11000000B;方式3,SM2位为0,以便接收奇偶校验位

MOVPCON,#00H;波特率不倍增;将30~4FH缓冲区内32字节发送给接收方

CLRFHbit;成功标志清零

MOVR0,#30H;发送数据缓冲区首地址送R0

MOVR7,#20H;发送字节数送R7

CLRTI;清除TI

LOOP1:

MOVA,@R0;取发送数据

MOVC,PSW.0;取奇偶标志

MOVTB8,C;奇偶标志送TB8

MOVSBUF,A;数据送SBUF寄存器,启动发送过程

LOOP2:

JNBTI,LOOP2;如果TI不是1就循环,等待发送中断标志有效

CLRTI;清除TI,以便发送下一字节

INCR0;数据指针加1,指向缓冲区内下一数据

DJNZR7,LOOP1;指定字节数据未发送结束,循环;发送结束,准备接收返回码

CLRRI;清除接收中断标志

SETBREN;允许接收

LOOP3:

JNBRI,LOOP3;等待接收中断有效

CLRREN;停止接收

MOVA,SBUF;把结果送A

XRLA,#0AAH;返回码与AAH异或

JZREEND;如果返回码是AAH,则退出

SETBFHbit;如果返回码不是AA,则将接收成,功标志为1(即失败)

REEND:

RET

当串行通信的波特率较高时,多采用查询方式来确定一帧信息是否发送结束,如本例所示。

对于接收过程来说,如果不能确定发送方是否会发送信息以及什么时候发送时,最好使用中断方式。

为此,上例发送、接收程序段改为(发送过程采用查询方式;接收过程采用中断方式

;初始化定时器T1

FHbitBIT07H; 07H位单元作为通信成功标志,0表示通信成功;1表示失败。

MOVA,TMOD

ANLA,#0FH

ORLA,#00100000B;定时器T1工作在方式2(即自动重装初值),定时状态,由TR1控制

MOVTMOD,A

MOVTL1,#0F4H

MOVTH1,#0F4H;波特率为2400

CLRET1; T1用作波特率发生器,禁止T1中断

SETBTR1;启动定时器T1;初始化串行通信口

MOVSCON,#11000000B;方式3,SM2位为0,以便接收奇偶校验位

MOVPCON,#00H;波特率不倍增;将30~4FH缓冲区内32字节发送给接收方

CLRFHbit;成功标志清零

MOVR0,#30H;发送数据缓冲区首地址送R0

MOVR7,#20H;发送字节数送R7

CLRES;禁止串行中断,即在发送过程中,采用查询方式

CLRTI;清除TI

LOOP1:

MOVA,@R0;取发送数据

MOVC,PSW.0;取奇偶标志

MOVTB8,C;奇偶标志送TB8

MOVSBUF,A;数据送SBUF寄存器,启动发送过程

LOOP2:

JNBTI,LOOP2;如果TI不是1就循环,等待发送中断标志有效

CLRTI;清除TI,以便发送下一字节

INCR0;数据指针加1,指向缓冲区内下一数据

DJNZR7,LOOP1;指定字节数据未发送结束,循环;发送结束,准备接收返回码

CLRRI;清除接收中断标志

SETBREN;允许接收

SETBES;允许串行中断,即在接收过程中采用中断方式

RET;返回

;串行口中断服务程序

UART:

PUSHAcc;保护累加器Acc

PUSHPSW

MOVA,SBUF;把结果送A

XRLA,#0AAH;返回码与AAH异或

JZREEND;如果返回码是AAH,则退出

SETBFHbit;如果返回码不是AA,则将接收成功标志为1(即失败)

REEND:

CLRREN;停止接收

CLRRI;清除接收中断标志

POPPSW

POPAcc

RETI

多机通信

主机与特定从机的通信过程如下:

(1)主机发送从机地址(TB8位为1),然后进入接收状态,接收从机应答信号(实际上就是相应从机的地址信息)。

(2)所有从机均接收主机送出的地址信息,并与本机地址比较,当接收到的地址信息与本机地址相符时,表示被选中,将本机地址信息发给主机,然后执行“CLRSM2”指令,使SM2位为0,以便接收主机随后送出的数据信息。

对于未被选中的从机,SM2位依然为1,因此不接收主机送出的数据信息。

(3)主机收到从机的应答信号后,发出数据信息(TB8位为0)。

(4)从机正确接收主机数据信息后,发应答信号给主机,并将SM2置1,主机与从机通信过程结束。

从机与主机的通信过程如下:

(1)发送前从机先检测TXD引脚,如果在(20/波特率)时间内,TXD引脚依然为高电平,则表明没有其他从机给主机发送信息,主机的RXD引脚处于空闲状态。

(2)从机确认主机的RXD引脚处于空闲状态后,发出地址信息(TB8位为1)到主机。

(3)从机收到主机的应答信号(实际是从机地址信息)后,发送数据(TB8位为0)给主机,然后令从机的SM2为0,以便接收主机发送的接收正确信号。

(4)主机正确接收后,再发接收正确信号给从机。

(5)从机收到主机发来的“接收正确”信号后,表明通信过程结束——可将SM2位置1,以便从机能接收主机发送的地址信息。

帧错误检测

增强型UART口通过检测“停止位”的有无来判别方式2、3下的串行接收是否正确,这就是所谓的“帧错误检测”功能。

在增强型UART口中,SCON寄存器的b7位具有SM0/FE(FramError)双重功能(由PCON寄存器的b6,即SMOD0位控制:

当SMOD0位为0时,SCON寄存器的b7位是SM0;而当SMOD0位为1时,SCON寄存器的b7位是FE)。

当接收不到有效停止位时,SCON寄存器的b7位(即FE)置1。

当FE为1时,表示接收的数据无效,不装入SBUF寄存器,RI也不置1。

帧错误检测仅对方式2、3有效,原因是方式0不能用于串行通信,而方式1本身就具有停止位检测功能,只是没有记录检测结果而已,因为在方式1中,只有接收到有效的停止位时,RI才有效

启用帧错误检测功能的串行口初始化过程如下:

初始化定时器T1或T2,定义串行口接收波特率→初始化SCON寄存器,定义串行口工作方式(只能是2或3)→执行“ORLPCON,#40H”指令将PCON.6位置1,使SCON.7位具有FE功能→执行“CLRRI”指令,清除接收中断→执行“SETBREN”启动接收过程→检测FE标志(如果FE标志有效,则说明收不到有效停止位,数据出错;反之,如果FE无效,而RI有效,则说明数据接收正确)。

值得注意的是,FE有效后,即使下一数据帧能正确接收也不自动清除,因此FE有效,在完成错误信号处理后需要手工清除。

地址自动识别

在方式2、3中,SM2位可作多机通信控制位。

当SM2位为1时,只有收到的第九位数据,即RB8为1时,RI才有效;而当SM2位为0时,便放弃对地址的识别,一律视为数据处理。

采用硬件地址自动识别技术后,只要从机的SM2位为1,则收到的第一帧信息必然是本机的地址信息,可立即将从机的SM2位置0,接收主机随后送来的数据信息,无须判别所收到的地址信息是否就是本机地址,待数据接收结束后,便立刻将SM2位置1,等待下一次通信,于是提高了主从机之间的通信效率。

从图4-26中看出,采用地址自动识别功能后,有效接收条件是:

主机发出的地址与从地址屏蔽码SADEN按位相与后和从机地址寄存器SADDR比较,若相同,则相应从机接收中断有效。

这样主机通过发出特定从机地址与单一从机通信、 通过发出给定地址与一组从机通信、 通过发出广播地址与所有从机通信。

构造从机地址编码、 从机地址屏蔽码的方法很多,例如在一主四从多机系统中,从机地址码和从机地址屏蔽码可按如下方法构造:

从机编号0机1机2机3机

从机地址屏蔽码10100001101000101010010010101000

从机地址码11110000111100001111000011110000

SADEN和SADDR相与1010***01010**0*1010*0**11110***

选定123机地址10100001不中中中

选定023机地址10100010中不中中

选定013机地址10100100中中不中

选定012机地址10101000中中中不

选定0机地址10101110中不不不

选定1机地址10101101不中不不

选定2机地址10101011不不中不

选定2机地址10100111不不不中

广播地址码11110000中中中中

RS-232C串行接口标准中主信道重要信号含义

RS-232C串行接口标准主信道重要信号含义:

TXD:

串行数据发送引脚,输出。

RXD:

串行数据接收引脚,输入。

DSR:

数据设备(DCE)准备就绪信号,输入,主要用于接收联络。

当DSR信号有效时,表明本地的数据设备(DCE)处于就绪状态。

DTR:

数据终端(DTE)就绪信号,输出。

用于DTE向DCE发送联络,当DTR有效时,表示DTE可以接收来自DCE的数据。

RTS:

发送请求,输出。

当DTE需要向DCE发送数据时,向接收方(DCE)输出RTS信号。

CTS:

发送允许或清除发送,输入。

作为“清除发送”信号使用时,由DCE输出,当CTS有效时,DTE将终止发送(如DCE忙或有重要数据要回送DTE);而作为“允许发送”信号使用时,情况刚好相反:

当接收方接收到RTS信号后进入接收状态,就绪后向请求发送方回送CTS信号,发送方检测到CTS有效后,启动发送过程。

图4-27RS-232C接口插座

25芯D型插座RS-232C接口信号名称及主要信号流向; 9芯D型插座上的RS-232C接口信号名称及流向

3.电平转换

为保证数据可靠传送,RS-232C标准规定发送数据线TXD和接收数据线RXD均采用EIA电平,即传送数字“1”时,传输线上的电平在-3~-15V之间;传送数字“0”时,传输线上的电平在+3~+15V之间。

但单片机串行口采用正逻辑的TTL电平,这样就存在TTL电平与EIA电平之间的转换问题,例如当单片机与PC机进行串行通信时,PC机COM1或COM2口发送引脚TXD信号是EIA电平,不能直接与单片机串行口接收端RXD引脚相连;同样单片机串行口发送端TXD引脚输出信号采用正逻辑的TTL电平,也不能直接与PC机串行口COM1或COM2的RXD端相连。

RS-232C与TTL之间电平转换芯片主要有传输线发送器MC1488(把TTL电平转成EIA电平)、传输线接收器MC1489(把EIA电平转成TTL电平)以及MAX232系列RS232电平转换专用芯片。

其中传输线发送器MC1488含有4个门电路发送器,TTL电平输入,EIA电平输出;而传输线接收器MC1489也含有4个接收器,EIA电平输入,TTL电平输出,但由MC1488和MC1489构成的EIA与TTL电平转换器需要±12V双电源,而单片机应用系统中一般只有+5V电源,如果仅为了实现电平转换增加±12V电源,体积大、成本高。

而MAX232系列芯片集成度高,单+5V电源(内置了电压倍增电路及负电源电路)工作,只需外接5个容量为0.1~1μF的小电容即可完成两路RS-232与TTL电平之间转换,是单片机应用系统中最常用的RS-232电平转换芯片,其内部结构及典型应用如图4-28所示。

图4-29只有RTS、CTS联络信号的串行通信图4-30没有联络信号的串行通信

在MCS-51单片机应用系统中,由于彼此之间需要传输的数量少,就常使用没有联络信号的串行通信,只需明确如下的收发条件即可:

波特率(CPS)。

发送、接收双方的波特率必须相同,误差不得超过一定的范围,否则不能正确接收。

数据位长度(8位还是9位)。

·校验有无及校验方式。

在串行通讯中,除了使用奇偶校验方式,还可以使用其他的检验方式——和校验(往往仅保留和的低8位,甚至低4位)、某一特征数码的倍数等,或同时使用两种校验方式。

正确接收后的应答信号。

·确定信息帧起始标志。

常使用发送信息(命令、数据)中不可能出现的状态编码作为信息帧的起始标志。

·确定信息帧结束标志。

4.5增强型MCS-51芯片识别和仿真

1.判别芯片内核类型

方法一:

由于增强型MCS-51内核一般提供关闭ALE功能,因此对于采用片内程序存储器系统,在一简单循环程序前插入“MOV8EH,#01H”(AUXR特殊功能寄存器字节地址为8EH),然后用逻辑笔观察ALE引脚是否还有脉冲输出,即可判别该芯片是否支持ALE关闭功能,从而判别该芯片是否是增强型MCS-51内核。

方法二:

由于增强型MCS-51内核定时器T2具有时钟输出功能,因此将定时器T2定义为自动重装初值的定时状态,并允许在P1.0引脚输出时钟信号,然后用逻辑笔或万用表交流挡观察P1.0引脚状态,也能迅速判别该芯片采用何种内核。

2.在标准MCS-51仿真器使用增强型MCS-51新增硬件功能

目前市面上多数MCS-51及兼容芯片采用增强型MCS-51内核,但国内大多数用户使用的MCS-51仿真开发设备——仿真器或仿真头之一可能不支持增强型MCS-51内核芯片,只能仿真标准MCS-51,甚至随仿真开发器提供的汇编器(汇编程序)不识别增强型MCS-51新增特殊功能寄存器。

在这种情况下又如何使用增强型MCS-51及兼容芯片新增功能呢?

由于增强型MCS-51硬件资源与标准MCS-51保持兼容,因此先当标准MCS-51使用,即程序中暂时不出现增强型MCS-51新增特殊功能寄存器(位),如在涉及这些特殊功能寄存器(位)的程序段及指令前加“;”(分号)暂时注销,待程序调试无误后采用如下方法之一使用新增的硬件资源:

(1)用支持89C51RX系列CPU仿真器(头)仿真8XC5X、8XC5XX2系列增强型MCS-51内核CPU。

例如“伟福”E2000系列仿真器不能仿真8XC5X、8XC5XX2系列增强型MCS-51CPU。

但配合“POP-89C51RX”仿真头可以仿真89C51RX系列CPU,而89C51RX硬件资源与8XC5X、8XC5XX2系列增强型MCS-51内核芯片保持兼容,因此可用E2000系列仿真器,配合POP-89C51RX仿真头仿真8XC5X、8XC5XX2系列增强型MCS-51CPU。

(2)如果没有89C51RX系列仿真器、仿真头,可使用软件仿真方式。

例如在“伟福”汇编器中,在“仿真器”选择窗内,选用“伟福软件模拟器”选项,并选择E2000系列仿真器和“POP-89C51RX”仿真头。

这样就可以在“伟福软件模拟器”中直接引用8XC5X、8XC5XX2系列增强型MCS-51内核芯片新增特殊功能寄存器和寄存器位,经编译、调试(当然只能在软件模拟器环境下进行)后,将代码直接写入目标芯片,在用户板上测试。

不满意,再检查源程序,找出其中的错误并修正即可。

(3)如果汇编器不支持89C51RX芯片,不能使用“软件模拟仿真”方式时,可将源程序中涉及到的新增特殊功能寄存器名用直接地址取代,即在程序头变量定义区内插入新增特殊功能寄存器伪定义指令,如:

AUXRDATA8EH

AUXR1DATA0A2H

IPHDATA0B7H

……

汇编后将代码直接写入目标芯片,在用户板上测试。