Quartus Ⅱ运用.docx

《Quartus Ⅱ运用.docx》由会员分享,可在线阅读,更多相关《Quartus Ⅱ运用.docx(14页珍藏版)》请在冰豆网上搜索。

QuartusⅡ运用

实验一QuartusⅡ运用

一、实验目的

学习EDA工具软件的使用。

二、实验内容

利用QuartusⅡ设计数字系统之前,应该先建立一个文件夹,此文件夹可作为QuartusⅡ默认的工作库。

QuartusⅡ中任何一项设计都是一项工程,在工程设计过程中,会产生许多仅扩展名不同的同名文件,放在同一个文件夹下,便于统一管理。

出于同样的原因,不同的设计项目最好放在不同的文件夹中。

在本例中,建立文件夹D:

\Designs作为工作库,以便将设计过程中的相关文件存储于此。

1.编辑文件

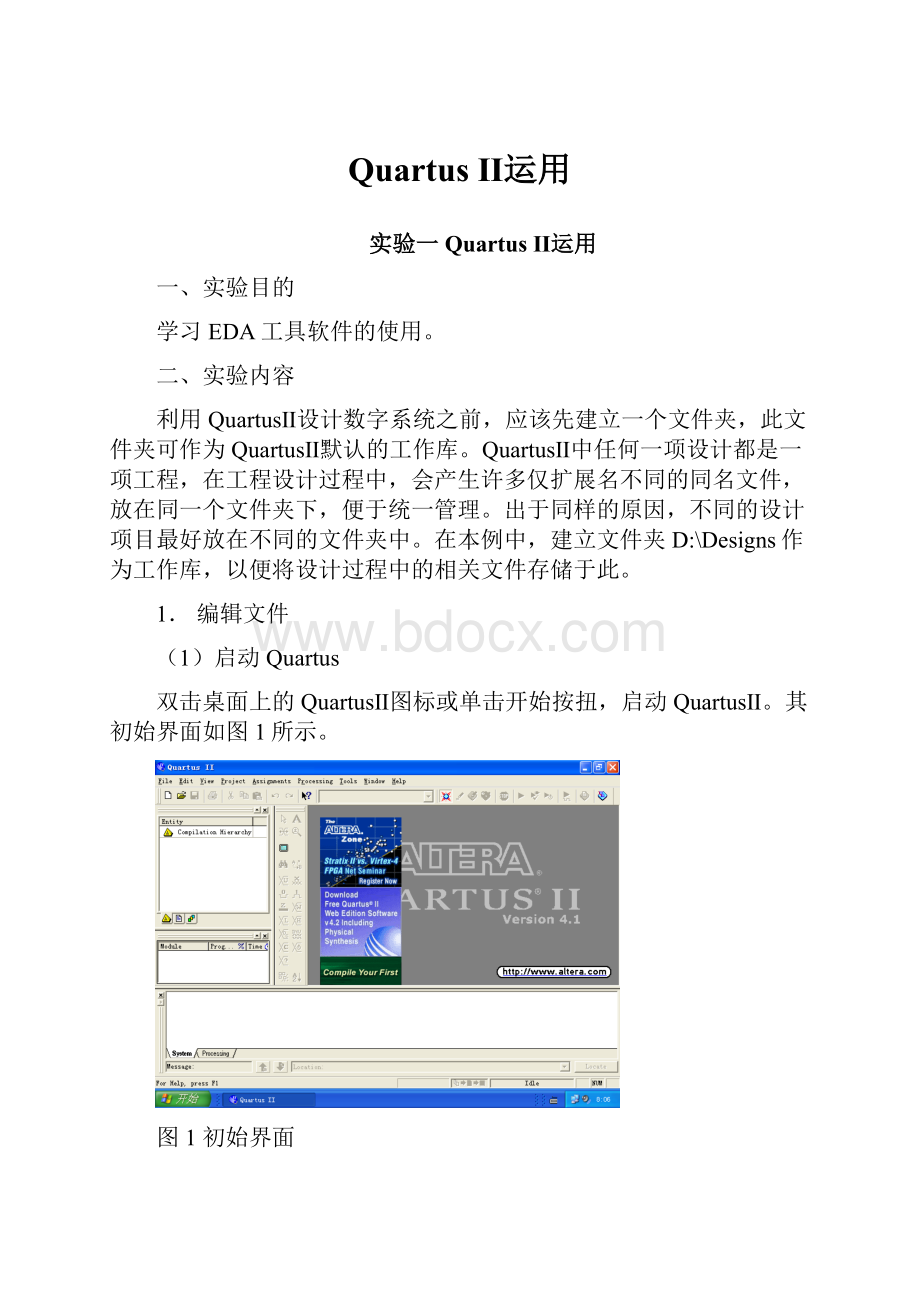

(1)启动Quartus

双击桌面上的QuartusⅡ图标或单击开始按扭,启动QuartusⅡ。

其初始界面如图1所示。

图1初始界面

(2)编辑文件

单击标题栏中的File→New对话框,如图2所示。

图2输入选择对话框

单击New对话框的DeviceDesignFiles选项卡,选择编译文件的语言类型。

这里选择VHDLFiles,选好后单击【OK】按钮,打开VHDL文本编辑器窗口,并在其中输入图3所示的程序,这是一个与门的VHDL程序。

图3文本编辑器

输入完成之后,单击File→SaveAs选项,将编辑的文本文件存在已建立的文件夹d:

\Designs下,存盘文件名应该与VHDL程序的实体名一致,即ex1_v.vhd。

当出现问句Doyouwanttocreate…时,可选“否”。

2.创建工程

(1)打开建立新工程向导

单击File→NewProjectWizard菜单,出现新建工程向导对话框,如图4所示。

图4新建工程向导

在图4中,单击【Next】按钮,出现如图5所示的工程基本设置对话框。

图5工程基本设置

在最上面的输入框中输入工作库文件夹的地址,本例的地址是D:

\Designs,或者单击该对话框最上一栏右侧的【…】按钮,出现如图6所示的对话框。

如果所见与图6不同,可单击查找范围输入框旁的下三角按钮,在下拉框中选定D:

\Designs文件夹后,单击【打开】按钮,返回图5。

(2)将设计文件加入工程中

单击图7中的【Next】按钮,在弹出的对话框中,将与本工程有关的文件加入,有两种方法:

一种是单击右边的【AddAll】按钮,将设定工程目录中的所有VHDL文件加入到工程文件栏;另一种是单击【Add…】按钮,从工程目录中选出相关的VHDL文件。

完成后,如图8所示。

图6选择文件夹目录

图5中间的输入框要求输入该工程的名称,一般可以用顶层文件的名称作为工程名称,本例的顶层文件名是ex1_v。

最下面的输入框要求输入顶层设计文件实体的名称,本例顶层文件的实体名称是ex1_v。

完成后,如图7所示。

图7新建工程基本情况

图8加入设计文件

(3)选择仿真器和综合器类型

单击图8中的【Next】按钮,这时弹出选择仿真器和综合器类型的窗口。

如果选择默认的NONE,表示使用QuartusⅡ中自带的仿真器和综合器。

在本例中都选默认的NONE选项。

如图9所示。

图9EDA工具设置

(4)选择目标芯片

单击图9中的【Next】按钮,根据系统设计的实际需要选择目标芯片。

首先在Family栏选择芯片系列,本例选择ACEX20KE系列。

在此栏下方,询问选择目标器件的方式,选No,表示允许编程器自动选择该系列中的一个器件;单击Yes选项,表示手动选择。

如图10所示。

图10器件模式

本例采用手动选择,单击图10中的【Next】按钮,选择此系列的具体芯片:

EP20K30ETC144-1,如图11所示。

图11目标器件选择

单击【Next】按钮后,弹出工程设置统计窗口,如图12所示。

图12摘要

(5)结束设置

最后单击图12中的【Finish】按钮,结束设置。

在QuartusⅡ主窗口的左侧,如图13所示。

图13工程管理窗口

该图是工程ex1_v的工程管理窗口(或称CompilationHierarchy窗口),主要显示本工程项目的层次结构和各层次的实体名。

3.目标芯片的配置

(1)选择目标芯片

单击标题栏中的Assignments→Settings菜单,在弹出的对话框中选Category下的Device选项,然后在右侧选择目标芯片EP20K30ETC144-1(此芯片已在建立工程时选定了)。

也可在Availabledevices栏分别单击Package(封装形式)、Pincount(管脚数量)和Speed(速度)来选定芯片。

如图14所示。

图14选择器件对话框

(2)选择目标器件编程配置方式

单击图14中的【Device&PinOptions…】(本例中字母D被挡住了)按钮进入器件与管脚操作对话框,首先选择Configuration项,在此框的下方有相应的说明,在此可选Configuration方式为PassiveSerial,这种方式可以直接由PC机配置,也可由专用配置器件进行配置。

使用的配置器件选Auto(系统自动配置),如图15所示。

图15配置选项卡

(3)选择输出配置

单击图15中的ProgrammingFiles选项卡,可以选Hexadecimal,即产生下载文件的同时,产生十六进制配置文件,Start(起始地址)设为0,Count(计数)设为Up(递增方式)。

如图16所示。

此文件可用于单片机与EPROM构成的FPGA配置电路系统。

图16程序文件选项卡

(4)选择目标器件闲置管脚的状态

单击图16中的UnusedPins选项卡,可根据实际需要选择目标器件空闲管脚的状态,有三种状态可供选择:

作为输入并呈高阻状态、作为输出并呈低电平状态、作为输出并呈不确定状态。

也可以对空闲管脚不作任何选择,而由编程器自动配置。

如图17所示。

图17空闲管脚设置选项卡

4.编译

(1)编译

单击标题栏中的Processing→StartCompilation选项,启动全程编译。

编译包括对设计输入的多项处理操作,其中包括排错、数据网表文件提取、逻辑综合、适配、装配文件(仿真文件与编程配置文件)生成,以及基于目标器件的工程时序分析等。

如果工程文件中有错误,在下方的信息栏中会显示出来。

可双击此条提示信息,在闪动的光标处(或附近)仔细查找,改正后存盘,再次进行编译,直到没有错误为止。

编译成功的标志是所有进程都完成,如图18所示。

图18编译进程信息

(2)阅读编译报告

编译成功后可以看到编译报告,如图19所示。

左边栏目是编译处理信息目录,右边是编译报告。

这些信息也可以在Processing菜单下的CompilationReport处见到。

图19编译报告

5.仿真

仿真就是对设计项目进行一项全面彻底的测试,以确保设计项目的功能和时序特性符合设计要求,保证最后的硬件器件的功能与原设计相吻合。

仿真可分为功能仿真和时序仿真。

功能仿真只测试设计项目的逻辑行为,而时序仿真不但测试逻辑行为,还测试器件在最差条件下的工作情况。

(1)建立波形文件

与MAX+plusⅡ仿真操作相同,仿真前必须建立波形文件。

单击File→New选项,打开文件选择窗口。

然后单击OtherFiles选项卡,选择其中的VectorWaveformFile选项。

如图20所示。

图20新文件选择

(2)打开波形编辑器

单击图20中的【OK】按钮,即出现空白的波形编辑器,如图21所示。

图21波形编辑器

为了使仿真时间设置在一个合理的时间区域上,单击Edit→EndTime选项,在弹出窗口中的Time输入框键入50,单位选us,即整个仿真域的时间设定为50微秒,如图22所示。

图22仿真时间设置

单击【OK】按钮。

结束设置后,要将波形文件存盘。

单击File→Saveas选项,将波形文件以文件名ex1_v.vwf(默认名)存入文件夹D:

\Designs中。

(3)输入信号节点

单击View→UtilityWindows→NodeFinder选项,会打开一个对话框。

在该对话框的Filter空白栏中选Pins:

all,然后点击【list】按钮。

在下方的NodesFound窗口中会出现了设计工程的所有端口管脚名,如图23所示。

图23管脚编辑

用鼠标将输入端口节点A、B和输出信号节点C逐个拖到波形编辑窗口,如图24所示。

图24波形编辑

单击图23中的关闭按钮,关闭NodeFinder窗口。

(4)编辑输入波形

波形编辑器的按钮操作方法与MAX+plusⅡ相同。

利用这些按钮,分别给输入管脚编辑波形,如图25所示。

图25已编辑输入波形

(5)启动仿真及阅读仿真报告

单击标题栏中的Processing→StartSimulation选项,即可启动仿真器。

如图26所示。

图26仿真结果

从图26中可以看出,本次设计与门的输出有着明显的延时。

单击左侧的栏目,能够打开仿真报告。

三、实验报告要求

根据实验内容,熟悉QuartusII软件的使用,将实验心得写进实验报告,并附上仿真器中所得到的A,B,C的波形图。