09325221电子可调定时器.docx

《09325221电子可调定时器.docx》由会员分享,可在线阅读,更多相关《09325221电子可调定时器.docx(17页珍藏版)》请在冰豆网上搜索。

09325221电子可调定时器

第一章主电路的设计方案

一.设计要求

(1)该电路具有定时控制电路,控制外围电路;

(2)定时时间2—2048S;(3)时间精确度小于1S;(4)自制+12V稳压直流电源。

二.设计方案

1.方案一

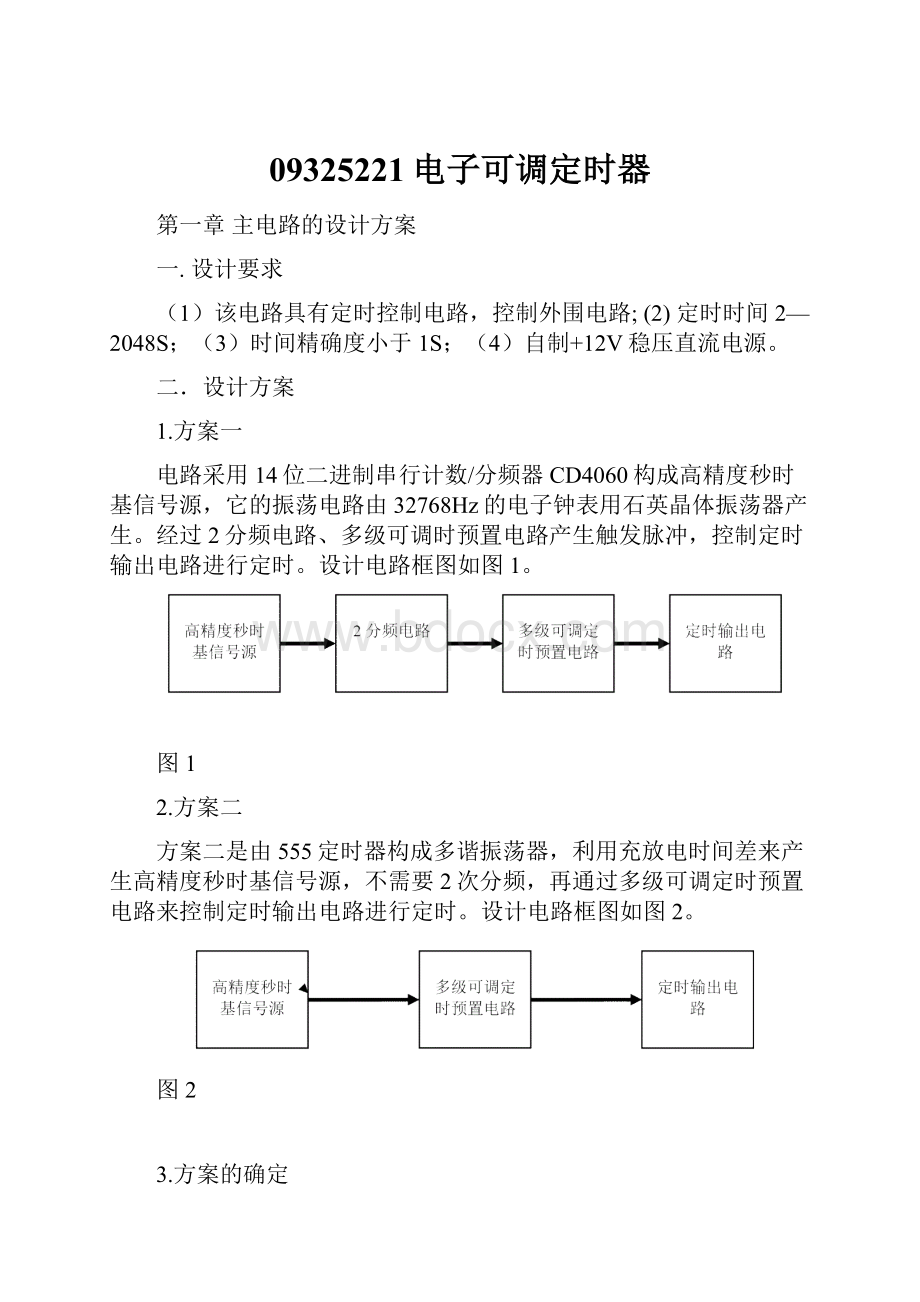

电路采用14位二进制串行计数/分频器CD4060构成高精度秒时基信号源,它的振荡电路由32768Hz的电子钟表用石英晶体振荡器产生。

经过2分频电路、多级可调时预置电路产生触发脉冲,控制定时输出电路进行定时。

设计电路框图如图1。

图1

2.方案二

方案二是由555定时器构成多谐振荡器,利用充放电时间差来产生高精度秒时基信号源,不需要2次分频,再通过多级可调定时预置电路来控制定时输出电路进行定时。

设计电路框图如图2。

图2

3.方案的确定

虽然方案二的电路结构比方案一简单,所需的元器件也比较少,但是方案一由CD4060产生的秒时基信号源比方案二由555定时器产生的秒时基信号源频率更稳定,所产生的信号源更精确,更符合任务书要求。

为使电路具有更高的Q值以提高振荡频率的稳定性,这里选择CMOS非门,从减小电路功耗的角度来考虑,这也是一种较好的选择,因此,电路的其它部分也应尽量采用CMOS集成电路来实现,方案一符合这一要求。

方案一所需的元器件实验室也可以购得,所需的元件价钱不高,因此我选用方案一。

第二章电路的工作原理

一主电路原理

本定时器是由石英晶体振荡器产生的高稳定度的脉冲信号,通过数字电路多级分频后取得1Hz的秒时基信号,再通过多级数字分频电路的分频,取得多种时间的控制信号并通过继电器控制工作电路。

本电路定时时间范围为2……2048S,通过选择开关分11级输出。

电路图如图3。

图3所示为精密数字式定时控制电路。

该控制器由高精度秒时基信号源、2分频电路、多级可调定时预置电路和定时输出电路与继电器驱动电路组成。

图3

二构成电路各硬件部分原理分析

1.高精度秒时基信号源

高精度秒时基信号源是由14位二进制串行计数/分配器CD4060、电子钟表用石英晶体振荡器(它固有频率为32768Hz)等组成。

CD4060内包含两个反相器,这两个反相器可通过外接RC元件或石英晶体组成振荡器。

本电路由石英晶体振荡器产生的32768Hz脉冲信号经CD4060内部14级二进制计数器,每个计数器可用作一个2分频,其分频范围为24--214,即16—16384。

后由③脚(Q14)输出,输出的脉冲频率为2Hz。

a.晶体振荡器电路

一般输出为方波的数字式晶体振荡器电路通常有两类,一类是用TTL门电路构成;另一类是通过CMOS非门构成的电路,如图4所示,从图上可以看出其结构非常简单。

该电路广泛使用于各种需要频率稳定及准确的数字电路,如数字钟、电子计算机、数字通信电路等。

图4

图4所示电路中,CMOS非门U1与晶体、电容和电阻构成晶体振荡器电路,U2实现整形功能,将振荡器输出的近似于正弦波的波形转换为较理想的方波。

输出反馈电阻

为非门提供偏置,使电路工作于放大区域,即非门的功能近似于一个高增益的反相放大器。

电容C1、C2与晶体构成一个谐振型网络,完成对振荡频率的控制功能,同时提供了一个180度相移,从而和非门构成一个正反馈网络,实现了振荡器的功能。

由于晶体具有较高的频率稳定性及准确性,从而保证了输出频率的稳定和准确。

晶体XTAL的频率选为32768HZ。

该元件专为数字钟电路而设计,其频率较低,有利于减少分频器级数。

从有关手册中,可查得C1、C2均为30pF。

当要求频率准确度和稳定度更高时,还可接入校正电容并采取温度补偿措施。

由于CMOS电路的输入阻抗极高,因此反馈电阻R1可选为10MΩ。

较高的反馈电阻有利于提高振荡频率的稳定性。

b.分频电路

分频电路原理

由于晶体振荡器输出频率为32768HZ,为了得到1HZ的秒信号输入,需要对振荡器的输出信号进行15级2进制分频。

CD4060在数字集成电路中可实现的分频次数最高,而且CD4060还包含振荡电路所需的非门,使用方便。

CD4060计数为14级2进制计数器,可以将32768Hz的信号分频为2Hz,其内部框图如图5所示,从图中可以看出,CD4060的时钟输入端两个串接的非门,因此可以直接实现振荡和分频的功能。

图5

综上所述,可选择CD4060同时构成振荡电路和分频电路。

在

和

之间接入振荡器外接元件可实现振荡,并利用时计数电路中多一个2分频器(后述)可实现15级2分频,即可得1Hz信号。

CD4060功能简介:

CD4060由一振荡器和14级二进制串行计数器位组成,振荡器的结构可以是RC或晶振电路。

CR为高电平时,计数器清零且振荡器使用无效,所有的计数器位均为主从触发器。

在

(和CP0)的下降沿计数器以二进制进行计数,在时钟脉冲上使用施密特触发器对时钟上升和下降时间无限制。

CD4060的功能表见表1;引脚图见图6。

引出端符号:

时钟输入端CP0时钟输出端

反相时钟输出端Q4-Q10,Q12-Q14计数器输出端

第14级计数器反相输出端

表1:

功能表

CD4060引脚图:

图6

2.二分频电路

二分频电路原理

CD4069与CD4013组成缓冲级和2分频器,由秒时基信号源输出的2Hz信号源经CD4069反相和缓冲,送入CD4013二分频,得到1Hz(秒)的信号,该信号加至CD4040的CP端,以作为时钟控制信号。

CD4013为D触发器CD4013,在本电路中被接成双稳态电路,使其每输入两个脉冲,它的输出端输出一个脉冲,实现2分频功能。

CD4013功能简介:

CD4013是一双D触发器,由两个相同的、相互独立的数据型触发器构成。

每个触发器有独立的数据、置位、复位、时钟输入和Q及Q输出,此器件可用作移位寄存器,且通过将Q输出连接到数据输入,可用作计算器和触发器。

在时钟上升沿触发时,加在D输入端的逻辑电平传送到Q输出端。

置位和复位与时钟无关,而分别由置位或复位线上的高电平完成。

CD4013的真值表见表2;引脚图见图7。

表2:

CD4013真值表功能:

CL(Note1)

D

R

S

Q

↑

0

0

0

0

1

↑

1

0

0

1

0

↓

X

0

0

Q

X

X

1

0

0

1

X

X

0

1

1

0

X

X

1

1

1

1

CD4013引脚图:

图7

CD4069功能简介:

CD4069由六个COS/MOS反相器电路组成。

此器件主要用作通用反相器、即用于不需要中功率TTL驱动和逻辑电平转换的电路中。

CD4069的引脚功能见图8、图9。

CD4069引脚功能

图8图9

交流测试电路和波形切换时间

图10图11

3.多级可调定时预置电路

多级可调定时预置电路的原理

多级可调定时预置电路由一个12位二进制计数/分配器CD4040(IC4)组成。

该电路内由12级2分频器组成,它有12个分频输出端,即Q1——Q12,其中Q1的分频系数=20=1,Q12的分频系数=211=2048。

由IC4组成的可调定时预置电路分11级,当CP信号频率为1Hz时,其中第一级的定时预置时间由CD4040的Q2输出,定时时间为21=2S,第二级定时预置时间由Q3输出,定时预置时间为22=4S,第三级由Q4输出,时间为23=8S……第十级定时预置由Q11输出,时间为210=1024S,第十一级定时预置时间由Q12输出,定时预置时间为211=2048S。

CD4040功能简介:

CD4040是12位二进制串行计数器,其内部框图如图12。

所有的计数器为主从触发器。

计数器在时钟的下降沿进行计数。

CR为高电平时,对计数器进行清零。

由于在时钟输入端使用施密特触发器,对脉冲上升和下降时间无限制,所有输入和输出均经过缓冲。

CD4040功能表见表3;引脚图见图13。

图12

引出端符号:

时钟输入端

CR清除端

Q0-Q11 计数器脉冲输出端

表3:

CD4040引脚图

图13

4.定时信号输出变换与控制电路

定时信号输出变换与控制电路工作原理

VT1、VT2和IC5组成定时信号输出变换与控制电路,其中NE555与R4、C3组成单稳态延时电路,延时时间T=1.1R4C3,也可根据实际定时需要,按照公式选择R4和C3的数值。

根据定时需要,可由选择开关SA1将相应的定时阶跃高电平引出一路。

当IC4输出定时信号后,加至放大器VT1、VT2(VT1先导通,VT2随后导通)。

VT2集电极输出低电平,经放大后的信号再加至IC5②脚,使555因②脚为低电平而发生翻转置位,③脚输出的高电平使继电器K吸合,接通相应控制的负载,使负载工作。

本控制器定时的工作程序为:

等待2N(N=2~11)秒后,继电器才吸合,接通工作。

之后,因C3通过R4进行充电,当C3上的电压充到使6脚电位达到2/3VDD时,555发生复位,③脚输出的低电平使继电器K释放,相应负载断电,停止工作。

本定时控制器的定时时间可从2~2048秒,分11个档次,定时精度高,较一般定时器理想。

NE555定时器:

555定时器是一种数字与模拟混合型的中规模集成电路,应用广泛。

外加电阻、电容等元件可以构成多谐振荡器,单稳电路,施密特触发器等。

555定时器原理图及引线排列如图14所示。

其功能见表4。

定时器内部由比较器、分压电路、RS触发器及放电三极管等组成。

分压电路由三个5K的电阻构成,分别给A1和A2提供参考电平2/3VCC和1/3VCC。

A1和A2的输出端控制RS触发器状态和放电管开关状态。

当输入信号自6脚输入大于2/3VCC时,触发器复位,3脚输出为低电平,放电管T导通;当输入信号自2脚输入并低于1/3VCC时,触发器置位,3脚输出高电平,放电管截止。

4脚是复位端,当4脚接入低电平时,则V0=0;正常工作时4接为高电平。

5脚为控制端,平时输入2/3Vcc作为比较器的参考电平,当5脚外接一个输入电压,即改变了比较器的参考电平,从而实现对输出的另一种控制。

如果不在5脚外加电压通常接0.01μF电容到地,起滤波作用,以消除外来的干扰,确保参考电平的稳定。

2触发5控制电压

3输出6门限(阈值)

4复位7放电

图14NE555内部框图(a)和引脚图(b)

表4:

NE555功能表:

在此次电路我应用的是555构成的脉冲启动式单稳态电路单稳态,因此我重点在这里说一下脉冲启动式单稳态电路。

所谓“单稳态”电路,就是该电路只有一个稳定状态,另一个状态为不稳定状态或称暂稳定状态。

这种电路在平时处于稳定状态,当需要时,用一个触发信号去触发它,使它翻转进入暂稳态,经过一段时间后电路又自动恢复到稳态。

单稳态电路有下列特点:

一是电路处于稳态时,若没有外加的触发信号,则电路一直处于稳定状态而不会自动改变其状态;二是暂稳态的暂稳时间可以根据需要预先设定;三是到达预定的暂稳时间后,电路可不外加任何信号而自动恢复到稳态。

图15为脉冲启动型单稳,也可以分为2个不同的单元。

他们的输入特点都是“RT-7.6-CT”,都是从2端输入A路的2端不带任何元件,具有最简单的形式;B路则带有一个RC微分电路。

图15

我在这里选用的是B路。

该电路在接通电源后,首先进入一个稳态建立的过程。

这个过程是这样的:

接通电源后,输出端

输出高电平。

电源首先通过电阻RT向电容CT充电,当充电使电容CT上的电压达到2/3VCC时,电路复位,输出端

变为低电平。

这时由于内部放电管导通,电容CT通过

脚进行放电,电路进入稳态。

R1、C1组成微分电路,它将输入的触发脉冲微分后加至电路的触发端

脚,使电路的触发更可靠。

当对电路的输入端Vi加上低电平后,经过微分电路,该低电平变为窄脉冲加至触发端

脚,电路被触发后发生翻转,输出端

脚由低电平变为高电平。

当电路输出端

脚变为高电平后,555电路内部的放电管截止。

电源开始通过RT向CT充电,电路进入暂稳态。

当电容充电使其电压上升至2/3VCC时,电路翻转,输出端

脚由高电平变为低电平,电路进入稳态。

第三章电源电路的制作

直流稳压电源

小功率稳压电源由电源变压器、整流电路、滤波电路和稳压电路四个部分组成,系统框图如图16所示,电路图如图17所示

+电源+整流+滤波+稳压+

u1u2u3uIU0

_变压器_电路_电路_电路_

(a)稳压电源的组成框图

u1u2u3uIU0

0t0t0t0t0t

(b)整流与稳压过程

图16

图17

1.整流和滤波电路

在稳压电源中一般用四个二极管组成桥式整流电路,整流电路的作用是将交流电压u2变换成脉动的直流电压u3。

滤波电路一般由电容组成,其作用是把脉动直流电压u3中的大部分纹波加以滤除,以得到较平滑的直流电压UI。

UI与交流电压u2的有效值U2的关系为:

在整流电路中,每只二极管所承受的最大反向电压为:

流过每只二极管的平均电流为:

其中:

R为整流滤波电路的负载电阻,它为电容C提供放电通路,放电时间常数RC应满足:

其中:

T=20ms是50Hz交流电压的周期。

全波整流电路波形如图18所示。

2、稳压电路

由于输入电压u1发生波动、负载和温度发生变化时,滤波电路输出的直流电压UI会随着变化。

因此,为了维持输出电压UI稳定不变,还需加一级稳压电路。

稳压电路的作用是当外界因素(电网电压、负载、环境温度)发生变化时,能使输出直流电压不受影响,而维持稳定的输出。

稳压电路一般采用集成稳压器和一些外围元件所组成。

采用集成稳压器设计的稳压电源具有性能稳定、结构简单等优点。

集成稳压器的类型很多,在小功率稳压电源中,普遍使用的是三端稳压器。

按输出电压类型可分为固定式和可调式,此外又可分为正电压输出或负电压输出两种类型。

常见的有CW78

(LM78

)系列三端固定式正电压输出集成稳压器;CW79

(LM79

)系列三端固定式负电压输出集成稳压器。

三端是指稳压电路只有输入、输出和接地三个接地端子。

型号中最后两位数字表示输出电压的稳定值,有5V、6V、9V、12V、18V和24V。

稳压器使用时,要求输入电压UI与输出电压Uo的电压差UI-Uo≥2V。

稳压器的静态电流Io=8mA。

当Uo=5~18V时,UI的最大值UImax=35V;当Uo=18~24V时,UI的最大值UImax=40V。

这里我选用的是12V,经测试输出的直流稳压电源为11.6V左右,符合任务要求。

图18全波整